module zuoye(CLK,CNT,RST) ;

input CLK,RST;

output [ 3 : 0 ] CNT;

reg [ 3 : 0 ] CNT;

reg [3:0] max=4'd0110;

always @ (posedge CLK or posedge RST ) begin

if (RST) begin

CNT <=4'd0;

end

else begin

if (max<=9) begin

if (CNT<max) begin

CNT<=CNT+1'd1;

end

else begin

CNT<=0;

max=max+1'd1;

end

end

else begin

max<=6;

end

end

end

endmodule

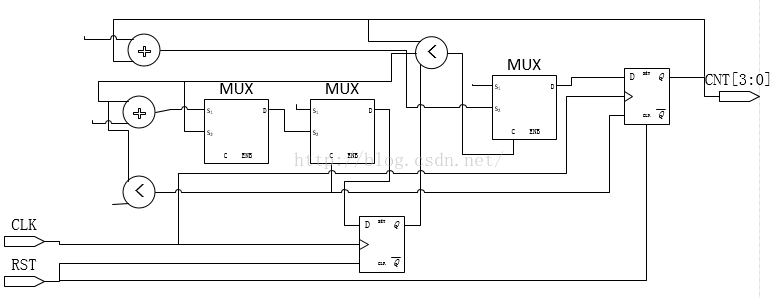

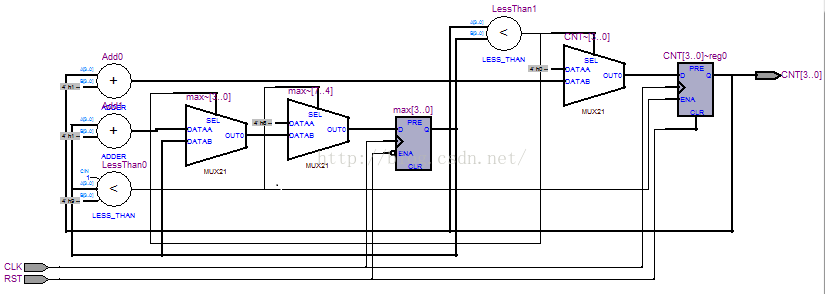

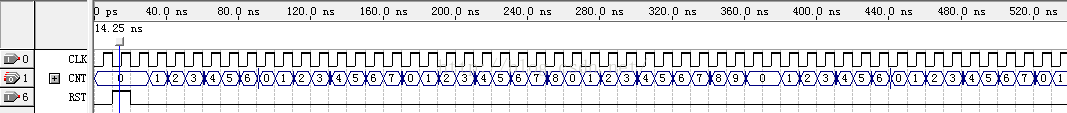

本文介绍了一个使用Verilog实现的计数器模块,该模块能够根据输入时钟信号进行递增计数,并在达到预设的最大值后重新开始计数。同时,该模块还具备复位功能。

本文介绍了一个使用Verilog实现的计数器模块,该模块能够根据输入时钟信号进行递增计数,并在达到预设的最大值后重新开始计数。同时,该模块还具备复位功能。

8093

8093