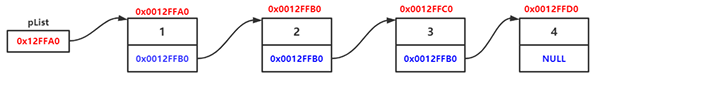

我们有学过,顺序表如何制作,还有一个与其非常相似的结构就是链表的制作,不过链表在数据中的存储不像顺序表一样是按照内存的顺序进行存储的,其在内存中是一块一块的进行存储,具体如何我们可以看看下面这张图

此链表有一个头指针pList,我们要创造的链表为不带头指针的链表,既我们创造一个结构体,其中一部分为数据部分,另外一部分为下一个数据的地址。

此链表有一个头指针pList,我们要创造的链表为不带头指针的链表,既我们创造一个结构体,其中一部分为数据部分,另外一部分为下一个数据的地址。

如何开辟内存呢?

我们知道如果我们要增加数据,我们无法像静态顺序表一样一开始就定下来最大数据量为多少,因此我们这边采用动态内存的方式进行开辟内存。还有一些具体的功能

如增删查改,具体如何实现我们可以看以下代码

SeqList.h文件

#pragma once

//单向链表,增删查改插

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <assert.h>

#define datatype int

typedef struct Single_list

{

datatype x;

struct SL* next;

}SL;

//购买一个动态内存空间

SL* buynode();

//尾插

void pushback(SL** head,datatype input);

//打印链表

void printlist(SL* head);

//头插

void pushfront(SL** head, datatype input);

//尾删

void popback(SL** head);

//头删

void popfront(SL** head);

//查找

SL* findlist(SL* head, datatype input);

//改

void modifylist(SL** head, int location, datatype input);

//插入

void insertlist(SL** head, int location, datatype input);

SeqList.c文件

#include "Slist.h"

SL* buynode()

{

SL*temp = (SL*)malloc(sizeof(SL));

if (temp == NULL)

{

perror("buynode:");

}

return temp;

}

void pushback(SL** head,datatype input)

{

SL* temp = buynode();

temp->x = input;

temp->next = NULL;

if (*head == NULL)

{

*head = temp;

}

else

{

SL* tail = *head;

while (tail->next)

{

tail = tail->next;

}

tail->next = temp;

}

}

void printlist(SL* head)

{

if (head == NULL)

{

printf("NULL");

printf("\n");

return;

}

while (head->next)

{

printf("%d --> ", head->x);

head = head->next;

}

printf("%d --> ", head->x);

printf("NULL");

printf("\n");

}

void pushfront(SL** head, datatype input)

{

if (*head == NULL)

{

SL* temp = buynode();

temp->x = input;

temp->next = NULL;

*head = temp;

}

SL* temp = buynode();

temp->x = input;

temp->next = *head;

*head = temp;

}

void popback(SL** head)

{

if (*head == NULL)

{

printf("目前没有数据填入,请输入数据后再进行删除\n");

return;

}

if ((*head)->next == NULL)

{

free(*head);

*head = NULL;

return;

}

SL* pre = NULL;

SL* tail = *head;

while (tail->next)

{

pre = tail;

tail = tail->next;

}

pre->next = NULL;

free(tail);

tail = NULL;

}

void popfront(SL** head)

{

if (*head == NULL)

{

printf("目前没有需要删除的数据,请先输入\n");

return;

}

SL* temp;

temp = (*head)->next;

free(*head);

*head = temp;

}

SL* findlist(SL* head, datatype input)

{

SL* tail = head;

while (tail->next == NULL)

{

if (tail->x == input)

{

printf("找到了\n");

return tail;

}

tail = tail->next;

}

//判断最后一个数据

if (tail->x == input)

{

printf("找到了\n");

return tail;

}

printf("没找到数据");

}

void modifylist(SL** head, int location, datatype input)

{

int count = 1;

SL* tail = *head;

while (count < location)

{

tail = tail->next;

count++;

}

tail->x = input;

}

void insertlist(SL** head, int location, datatype input)

{

SL* newnode = buynode();

newnode->x = input;

if (*head == NULL)

{

SL* temp = buynode();

temp->x = input;

temp->next = NULL;

*head = temp;

return;

}

if (location == 1)

{

newnode->next = *head;

return;

}

int count = 1;

SL* pre = NULL;

SL* tail = *head;

while (count < location)

{

pre = tail;

tail = tail->next;

count++;

}

pre->next = newnode;

newnode->next = tail;

}

Test.c文件

#include "Slist.h"

void test1()

{

SL* Singlelist = NULL;

pushback(&Singlelist, 1);

pushback(&Singlelist, 2);

pushback(&Singlelist, 3);

pushback(&Singlelist, 4);

pushfront(&Singlelist, 5);

pushfront(&Singlelist, 6);

pushfront(&Singlelist, 7);

printf("一开始:");

printlist(Singlelist);

findlist(Singlelist, 7);

popback(&Singlelist);

printf("尾删:");

printlist(Singlelist);

printf("头删:");

popfront(&Singlelist);

printlist(Singlelist);

printf("修改后:");

modifylist(&Singlelist, 3, 3);

printlist(Singlelist);

printf("插入:");

insertlist(&Singlelist, 3, 5);

printlist(Singlelist);

findlist(Singlelist, 7);

return;

}

void test2()

{

SL* Singlelist = NULL;

pushback(&Singlelist, 1);

printlist(Singlelist);

popfront(&Singlelist);

printlist(Singlelist);

}

void main()

{

test1();

}

总之单向非循环链表是一个非常简单的数据结构,读者可以自行阅读代码以及注释理解。

本文详细介绍了如何使用C语言创建不带头指针的链表,包括动态内存分配、节点结构、链表操作如头插、尾插、增删查改等,并提供了两个测试示例以展示功能应用。

本文详细介绍了如何使用C语言创建不带头指针的链表,包括动态内存分配、节点结构、链表操作如头插、尾插、增删查改等,并提供了两个测试示例以展示功能应用。

927

927

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?