上一篇博文中讲到了如何生成测试用的hex文件,本篇讲解如何进行rtl仿真

测试case试跑

上一篇博客已经说明了如何生成测试用的testcase。

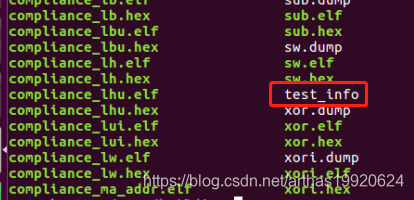

我们来分析一下生成的文件有哪些

其中hex文件是用于rtl仿真文件。dump文件用于观察生成的指令。elf文件是烧写到开发板的文件。标红的test_info是指示哪些文件用于仿真。

将Ubuntu系统的build文件拷贝至Centos系统的对应目录的对应位置,然后进入scr1目录,输入make_<simualtor>

由于本人将脚本中默认仿真工具改为了vcs,所以直接make即可

$ cd $SCR1_DIR

$ make

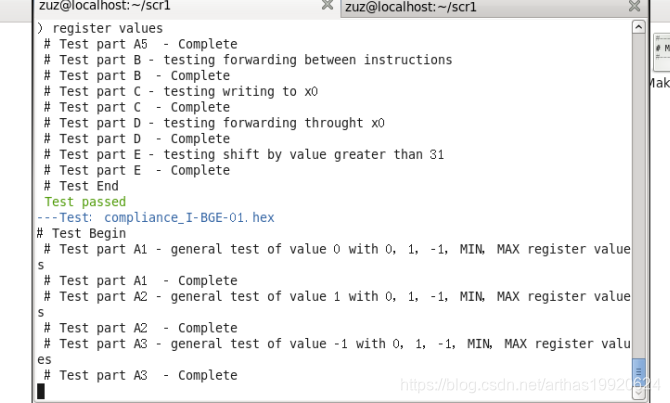

出现了test_pass即表示测试通过,如下所示

输出仿真波形

只是把case跑起来是没有用的,需要把波形dump出来才有助于分析源码。

在$(SCR1_DIR)/src/tb目录下有testbench顶层文件。我选择的总线接口类型为ahb,所以如下打开tb文件

$ cd $(SCR1_DIR)/src/tb/

$ gvim scr1_top_tb_ahb.sv

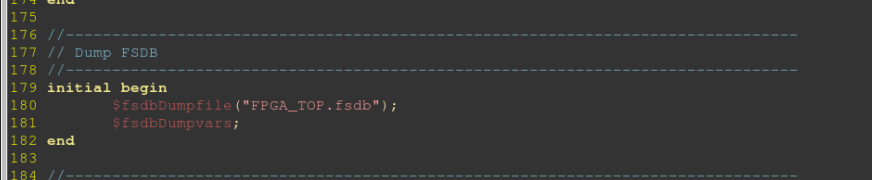

在文件中加上了这样两行语句

之后再按照1中的步骤重新跑一遍仿真,就能在 $SCR1_DIR/build目录中找到FPGA_TOP.fsdb文件,也就是波形文件。

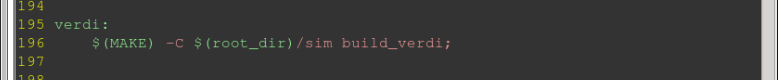

本人采用verdi进行波形的查看,在$(SCR1_DIR)目录的makefile中插入如下语句

然后在$(SCR1_DIR)/sim目录下的makefile中插入如下语句

之后在$(SCR1_DIR)目录下敲命令

$ make verdi

即可打开verdi软件查看波形。

之后在verdi的波形窗口中加载上述生成的FPGA_TOP.fsdb即可查看波形。verdi的使用方法参考其他文档,不在此赘述。

下篇博客将会讲述riscv的gnu工具链以及如何添加自定义指令集。

Syntacore RISCV 工具链使用(四)编译器与链接脚本分析

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?