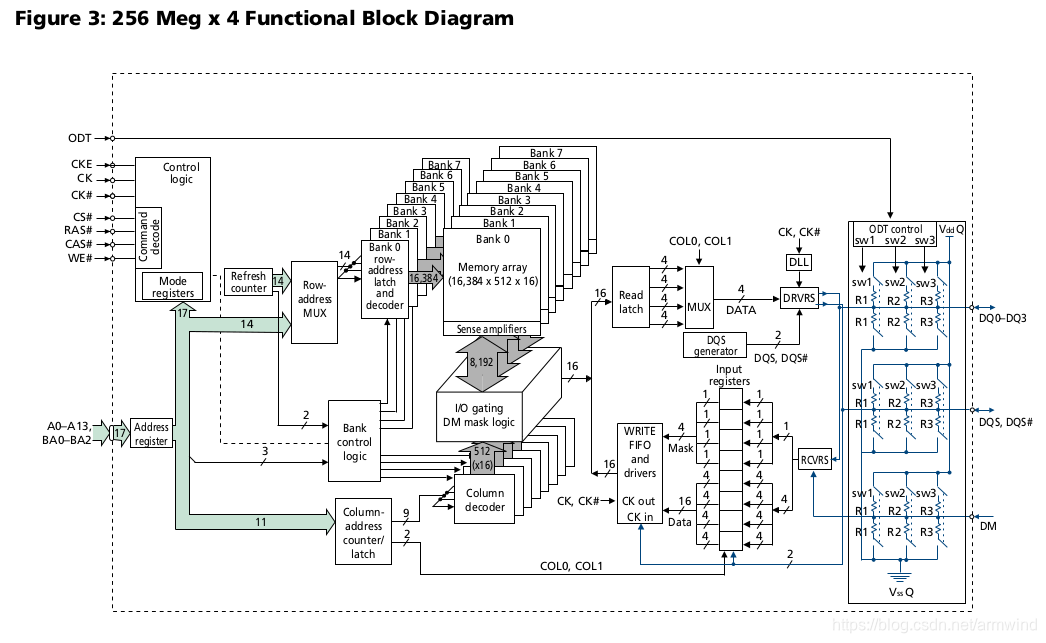

1.整体认识

从上面可以看到很多引脚

- 【1】BA[2:0]:选择bank的几个IO,这里有3个IO,可以知道最大支持8个bank。这个是由芯片的DDR控制器,根据逻辑地址计算出来的。

- 【2】CK, CK#:查分时钟输入口,为DDR2提供时钟

- 【3】CKE:(CLOCK ENABLE)时钟使能IO

- 【4】CS#:(CHIP SELECT)芯片片选信号,底有效。如果是高的情况下,屏蔽外界所有指令。

- 【5】LDM, UDM, DM:(LOW DATA MASK,UPPER DATA MASK,DATA MASK) 数据屏蔽信号,只针对写数据时有用,当DM和LDM使能时,会屏蔽底8位的数据。当DM和UDM使能时会屏蔽高八位的数据。可以说这个信号就是当有数据要写入时会触发。

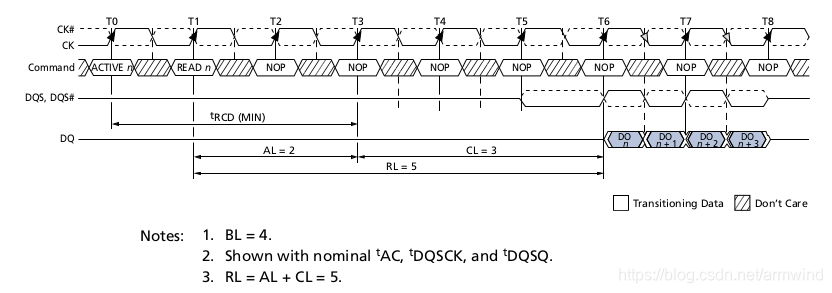

- 【6】DQS, DQS#:(DATA STROBE)是内存和内存控制器之间信号同步用的,当要读取数据时,在地址发送之后在CAS Latency时钟周期后(如下图的RL,read latency),就会输出数据,此时同步信号DQS和数据是边沿对齐的,针对当前的MT47H64M16HR 芯片有LDQS和UDQS之分,当传输底八位的时,LDQS有效,当传送高八位时UDQS有效。

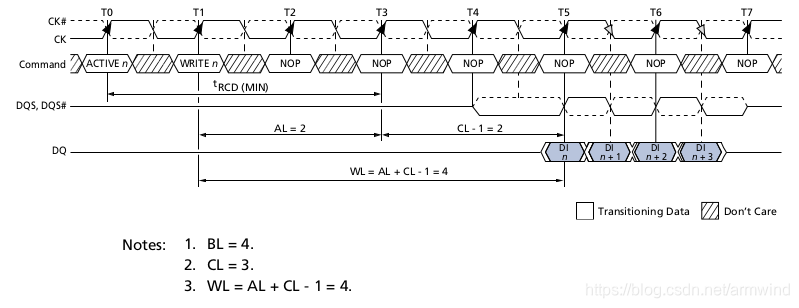

当要写入数据时,DQS是信号和数据DQ中心对齐的,这是为了数据在写入内存时,数据中央部分的可靠信号可以被内存模块截获。

这篇博客也介绍的不错(https://www.cnblogs.com/embedded-linux/p/4993069.html) - 【7】DQ[15:0]:数据输入输出接口。

- 【8】ODT:(On-die termination)端接电阻,此端口使能后,会对如下接口有作用,DQ[15:0], LDM, UDM, LDQS, LDQS#, UDQS,加入端节电阻主要是提高信号完整性。

- 【9】RAS#, CAS#, WE#:(RAW ADDRESS SELECT,COLUMN ADDRESS SELECT,WRITE ENABLE),这些常用的接口还是很好理解的。

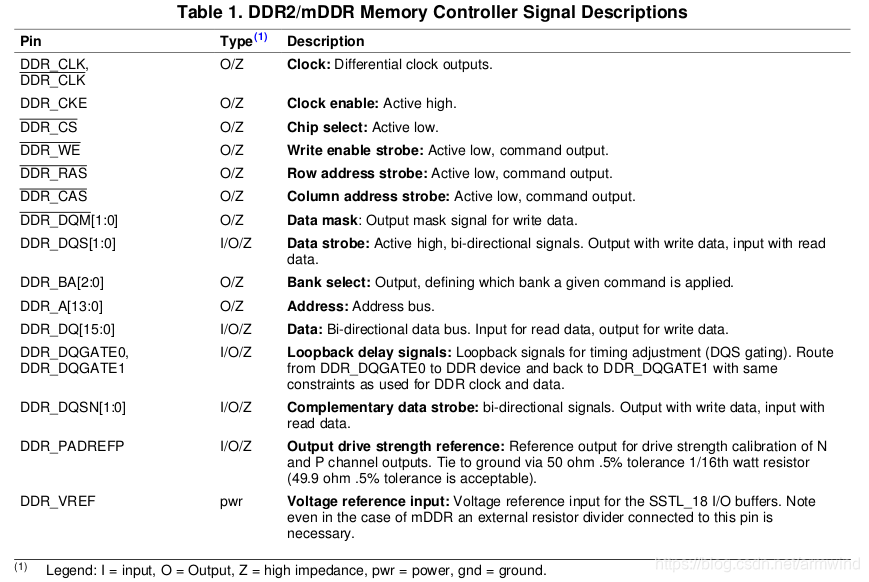

2.DM368 DDR控制器的官方介绍

如下是TMS320DM368的DDR控制器描述的接口

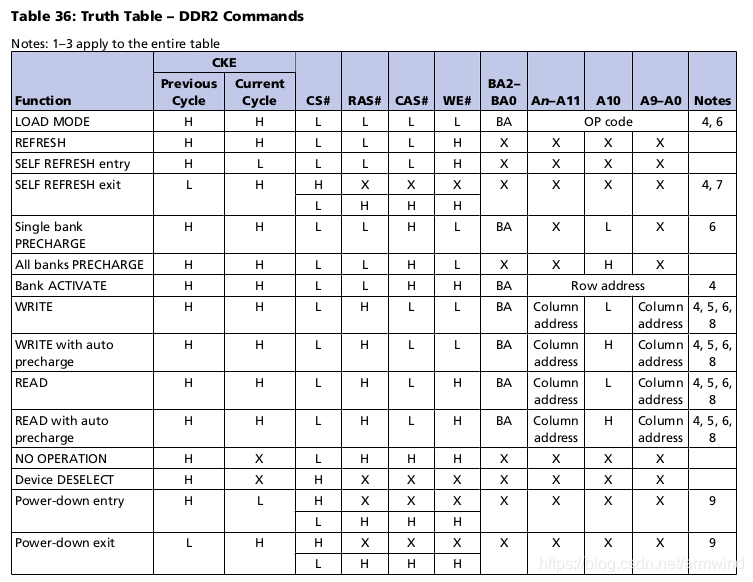

3. Command table

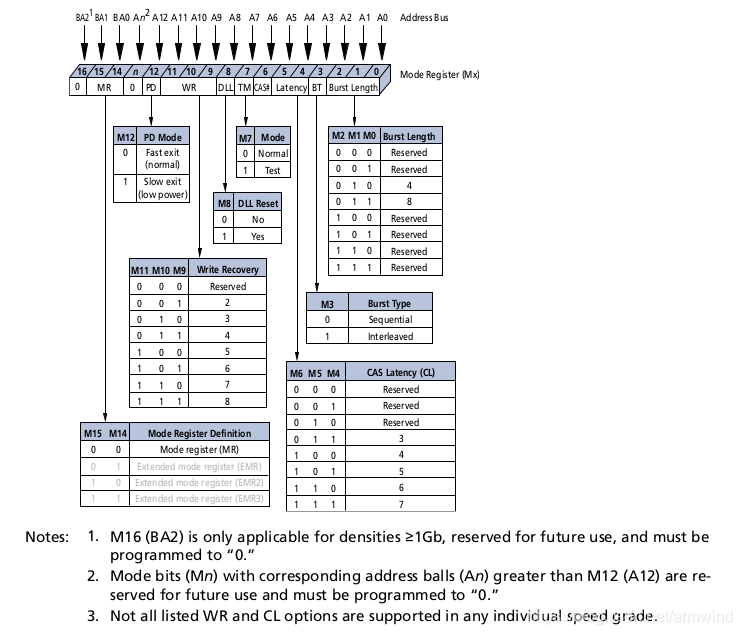

下图介绍了MT47H64M16HR芯片的操作时序,这里主要先了解一下LOAD MODE这个功能项,因为模式寄存器只有在该模式下才能写入,写入的值是BA[0,2],A[0,11]

模式寄存器会配置 burst length, burst type, CAS latency, operat-

ing mode, DLL RESET, write recovery, and power-down mode,等各种模式的值,而且内容一旦写入后就一直有效,除非重新进入LOAD MODE进行配置。

4.MODE定义

上面可以发现bank地址也用上了,其中突发模式可以配置成4,8,也就是说一次输出4bit和8bit的数据,此外CAS latency也可以配置的,在配置芯片的DDR控制器时,要注意这点。

本文深入解析DDR内存接口的各引脚功能,包括时钟输入、数据屏蔽、数据同步等关键信号,以及DM368 DDR控制器特性。阐述了模式寄存器的配置方法及其对突发长度、突发类型等参数的影响。

本文深入解析DDR内存接口的各引脚功能,包括时钟输入、数据屏蔽、数据同步等关键信号,以及DM368 DDR控制器特性。阐述了模式寄存器的配置方法及其对突发长度、突发类型等参数的影响。

1703

1703

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?