目标:

1-能独立分析时钟树框图,解释信号路径(如HSE→PLL→SYSCLK→AHB→APB1→UART);

2-灵活配置时钟:根据需求选择最佳时钟源,计算分频系数以满足外设频率约束;

3-解决时钟相关问题:

(1)诊断外设不工作的原因(未开启时钟或总线频率超限)

(2)优化功耗:关闭未用外设时钟,切换低速模式

4-彻底理解关键寄存器:

(1)RCC_CR(时钟控制)

(2)RCC_CFGR(分频配置)

(3)RCC_AHB/APBENR(外设时钟使能)

一、时钟树

1-时钟树的本质

时钟树是微控制器的“脉搏系统”,负责将时钟信号从源头分配到所有外设和内核,确保各模

块同步工作。

理解:跟电力系统一样

电源 -》变压器 -》配电盘 -》电器

时钟源 -》分频/倍频器 -》分配网络 -》外设

2-为何需要时钟源与分频

功耗与性能平衡:高速外设(如USB、以太网)需高频时钟、低速外设(如RTC、看门狗)只需

低频时钟,独立控制可以降低功耗。

稳定性:外部晶振(HSE/LSE)精度高但成本高,内部振荡器(HSI/LSI)成本低但精度

低,需按场景选择。

3-时钟分配路径

SYSCLK(系统时钟):可选HSI、HSE或PLL输出(通常选PLL以获得最高频率)

总线时钟分配:

AHB总线 → HCLK(最高216 MHz,供内存、DMA)

APB1总线 → PCLK1(最高54 MHz,低速外设如I2C、UART)

APB2总线 → PCLK2(最高108 MHz,高速外设如SPI、TIM1)

二、时钟源详解(五大核心源)

| 时钟源 | 频率 | 特点 | 典型应用 |

| HSE | 4-26MHZ(常用25MHZ) | 高精度、外部晶振 |

系统时钟/PLL输入 |

| HSI | 16MHZ | 低成本、快速启动 | HSE故障时的备份时钟 |

| LSE | 32.768kHZ | 高精度、低功耗 | RTC实时时钟 |

| LSI | 32kHz | 低精度、内置RC振荡器 | 看门狗、低功耗定时器 |

| PLL | 输出可达216MHz | 锁相环倍频、核心高频来源 | 系统时钟(SYSCLK)、USB/SDIO时钟 |

三、通过STM32CubeMX配置时钟树

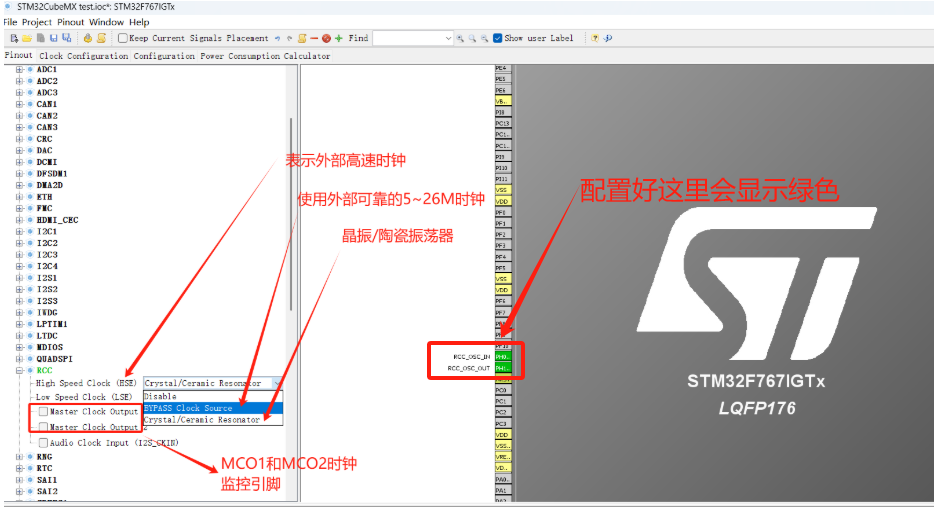

1-配置RCC时钟源

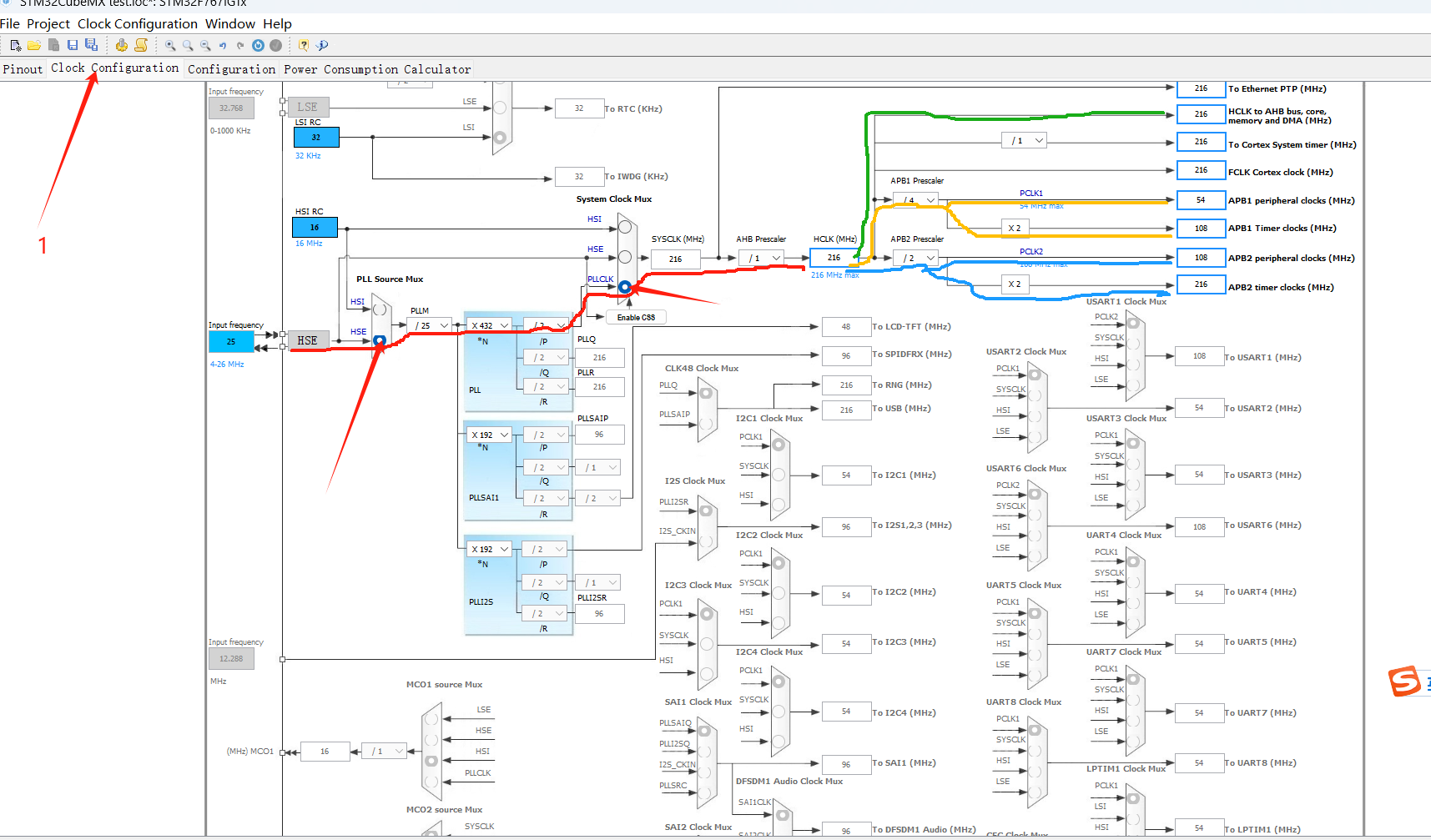

2-配置时钟源、时钟分频因子和倍频因子

2477

2477

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?