从外部世界进入我们同步电路的输入信号通常与时钟不同步;它们是异步的。输入信号可以来自不具有从0到1或从1到0的干净转变的源。一个示例是弹跳按钮或开关。输入信号可能带有尖峰噪声,可能会触发同步电路中的转换。

本章介绍处理此类输入条件的电路。后两个问题(去抖动开关和噪声滤波)也可以通过外部模拟元件解决。然而,在数字域中处理这些问题更具(成本)效率。

异步输入

与系统时钟不同步的输入信号称为异步信号。这些信号可能违反触发器输入的建立和保持时间。这种违反可能导致触发器的亚稳定性。亚稳态可能导致0和1之间的输出值,或者可能导致振荡。然而,在一段时间之后,触发器将稳定在0或1。

外部异步输入信号的另一个常见问题是,当该信号在接近时钟上升端时发生变化,并且在电路的多个位置使用时。由于延迟时间不同,输入的不同用法可能会在不同的时钟周期记录,这可能会违反某些假设。

外部异步输入信号的另一个常见问题是,当该信号在接近时钟上升端时发生变化,并且在电路的多个位置使用时。由于延迟时间不同,输入的不同用法可能会在不同的时钟周期记录,这可能会违反某些假设。

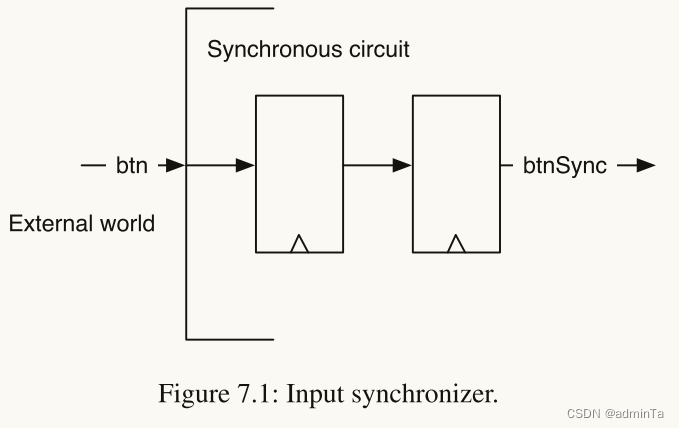

图7.1显示了外部世界和同步电路之间的边界。输入同步器由两个触发器组成。输入同步器的Chisel代码是一个单行程序,它实例化了两个寄存器。

val btnSync = RegNext(RegNext(bin))

消除抖动

开关和按钮可能需要一些时间在打开和关闭之间转换。在转换期间,开关可以在这两个状态之间弹跳。如果不进一步处理这样的信号,这可能会检测到比预期更多的转换。一个解决方案是使用时间来过滤这种抖动。假设,最长抖动时间为tbouncet_{bounce}tbounce,我们将以周期为T>tbounceT>t_{bounce}T>tbounce对输入信号进行采样。

当以这个长周期对输入进行采样时,我们知道在从0到1的转变时,只有一个样本可能落入弹跳区域。之前的样本将安全地读取0,并且反弹区域之后的样本将安全地读取1。反弹区域中的样本将为0或1。然而,这并不重要,因为它然后属于仍然0个样本或已经1个样本。

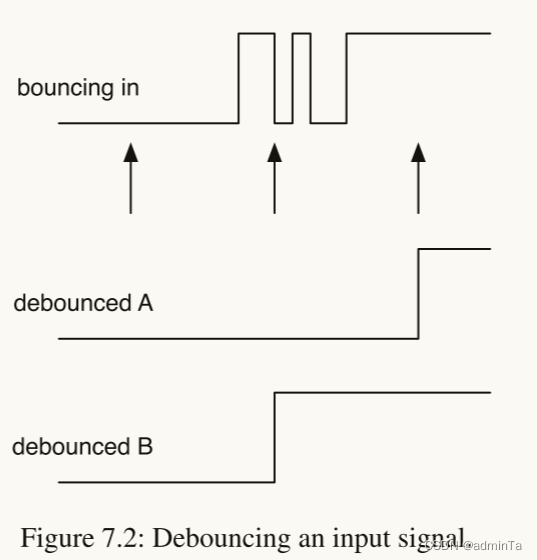

图7.2显示了去抖动的采样情况。顶部的信号显示了跳动输入,下面的箭头显示了采样点。这些采样点之间的距离需要长于最大反弹时间。第一个样本安全地采样0,图中的最后一个样本采样1。中间的样品福尔斯弹跳时间。它可以是0或1。两个可能的结果被示出为去抖动A和去抖动B。两者都具有从0到1的单个转换。这两个结果之间的唯一区别是版本A中的过渡是一个样本周期之后。然而,这通常不是问题。

用于去抖动的Chisel代码比同步器的代码更先进一点。我们使用一个计数器生成采样定时,该计数器提供单周期滴答信号,如我们在第6.2.2节中所做的那样。

val btnDebReg = Reg(Bool())

val cntReg = RegInit(0.U(32.W))

val tick = cntReg === (fac-1).U

cntReg := cntReg + 1.U

when (tick) {

cntReg := 0.U

btnDebReg := btnSync

}

首先,我们需要确定采样频率。上述示例假设时钟为100 MHz,采样频率为100 Hz(假设反弹时间低于10 ms)。最大计数器值是fac,即分频因子。我们为去抖动信号定义寄存器btnDebReg,没有复位值。寄存器cntReg用作计数器,当计数器达到最大值时,滴答信号为真。在这种情况下,when条件为真,并且(1)计数器复位为0,以及(2)去抖动寄存器存储输入样本。在我们的示例中,输入信号被命名为btnSync,因为它是上一节所示输入同步器的输出。

去抖动电路在同步器电路之后。首先,我们需要在异步信号中进行同步,然后我们可以在数字域中进一步处理它。

输入信号的滤波

有时我们的输入信号可能有噪声,可能包含我们可能无意中使用输入同步器和去抖动单元采样的尖峰。过滤那些输入尖峰的一个选项是使用多数表决电路。在最简单的情况下,我们取三个样本并执行多数投票。我们对采样信号执行多数表决。多数表决可确保信号稳定时间长于采样周期。

图7.3显示了多数表决器的电路。它由一个3位移位寄存器组成,由我们用于去抖动采样的滴答信号使能。三个寄存器的输出被馈送到多数表决电路。多数表决功能过滤任何短于采样周期的信号变化。

文章讨论了在同步电路中处理异步输入的问题,包括输入信号的抖动和噪声。介绍了去抖动技术,通过设定采样周期大于最大反弹时间来消除开关或按钮的弹跳。此外,还提到了噪声滤波,可以使用多数表决电路来过滤短期变化的信号。文章强调了在数字域内处理这些问题的效率和优势。

文章讨论了在同步电路中处理异步输入的问题,包括输入信号的抖动和噪声。介绍了去抖动技术,通过设定采样周期大于最大反弹时间来消除开关或按钮的弹跳。此外,还提到了噪声滤波,可以使用多数表决电路来过滤短期变化的信号。文章强调了在数字域内处理这些问题的效率和优势。

767

767

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?