为了更直观学习riscv-sodor-rv32-1stage的代码,我直接用它们自带的仿真进行分析。

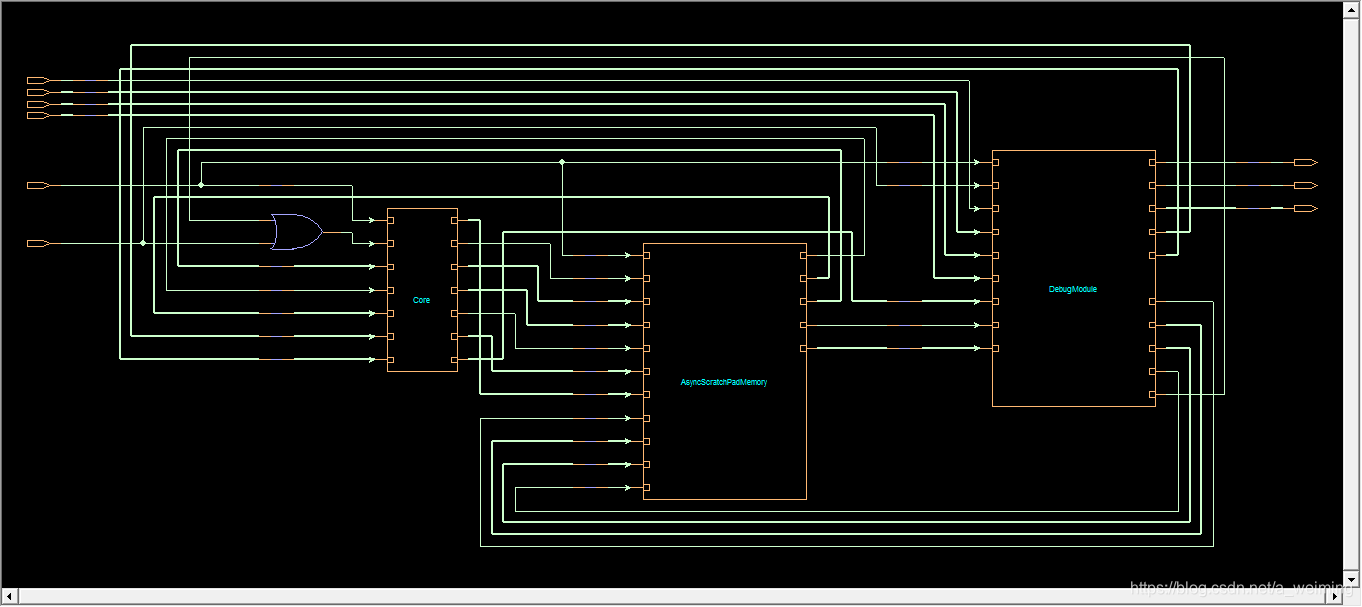

首先看得是riscv-sodor-rv32-1stage的整体框图:

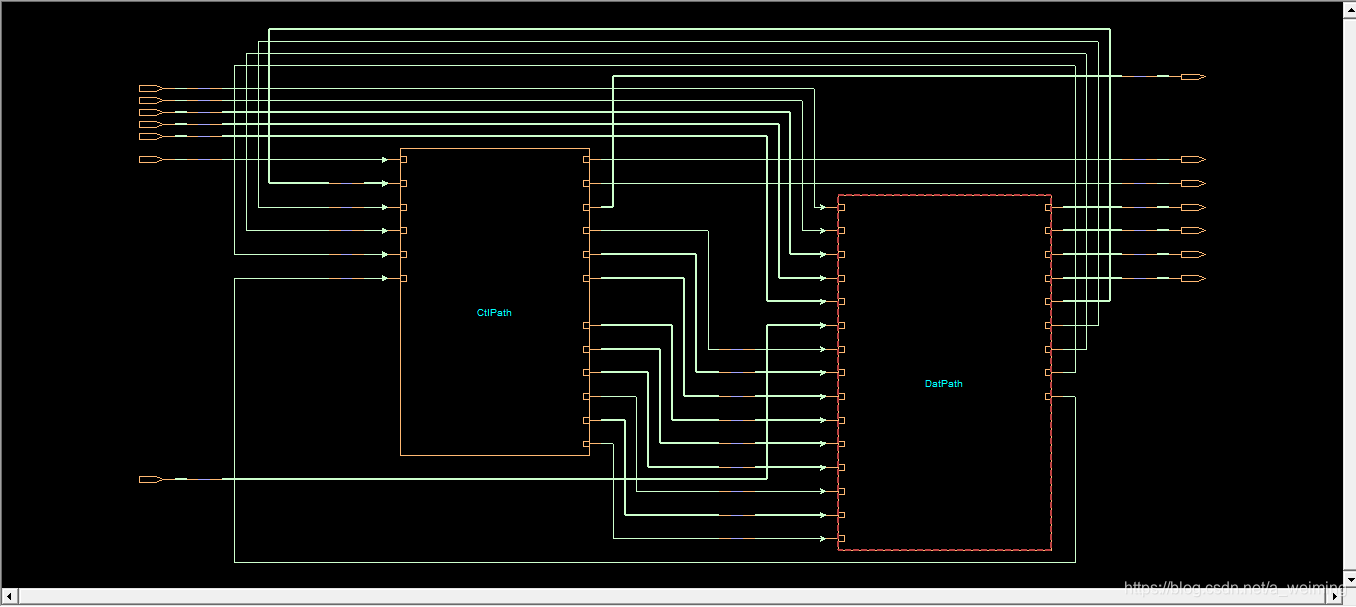

然后看的是core层次的框图:

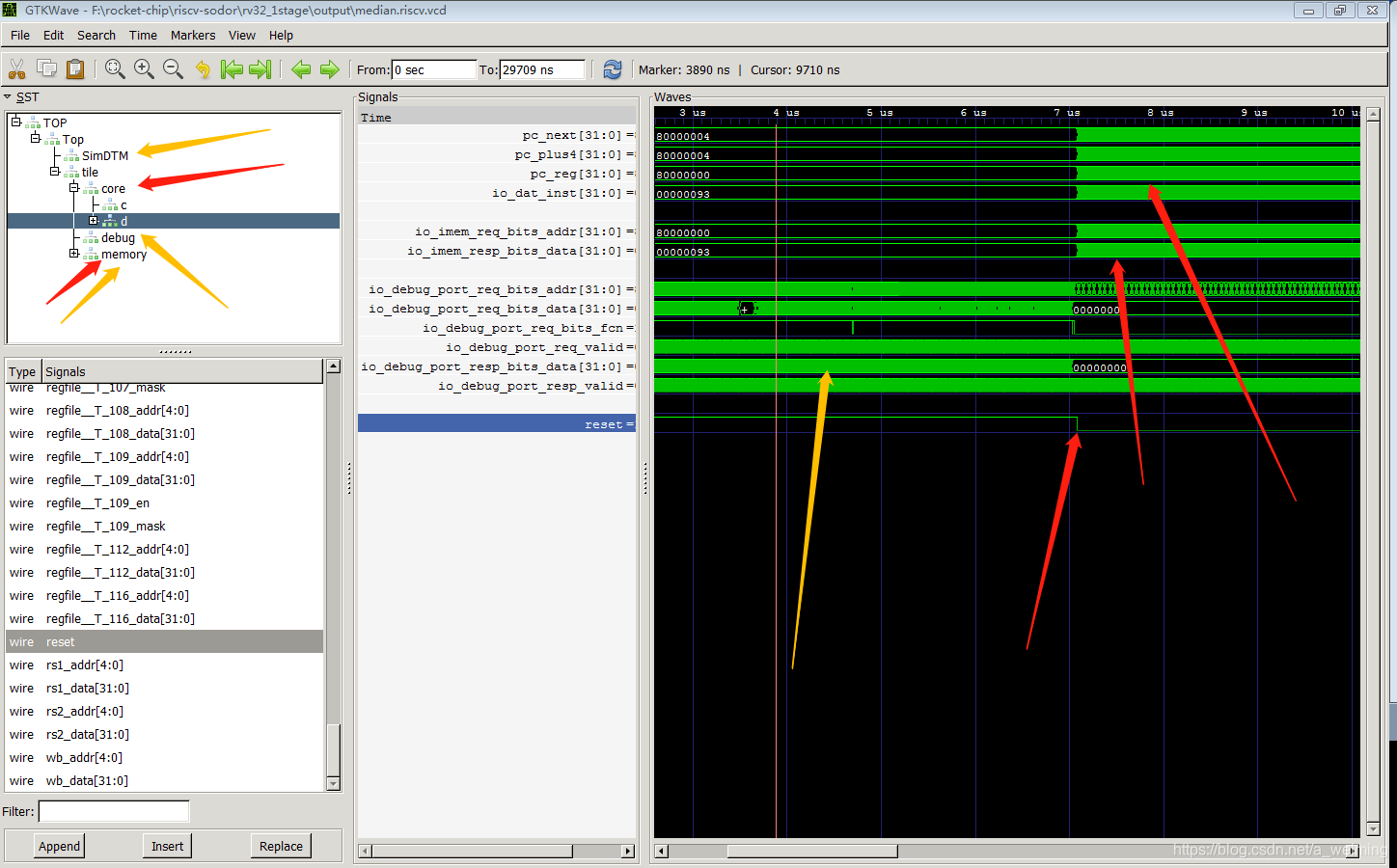

接下来我们以它们自带的memdian例子来说明riscv-sodor-rv32-1stage是如何运作的。先看下面的图:

我们先看黄色箭头,黄色箭头是什么意思呢?

第一个黄色箭头指的是SimDTM,它是一个仿真模块,模拟我们将代码download到memory的过程。所以实际上SimDTM–>debug–>memory就是我们的下载代码过程,这部分涉及RISCV-DEBUG协议的说明,暂时不展开说明。右边黄色箭头就是它们download的过程。

可以看到在download过程中,reset是一直拉高的,所以我们的core是一直被复位的,只有完成download了,才被释放出来。

红色箭头就是core运行的情况,实际上是core–>memory的运行过程。io_mem_*端口是core向memory请求执行指令的数据,而pc_*就是core里面pc的变化情况,还有in_data_inst就是当前执行的指令。

我们再放大一下波形:

本文详细分析了RISC-V Sodor RV32 1Stage处理器的运行机制,从整体框图到核心模块,再到代码下载与执行流程。通过波形图解释了SimDTM仿真模块如何模拟代码下载至内存,以及reset信号在下载过程中的作用。深入探讨了core与memory交互的细节,包括io_mem_*端口和pc变化情况,揭示了同步取指令的过程。

本文详细分析了RISC-V Sodor RV32 1Stage处理器的运行机制,从整体框图到核心模块,再到代码下载与执行流程。通过波形图解释了SimDTM仿真模块如何模拟代码下载至内存,以及reset信号在下载过程中的作用。深入探讨了core与memory交互的细节,包括io_mem_*端口和pc变化情况,揭示了同步取指令的过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2272

2272