1.阻塞赋值(使用 = )

理解为程序语言(如C语言)的顺序执行,“语句1”执行完毕之后才能执行“语句2”(执行“语句1”时,对于“语句2”谓之“阻塞”)。举例:

module Trigger(

input in,

input clk,

output reg out_a,

output reg out_b

);

always @(posedge clk)

begin

out_a = in; // 语句1

out_b = out_a; // 语句2

end

endmodule

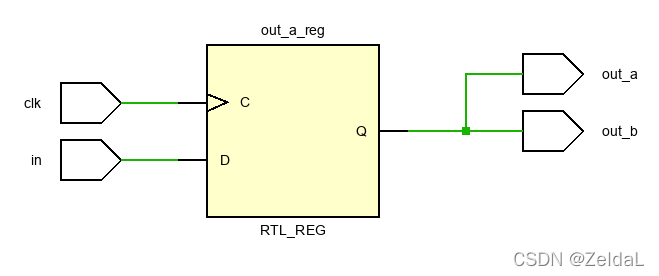

RTL图如下:

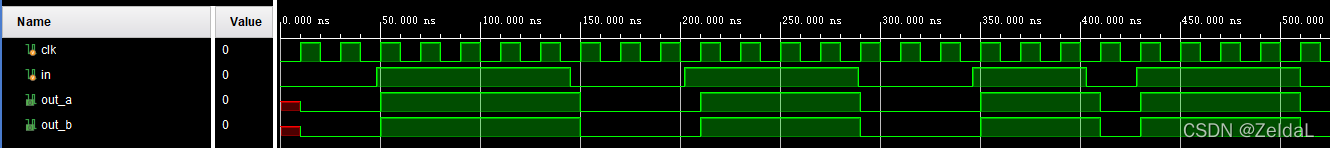

仿真结果表明,两个输出随上升沿的到来同时变化(其实就是同一个输出):

2.非阻塞赋值(使用 <= )

可理解为并行执行,但并不立即赋值(out_a和out_b不立即被in和out_a所更新)。在“<=”右边计算完、整个块结束时,才更新“<=”左边进行赋值。

如下代码,若in

本文详细介绍了Verilog编程中的阻塞赋值(使用 =)和非阻塞赋值(使用 <=)的区别。通过示例代码和仿真结果,展示了阻塞赋值导致的顺序执行特性,以及非阻塞赋值在并行执行中的延迟更新行为,帮助理解这两种赋值方式在FPGA开发中的应用。

本文详细介绍了Verilog编程中的阻塞赋值(使用 =)和非阻塞赋值(使用 <=)的区别。通过示例代码和仿真结果,展示了阻塞赋值导致的顺序执行特性,以及非阻塞赋值在并行执行中的延迟更新行为,帮助理解这两种赋值方式在FPGA开发中的应用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2383

2383

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?