ASPLOS’20

Reliable Timekeeping for Intermittent Computing

Authors:

Jasper de Winkel, Carlo Delle Donne, Kasım Sinan Yıldırım

Delft University of Technology Delft, The Netherlands

ABSTRACT:

Energy-harvesting devices have enabled Internet of Things applications that were impossible before. One core challenge of batteryless sensors that operate intermittently is reliable timekeeping. State-of-the-art low-power real-time clocks suffer from long start-up times (order of seconds) and have low timekeeping granularity (tens of milliseconds at best), often not matching timing requirements of devices that experience numerous power outages per second. Our key insight is that time can be inferred by measuring alternative physical phenomena, like the discharge of a simple 𝑅𝐶 circuit, and that timekeeping energy cost and accuracy can be modulated depending on the run-time requirements. We achieve these goals with a multi-tier timekeeping architecture, named Cascaded Hierarchical Remanence Timekeeper (CHRT), featuring an array of different 𝑅𝐶 circuits to be used for dynamic timekeeping requirements. The CHRT and its accompanying software interface are embedded into a fresh batteryless wireless sensing platform, called Botoks, capable of tracking time across power failures. Low start-up time (max 5 ms), high resolution (up to 1 ms) and run-time reconfigurability are the key features of our timekeeping platform. We developed two time-sensitive batteryless applications to demonstrate the approach: a bicycle analytics tool—where the CHRT is used to track time between revolutions of a bicycle wheel, and wireless communication—where the CHRT enables radio synchronization between two intermittently-powered sensors.

项目背景:

在能量收集架构中,计算、通信和驱动很可能是间歇性的。在这种情况下,电源故障成为经常发生,需要高效且优雅地从终端中进行恢复,确保能量收集设备能在频繁的电源故障中持续运行并保持数据一致性。我们之前介绍了先前的工作试图通过使用检查点对程序进行检测或使用基于任务的编程模型重写应用程序等软件方法来减轻间歇性操作的缺点。但是即便如此,今天的间歇性设备在部署方面仍存在挑战,跟踪时间的能力是许多计算和网络原语(如同步和网络、数据收集和实时操作)的基础,而频繁终端的间歇性设备不具备稳健的计时能力。

挑战:

嵌入式系统开发离不开对准确、连续时间概念的获取,超时和时间戳构成了嵌入式应用程序的支柱,特别是那些针对传感、通信和驱动的应用程序。超低功耗无电池设备的间歇性运行使得芯片上的数字计时器在停电期间处于不可用的状态,无法跟踪时间。即使是专用的超低功耗实时时钟,也需要很长的启动时间和每次停电后的高初始能量沉积,不适合间歇性操作。另一方面,为了覆盖可能遇到的最长的停机时间,实时时钟和其他嵌入式系统计时标准在提供能量方面十分保守。计时器的能量缓冲器(通常是其内部电容)总是被过度配置,以测量预期的最长停机时间,这浪费了能量来维持大的能量缓冲。

| RTC Model | Resol. | Start-up time | Nominal Worst | Current draw |

|---|---|---|---|---|

| NXP PCF85263A | 10 ms | 200 ms | 2s | 320 nA |

| Abracon AB18X5 | 10 ms | 900 ms | 21.5 s | 55 nA |

| ST M41T62 | 10 ms | <1000 ms | 1 s | 350 nA |

| Maxim DS139X | 10 ms | <1000 ms | N/A | 500 nA |

目前的低功耗计时解决方案并不适合间歇性运行,要么它们不是为快速重启和短时间执行而设计的(如实时时钟),要么它们依赖于来自外部基础设施或环境的信号(如基于光或射频的同步架构)。实时时钟(rtc)的时间间隔很少低于秒,并且冷启动时间过长(如果电源故障,一些低功耗型号需要数十秒,如表1所示),这对于电池供电设备而言是可以接受的,因为其电源故障很少。

贡献:

该工作提出了一种硬件和软件内核支持,能够抵御无电池设备间歇性运行所导致的反复电源故障,并适应间歇性计算的动态约束,从而实现连续计时功能。在硬件层面采用剩磁计时器的设计灵感,实现在设备耗尽能量时也可以跟踪时间;软件层对剩磁计时器进行抽象,并使它们可以在任何现有或未来的运行时中用于间歇性供电的传感器节点。

剩磁计时器的工作原理是,在执行和关闭期间,在一个大电阻上放电一个小电容器,并在电源返回时测量电压,以估计两次重新启动之间经过的时间。然而,随着测量时间的增加,剩磁计时器的分辨率降低(由于RC电路的指数能量衰减),使得设计具有毫秒分辨率和多秒寿命的计时器变得困难。我们的观察是,将这些不同尺寸的廉价RC电路级联在一起,分层排列,可以产生高分辨率和长计时范围。我们将这种具有低能耗,低冷启动时间和小面积特性的计时架构称为级联分层剩磁计时器(Cascaded Hierarchical Remanence Timekeeper,CHRT)。

剩磁计数器在工作Mayfly1在间歇性运行、无基础设施的本地计时中被引入,本质上是通过电阻(RC电路)放电的电容器。在设备重新启动时,对电容器的电压电平进行采样,以获得设备关闭电源时已经过的时间的估计。

具体在使用剩磁计数器时,需要对应用程序的计时需求、分辨率和可用能量之间进行复杂的权衡,主要通过调整剩磁计数器的电容和电阻器参数来控制。例如,在相同尺寸的电阻器上,较大的电容器需要更长的放电时间,这意味着可以计时更长的断电时间。然而,每次重新启动时,为较大的电容器充电需要更多的能量和更多的充电时间,并且降低了测量的分辨率,因为与较小的电容器相比,放电曲线不太陡峭。

因此,找到一种可以满足应用程序不同需求的配置,在设计时平衡和预测所有这些权衡是非常困难的。

除此之外,作者还注意到,剩磁计数器在计时刚度方面也存在挑战。经过调优,单个剩磁计数器的停机长度是固定的,这不适用具有时变计时需求的应用程序。例如同步无线电通讯传输需要毫秒级的计时,而一次湿度采样任务需要几分钟甚至几小时。在这种情况下,一个以毫秒为单位的、高精度的时间中断的单个剩余计时器不能给出任何以分钟为单位的时间流逝的概念。可以说,静态剩磁计时器过于死板,无法发挥作用。

当然,剩磁计数器具有很高的成本、大小和复杂性优势。首先,剩磁计数器电路结构简单,可以以超小的尺寸和成本应用。如果内置在现代CMOS工艺中,上述成本消耗更小。

系统总览:

鉴于上述间歇性运行设备的挑战与单个剩磁计数器和rtc的缺点,本工作提出了一种将多个电容增加的剩磁计数器连接在一起。耗尽层自动激活下一个最小层。对于较短的时间间隔,较小的层提供更高的分辨率,消耗更少的能量。

级联分层的设计相比单层设计有着诸多优势。首先,CHRT不会因放电曲线变平而导致分辨率下降,这意味着在长时间停机后仍然可以利用高分辨率。其次,CHRT的启动时间与能量相比RTC小很多,其启动时间仅受电容器大小的限制。最后,为了保证在最差情况下也能实现对断电时间的准确估计,rtc和单个剩余计时器都设计了一定容量的电容器并且浪费了很多能量为其充能。CHRT可以在运行时进行配置,以便使用可以计算下一次中断的可能长度的最小层。

CHRT:

在CHRT的设计中,其各个层可用于最小化冷启动时间和能耗,并最大化运行时的分辨率和计时范围。这些层从最小到最大连接在一起,因此耗尽的层可以自动激活下一层,从而增加总时间范围,同时保持最佳分辨率。根据剩磁计数器原理可知,在较短的时间间隔内,较小的层提供更高的分辨率并消耗更少的能量;较大的层用于间隔较长的时间,但分辨率较低,需要更多的充电能量。为了最小化能耗,会根据应用程序的需求和环境的能源可用性预期来配置硬件抽象层,预先指定每次重新启动时应该为那些层充能。

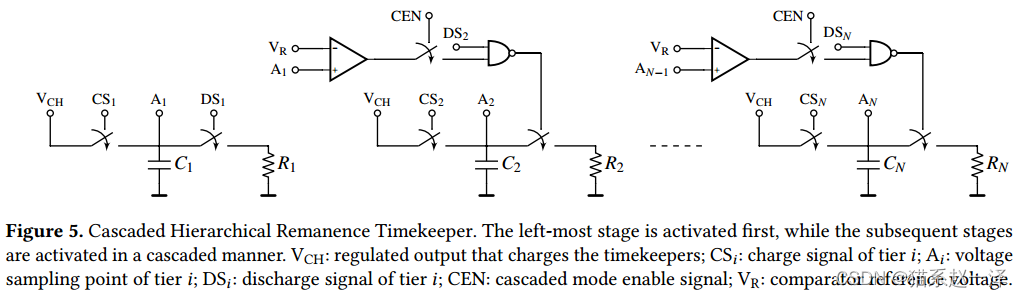

上图为CHRT前两层和最后一层的电路图,其中 V C H V_{CH} VCH是由超低功耗稳压器提供的;开关允许MCU控制这电阻的充电和放电;比较器用于触发级联的各个阶段,当前一层电压低于比较器的参考电压 V R V_R VR时,CHRT将会被激活。CEN控制信号可以绕过级联行为,将任何层设定为一个独立的计时器。使用独立层,程序员可以根据所需的时间粒度将层映射到特定的功能。

CHRT层数量及其大小的判定,需要根据所执行应用程序提取出的计时需求来确定。如果数据在收集10秒后就没有用了,那么就没有理由使用一个可以捕获超过10秒的时间段的计时器。嵌入式系统的应用程序代码通常充满了嵌入到程序中的时序需求。除了应用程序信息之外,还可以从对环境的预测中提取此类需求。对于能量特别稀少的环境,可能需要更大的层来维持中断。

一旦提取了时间需求(例如,数据的过期时间、通信的同步粒度),就可以通过检查所需的总范围和粒度来决定层的数量及其大小。由于每一层只能覆盖最终计时范围的一部分,我们可以使用简单的RC计算来找到这些范围。假设任务所需的分辨率为 δ t \delta_t δt,采用的ADC为为N-bit,电阻和电容分别表示为R和C,电容在校正和使用时被充电至 V 0 V_0 V0。为了推导出最大时间间隔 △ t m a x \bigtriangleup t^{max} △tmax,此外,设置自变量 △ t x \bigtriangleup t_x △tx和 △ t y \bigtriangleup t_y △ty分别满足 △ t x < △ t m a x \bigtriangleup t_x<\bigtriangleup t^{max} △tx<△tmax且 △ t y = △ t x + δ t ≤ △ t m a x \bigtriangleup t_y=\bigtriangleup t_x+\delta_t≤\bigtriangleup t^{max} △ty=△tx+δt≤△tmax,其中ADC在 △ t x \bigtriangleup t_x △tx和 △ t y \bigtriangleup t_y △ty的值之差表示为整数 K K K。 K K K的值越大,系统的抗噪声鲁棒性就越好,但是会压缩电容器的计时范围。 △ t x \bigtriangleup t_x △tx对应的电压为 V x V_x Vx, △ t y \bigtriangleup t_y △ty对应的电压为 V y V_y Vy,则可得:

V x − V y ≥ K V 0 2 N V_x-V_y\ge K\frac{V_0}{2^N} Vx−Vy≥K2NV0

将上式与RC放点模型函数

t

=

−

R

C

ln

(

V

/

V

0

)

t=-RC\ln{(V/V_0)}

t=−RCln(V/V0)可得:

△

t

y

≤

R

C

ln

(

2

N

K

(

exp

(

δ

t

R

C

)

−

1

)

)

≜

△

t

m

a

x

\bigtriangleup t_y \le RC\ln{\left (\frac{2^N}{K}\left (\exp\left (\frac{\delta_t}{RC}\right ) -1\right ) \right ) }\triangleq\bigtriangleup t^{max}

△ty≤RCln(K2N(exp(RCδt)−1))≜△tmax

根据这一定义式,就能推断出各个层的最大时序范围。除了时间范围外,我们还需要确定层的数量。不同的应用有不同的精度和范围要求,例如某些关键的数据样本可能在几毫秒内过期,而非关键数据样本在100ms内过期,并且在输出时以1秒的精度加上时间戳,因此需要一系列不同的层来保持准确性限制。在确定一组由分辨率和最大可计时范围表示的计时需求后,多次使用上述公式来计算其所需的CHRT层数量以及大小。

CHRT软件层:

为了让CHRT能够服务各项应用程序,需要开发针对的CHRT配套软件支持。本文作者为CHRT架构开发了两种软件层接口:

-

原始接口(raw interface):

用于直接请求CHRT硬件对层进行充电并在重新启动时检索经过的时间,最大限度地利用可用层,从而最大限度地提高能源效率和计时分辨率和范围。原始接口是底层计时硬件功能的硬件抽象层,用于CHRT的低级控制,能够根据应用程序的需求和环境的能源可用性预期进行配置,通过指定每次重新启动时应预充电的层数来最大限度地减少能源消。

原始CHRT接口由了解用户任务和操作的运行时或内核公开,但用户也可以在应用程序级别使用它。重新启动后,运行时调用chrt_get_time()函数来检索自上次重新启动以来所用的时间,然后调用chrt_charge() 函数为层充电。

-

高级接口(high-level interface):

将CHRT与数字定时器结合使用,以提供更高级别的功能,如时间戳生成和数据过期。该接口将CHRT的复杂性进行了抽象,使得开发人员无需深入研究电容器放电的基本原理就可以使用计时功能,从而确保CHRT能够适用于广泛的应用程序。

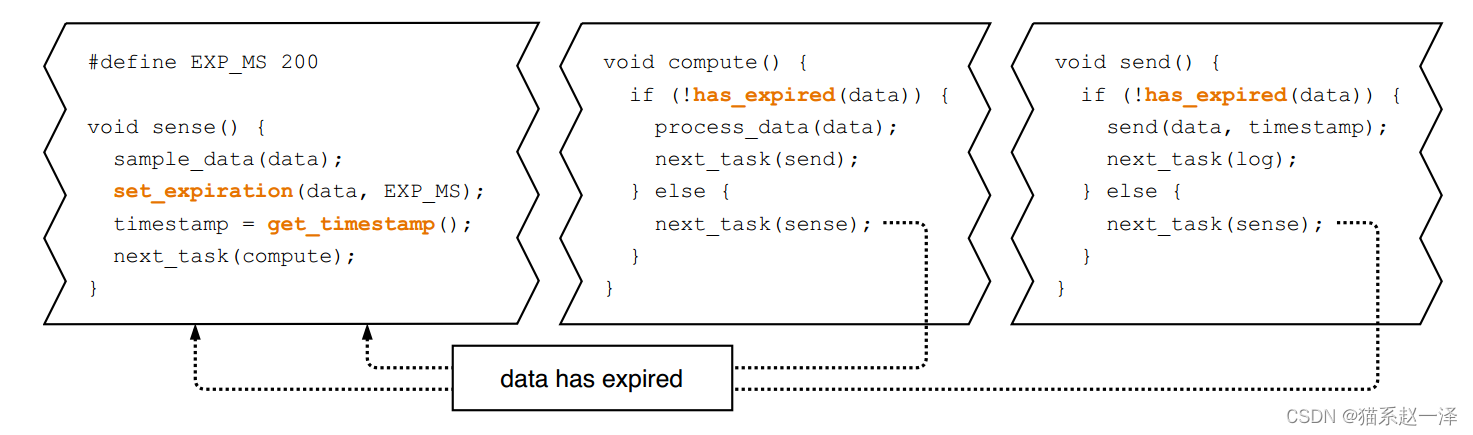

每次重新启动时,系统时间都会根据原始chrt_get_time()函数的结果增加。当在准时期间查询时,系统时间与从后台运行的数字计时器检索到的计时信息相结合。系统时间用于生成时间戳,并设置数据和功能的过期计时器。下图是一个高级接口的应用示例:

get_timestamp()是一个生成时间戳的高级接口函数,当应用程序需要时,使用系统时间来生成时间戳。当调用该函数时,MCU计时器的值被添加到CHRTpowered系统时间中,以返回可用于注释数据的细粒度计时值。

过期计时器可以跟踪数据的老化情况,并在数据被视为过期时将其丢弃。函数set_expiration()用于设置数据或完整函数/任务的过期时间,函数has_expired()用于检查某个对象是否过期。

间歇性管理内核(如InK或Chinchilla)可以使用原始接口定义其自定义计时功能,或者只将高级接口传递到应用层。

理想情况下𝑅𝐶电路放电模型 t = − R C ln ( V / V 0 ) t=-RC\ln{(V/V_0)} t=−RCln(V/V0)可用于估计经过的时间 t t t. 实际上,电容𝐶和电阻𝑅永远不会匹配它们的标称值,并且还有其他寄生电容器和电阻器散布在电路中。为了解决这个问题,需要在CHRT部署之前执行软件校准例程,以获得更好的计时器精度和准确性。在校准期间,CHRT的所有层都被重复充电和放电,并且随着时间的推移对它们的放电曲线进行采样,以获得每个层的真实物理模型。通过这种方式𝑅𝐶建立电路放电模型,并以查找表的形式存储。在运行时,目标层上的电压用于查找表并检索相应的经过时间。

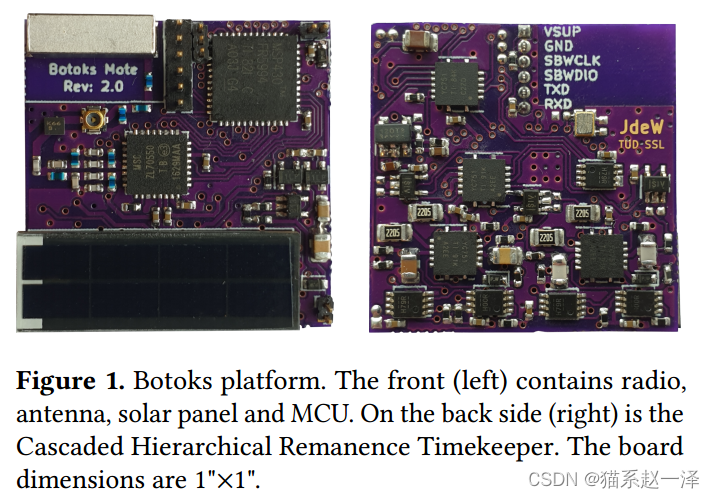

系统实施:

本位针对传感和实时设备中的各种通用计时要求实施了CHRT实例的验证,首先,放电电阻的阻值均为 22 M Ω 22M\Omega 22MΩ,这种电阻不仅成本低廉,同时可以保证在RC电路的长放电时间和电噪声之间的良好平衡。如果需要更大的计时范围,就需要提高电阻的阻值,同时也会引入可能影响准确率和精度的噪声。对于电容器,系统选择四个尺寸不断增加的层:2 nF、22 nF、220 nF和2200 nF,以满足各种应用不同的分辨率和计时范围需求。其中最小层的分辨率1ms,时间间隔大于100ms;最大层时间间隔100ms,分辨率低于1s。

作为概念验证,我们在定制PCB上使用现成组件构建了CHRT。除了四个RC电路之外,CHRT还包括其他重要部件。分立式元器件的ADC、锁存器、开关和比较器都选用超低功耗硬件。为了实现更好的规模、成本、效益,作者还通过台积电 0.18 μ m 0.18\mu m 0.18μm混合信号处理实现了CHRT的集成电路设计,并用Cadence Virtuoso[2]模拟了电路,以提取我们架构的集成版本的功耗估计值。

评估:

为了量化系统的性能,作者从准确性、精度和功耗等方面对CHRT的表现进行了评估。我们发现CHRT在高分辨率(1ms)和长距离(数百秒)下准确无误,启动时间比RTC低两个数量级,功耗极低。以下案例(应用程序)展示了CHRT在实际场景中使用时的性能。

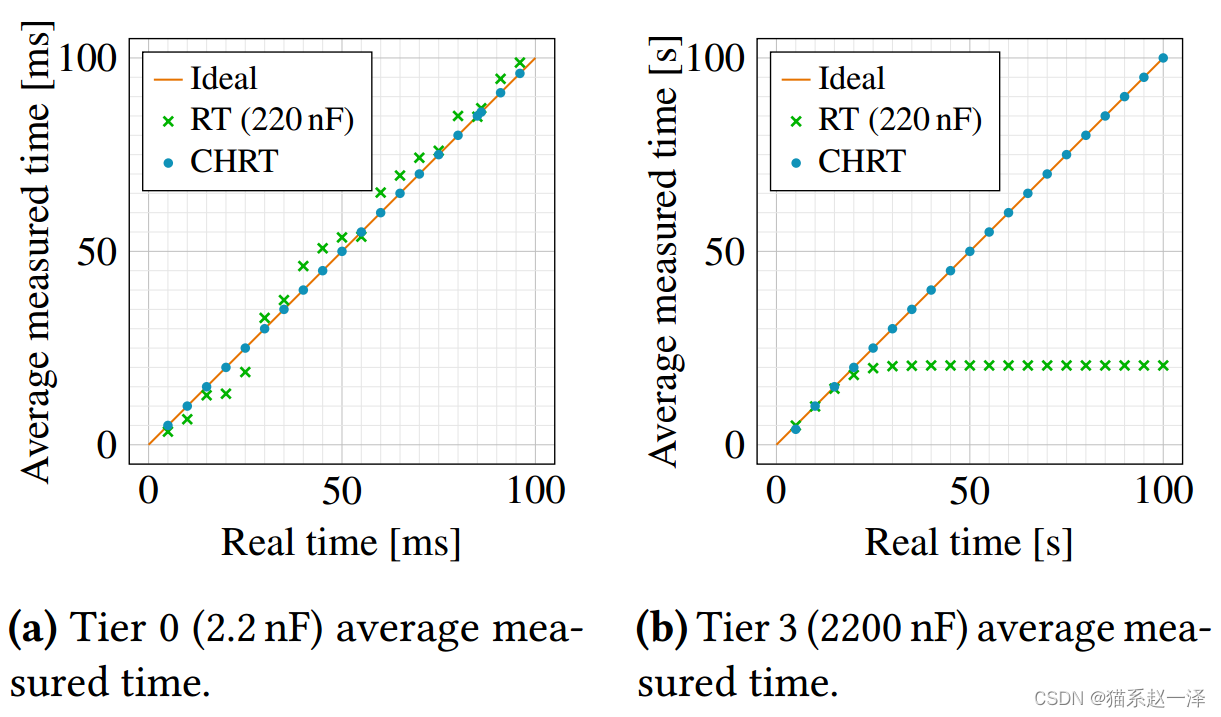

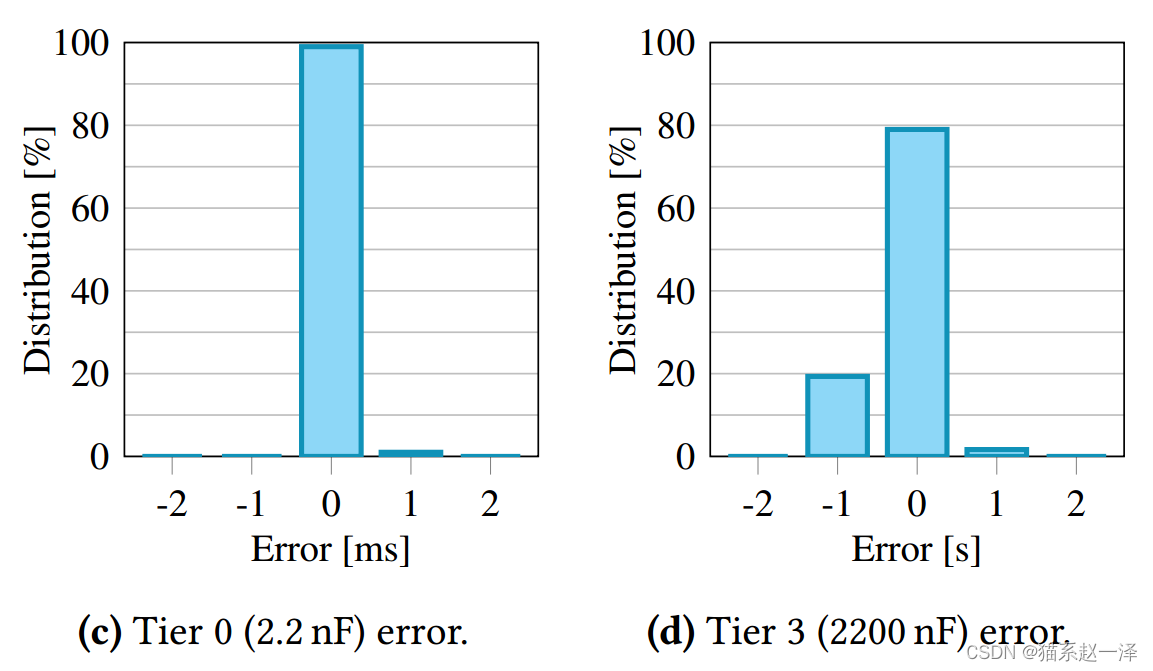

为了评估CHRT四层在应用程序中的计时性能,作者在不同的时间范围和不同的分辨率下对各层进行了广泛的测试。下图展示了CHRT的最小层和最大层的准确性:

(a)和(b)显示了两个层在最佳计时范围内的平均报告时间,其中每个数据点是10个测量值的平均值。除了CHRT和理想值,图中还给出了单程剩磁计数器( 220 n F 220nF 220nF)的精度。可以看出,单层计数器的设计在应用程序中需要在分辨率和计时范围内进行妥协,如果计时时间超过了单层计时器的时间范围,则计时效果大打折扣,这也体现出CHRT在精确度和计时范围方面的优势。

为了进一步研究CHRT的计时性能,作者还记录了最小层和最大层的误差分布,如上图所示,其中两层的最大绝对误差等于它们各自的分辨率。由图可以看出,误差分布很好地以零为中心,并且非常窄,表明CHRT在高分辨率(1 ms)和长距离(数百秒)下是准确和精确的。相比之下单层剩磁计时器在计时范围外的误差分布的标准偏差就要大很多。

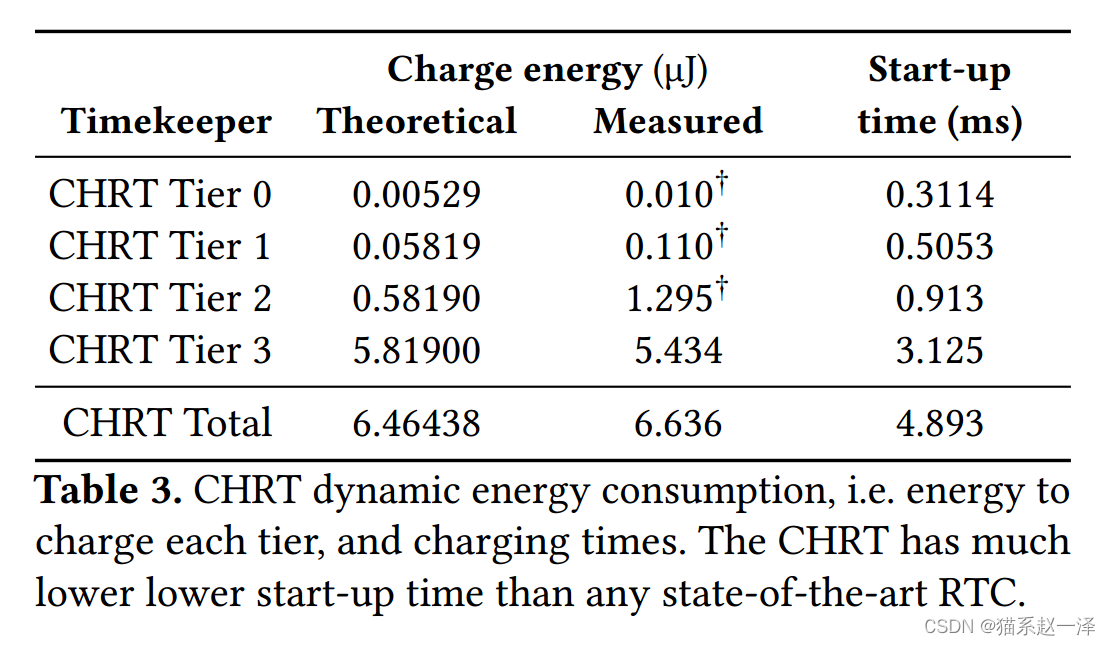

CHRT不仅在计时性能方面表现良好,测量所需的能量也要低很多。当使用2.2V的电压时,SMD版本的CHRT静态电流消耗为 0.958 μ A 0.958\mu A 0.958μA,而集成版本为 37.335 n A 37.335nA 37.335nA。下表展示了CHRT每次重新启动时充电各层所需的能量,也可以看作每层充电的能量,CHRT的启动时间( ≈ 5 m s ≈5ms ≈5ms)比任何先进的RTC都要短得多。

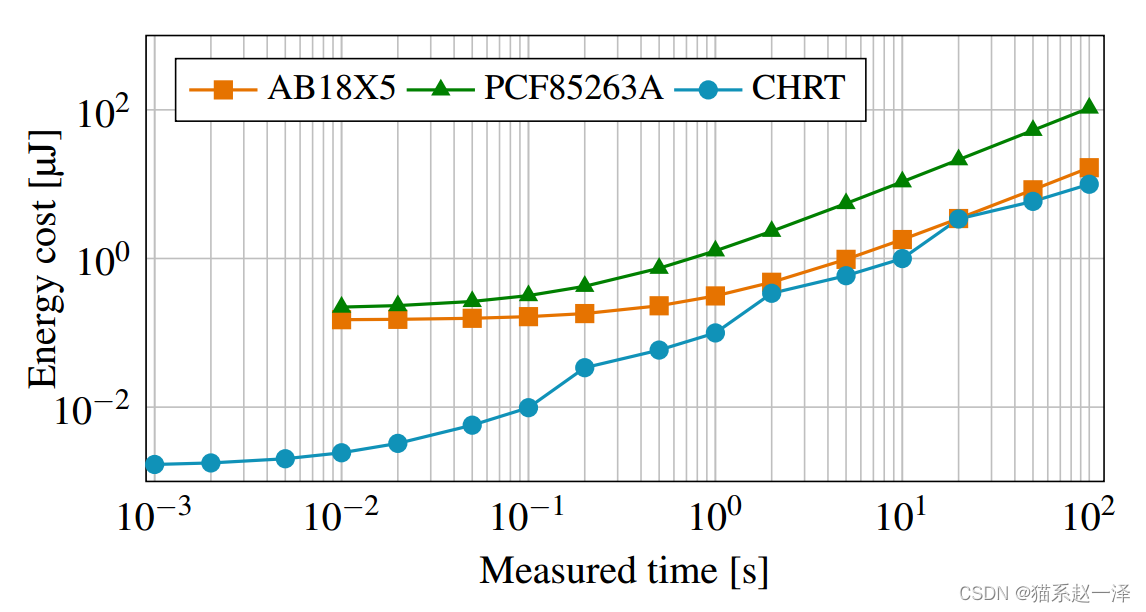

下图展示了CHRT与两个RTC对不同计时时间长度所需总能量的比较。可以看出,与最低功率RTC相比,CHRT允许毫秒计时,同时需要更少或相似的能量。

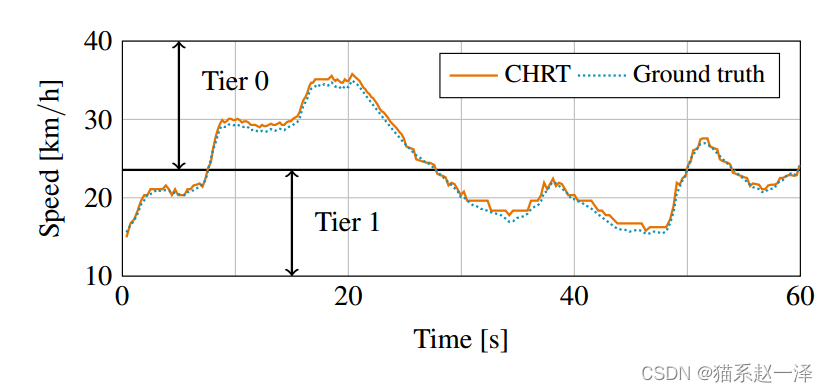

作者构建了一个自行车计速器,使用CHRT通过捕获连续事件(车轮转数)之间经过的时间。对于这种应用,想要提供准确的自行车速度就需要CHRT具备高计时能力与准确性。

对于自行车速度计应用,开发板从自行车后轮的磁铁获取能量,并将能量用于计时、发送数据表与为车灯的led供电。每当一个磁铁靠近能量采集器时,开发板就会醒来。对于性能评估,作者将基站收到的数据与真实速度进行比较,如下图所示。可以看出,使用CHRT估计的速度与预期的结果非常接近。该图还显示了用于不同时间范围的CHRT层。用最小层测量的速度越快,分辨率越高,图形中的曲线越平滑。在多次应用实验后,求得总平均RMS误差为0.5 km/h。

作者还构建了一个消息传递协议应用,使两个间歇供电设备的无线电通信保持一致。这个实时系统对于计时的准确度的要求更高,因为主动无线电传输和接收消耗大量能量,对于网络节点来说,准确地知道何时打开它们的无线电以最大限度地减少数据包丢失和能源浪费是至关重要的。

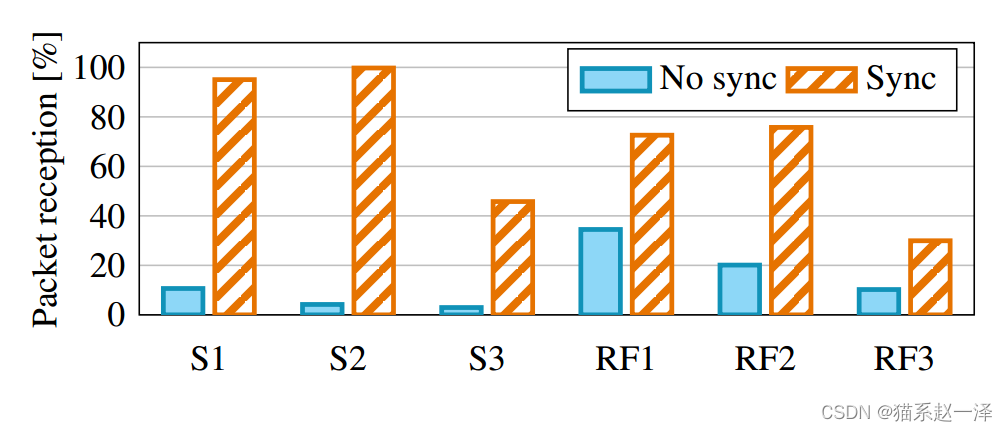

在这个点对点连接应用中,一个节点由太阳能供电,另一个由射频能量供电。在节点唤醒后,利用缓存的能量发送一个数据包,并再次进入电源故障,继续收集能量。同样,另一个节点唤醒后将进入侦听,直到收到数据包或断电。每个数据包包含序文、CHRT测量的平均时间,一个虚拟有效载荷和一个16b的CRC,以 200 k b / s 200kb/s 200kb/s的数据速率发送。接收器使用每个数据包中包含的平均传输周期来改变其侦听计划并与发送器保持一致。

上图表示了在六种不同的能量收集条件下,两个Botoks设备之间点对点链路接收数据包的百分比,将使用chrt驱动的同步算法接收的数据包百分比与基线情况(没有同步)进行比较。可以看出,在最佳情况下,射频接收数据包增加了3.77倍,太阳能增加了23.75倍。

结论:

本文提出了一种新的无电池计时机制,实现了可靠的无电池感知和计算,即级联分层剩磁计时器(CHRT),并提出了两个适用于间歇计算的应用实例:时间关键感知和间歇通信。CHRT是基于一个层次结构的剩磁计时器的想法,它结合了精度/分辨率,并且有很快的冷启动速度,同时也兼容长时间的电源故障计时。结合CHRT架构到一个硬件和软件平台,我们提出了botoks的设计和实现-一个新的无电池传感器。有了Botoks及其附带的CHRT,间歇性计算可以进入一个新的阶段,并探索到目前为止不可能实现的新应用程序。

本文围绕无电池设备的可靠计时问题展开。指出当前低功耗计时方案不适合间歇性运行,提出级联分层剩磁计时器(CHRT),介绍其硬件和软件设计,通过实验验证其在高分辨率、长距离计时上表现良好,启动时间短、功耗低,并给出自行车计速器和消息传递协议两个应用实例。

本文围绕无电池设备的可靠计时问题展开。指出当前低功耗计时方案不适合间歇性运行,提出级联分层剩磁计时器(CHRT),介绍其硬件和软件设计,通过实验验证其在高分辨率、长距离计时上表现良好,启动时间短、功耗低,并给出自行车计速器和消息传递协议两个应用实例。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?