前序

相信大家在网上可以找到本文章的类似教程,我就是这样,找到了教程,兴致冲冲地按教程每个步骤操作,但最后因为素材不一样,得不到想要的结果,有时出来的波形是一条水平线,有时出来的是脉冲振荡收敛波形,离谱的是还出现过脉冲振荡不收敛,当时的我懵逼了,差点砸了电脑,后来,看开了,慢慢理解,慢慢实验,最后,成功了。

所以我将利用Sigrity的SPEED2000进行时域电源噪声分析教程写出来,同时,将SPEED2000用于电源噪声的时域分析和验证的仿真素材上传:

https://download.youkuaiyun.com/download/ZHENGSA/85934288?spm=1001.2014.3001.5503

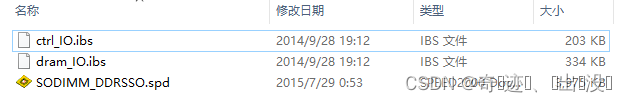

供大家使用,不用苦苦寻找仿真资料。资料里包括:SODIMM_DDRSSO.spd(DDR3 SODIMM板卡)、ctrl_IO.ibs(I/O控制模型)、dram_IO.ibs(动态随机存储器模型)。

电源噪声的时域分析是电源完整性设计重要内容,所以大家不妨尝试仿真一下。

前期准备

软件:Cadence Sigrity2018

仿真资料:SODIMM_DDRSSO.spd、ctrl_IO.ibs、dram_IO.ibs

正文

打开软件

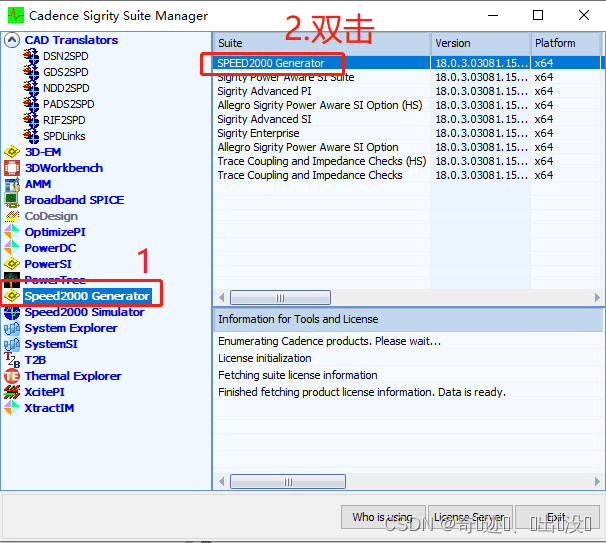

先找到Sigrityg管理软件(这个可以找到很多仿真软件):

电脑开始—Cadence Sigrity2018—Sigrity Suite Manager

找到SPEED2000 Generator,双击打开(找不到SPEED2000 Generator没关系,随便双击一个,因为他们都是指向一个路径同一个软件):

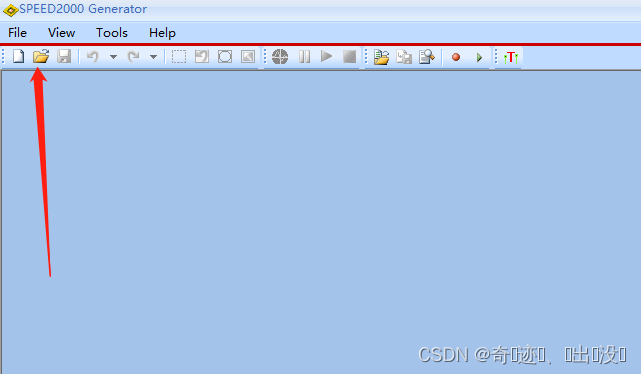

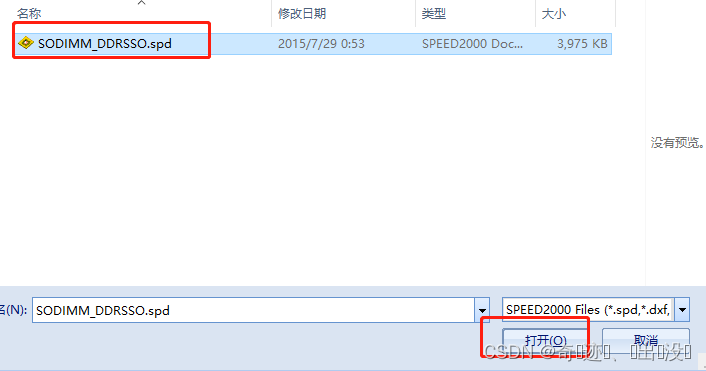

打开SODIMM_DDRSSO.spd

点击Open,找到SODIMM_DDRSSO.spd,打开

打开界面

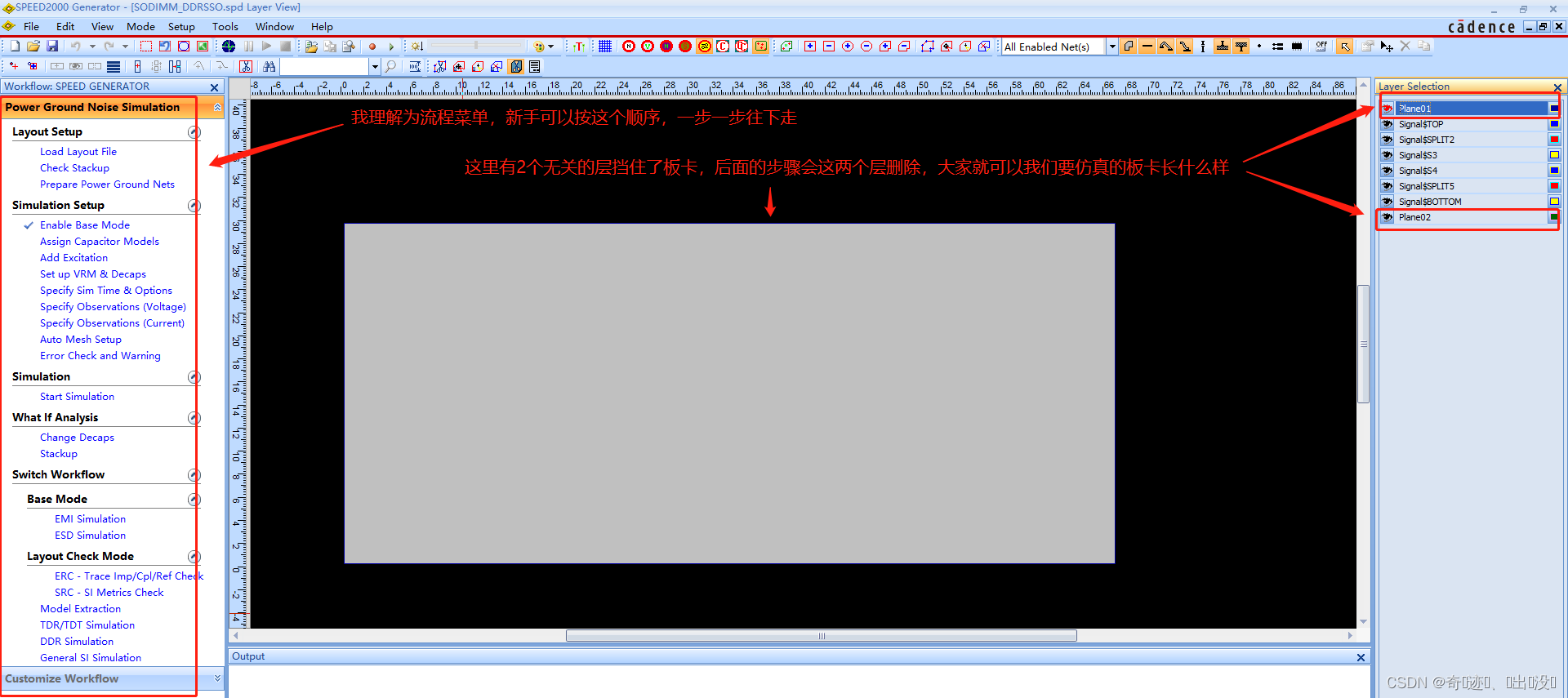

打开界面后,可以看到下面的界面,左边窗口一推英文是一些相关参数设置和操作,中间是PCB板的视图,现在被两个无关的层挡住了,后面的步骤会将其删除,则可看到我们要仿真PCB板的模样,右边窗口是层管理器

进入DDR Simulation模式

SPEED2000的仿真有很多仿真模式,它是整板系统级全波瞬态分析工具,电源地之间的波动(同步开关噪声),过孔和走线之间的耦合,以及电路和封装间的交互作用

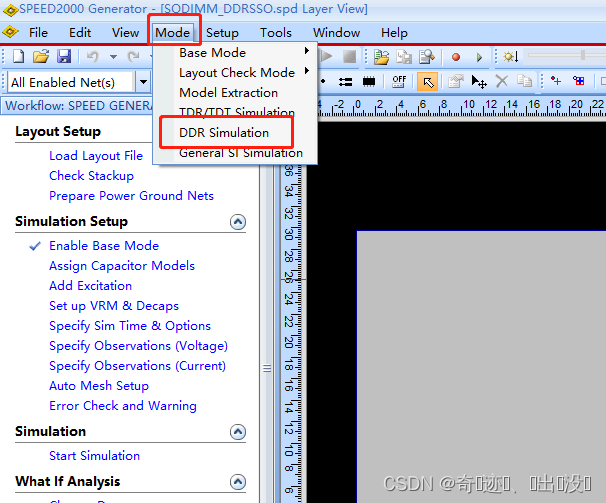

现在我们需要进入DDR Simulation模式,打开Mode–DDR Simulation:

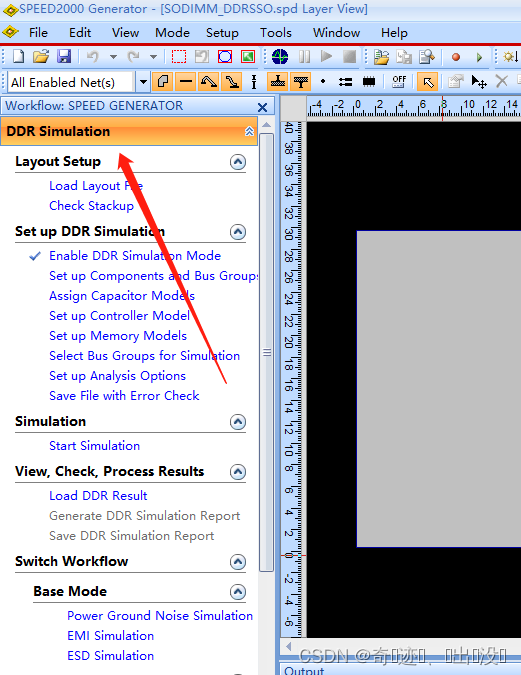

打开DDR Simulation模式,左边窗口变成DDR Simulation模式的参数设置界面。

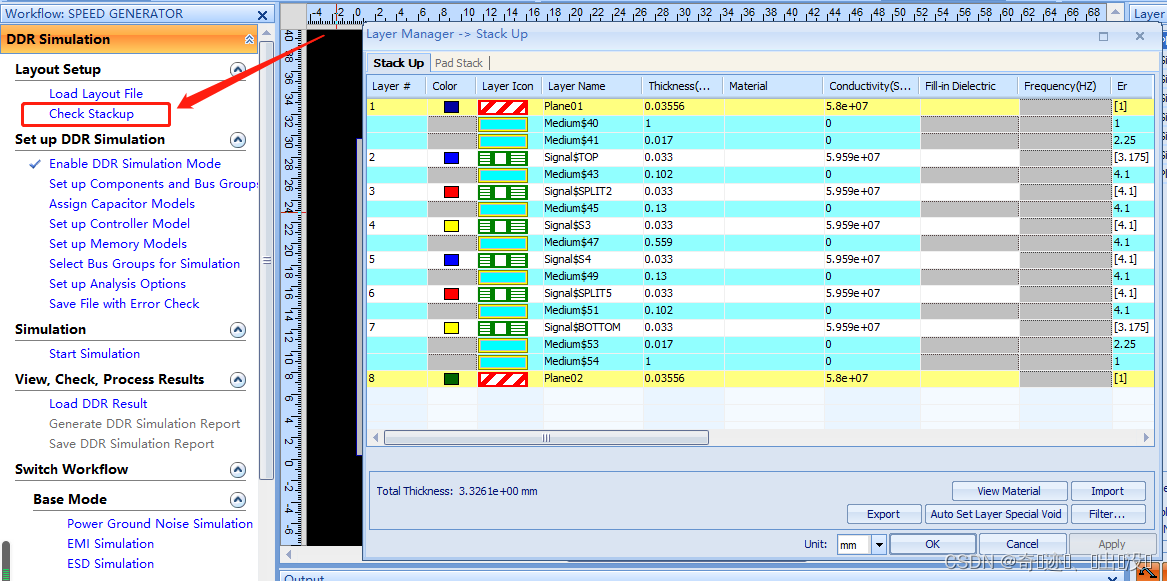

检查层叠

首先,我们打开层叠管理器,可以看到层叠信息,同时我们前面提到无关的层就是:Plane01、Plane02。

由于素材的层叠设计没完善,那我们可以自己设计层叠,或找板厂要一份六层的叠层结构,我直接按某个叠层结构来吧:

①删除无关层:

本文档详细介绍了如何使用Cadence Sigrity 2018中的SPEED2000工具进行电源噪声的时域分析。从前期准备、软件设置、PCB素材处理、元件和总线组设置、模型分配到仿真参数配置,每个步骤都有清晰的说明和操作指导。特别强调了DDR3 SODIMM板卡的电源完整性设计,包括层叠管理、焊盘设置、元件模型匹配和仿真网络选择。最终,作者提供了仿真过程可能出现的问题及解决办法,并分享了仿真素材供读者实践。

本文档详细介绍了如何使用Cadence Sigrity 2018中的SPEED2000工具进行电源噪声的时域分析。从前期准备、软件设置、PCB素材处理、元件和总线组设置、模型分配到仿真参数配置,每个步骤都有清晰的说明和操作指导。特别强调了DDR3 SODIMM板卡的电源完整性设计,包括层叠管理、焊盘设置、元件模型匹配和仿真网络选择。最终,作者提供了仿真过程可能出现的问题及解决办法,并分享了仿真素材供读者实践。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

319

319