DC-DC电源中的地线

参考视频:

去耦电容、旁路电容(二)“接地才是关键!”,仿真实验揭示答案

目录

一、PCB上放置去耦电容,旁路电容的规则,

- 接地不好,会导致旁路电容失去作用,PCB上放置去耦电容,旁路电容的规则,一句话就是,

保证最小阻抗路径连接

- 尽量靠近芯片电源角

- 最短路径连接到地

尽量靠近芯片电源角 尽量靠近芯片电源角

|

最短路径连接到地 最短路径连接到地

|

二、电容本身的esr和esl参数

- 当频率升高时,电容可能发生谐振,失去容性甚至成为一只电感,

- 解决方法:

大电容旁边并联一个小电容:

原因是大电容通常ESL(等效电感)比较大,需要一个ESL较小的电容来中和,

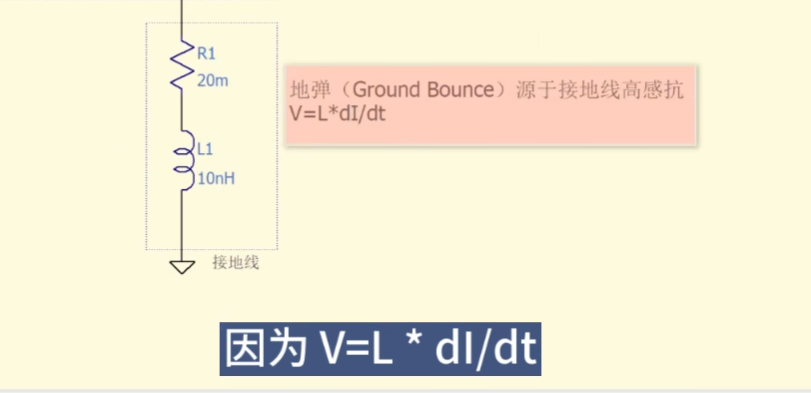

Ground Bounce(地弹)

- 因为地线的分布参数,使输出信号的上下沿部分出现了振铃,地线山也出现了Ground Bounce(地弹)

Ground Bounce(地弹)的危害还在于;两段信号共用一段地线时, 两路信号不仅出现了振铃,也出现了串扰

地弹+振动 地弹+振动

|

串扰 串扰

|

如何避免地弹造成的影响

- 地线上的感抗要尽量小;

- 不同的高频信号不要共用接地;

所以越是电流大,频率高的地方越容易出现地弹干扰

- 使用这种宽平面结构的连接器,带状线缆,在信号线之间加一根地线;

- 采用封装引脚短小的元件(如MLCC电容,BGA封装芯片)

图1 MLCC电容 图1 MLCC电容

|

图2 BGA封装芯片 图2 BGA封装芯片

|

6.较高频率数据线处理

- 几十赫兹以下的电路,可采用双层电路板,

- 一般元器件和走线放上层,底层为地和电源,

- 但双层板很难保证地平面的完整性,好在频率不高时,影响不会很大,

- 但是注意,两面灌水铺铜,尽量不要留空白,

- 尤其是高频信号,最好是以地线围绕,

- 比如图中的USB数据线,一定要用过孔缝合,两层铺铜,保证大片连续的地,删除孤立铺铜,

- 更高频率时采用多层板设计,设计一层或者多层地平面

- 避免在地平面上走线,造成地平面分割

- 灌水铺铜要放置过孔到地层

- 高频信号线下,或周围要有接地铺铜,以保证信号有最短的返回路径,

- 信号线换层,要打回流地孔

过孔缝合,两层铺铜**,保证**大片连续的地,删除孤立铺铜 过孔缝合,两层铺铜**,保证**大片连续的地,删除孤立铺铜

|

灌水铺铜要放置过孔到地层 高频信号线下,或周围要有接地铺铜, 信号线换层,要打回流地孔 灌水铺铜要放置过孔到地层 高频信号线下,或周围要有接地铺铜, 信号线换层,要打回流地孔

|

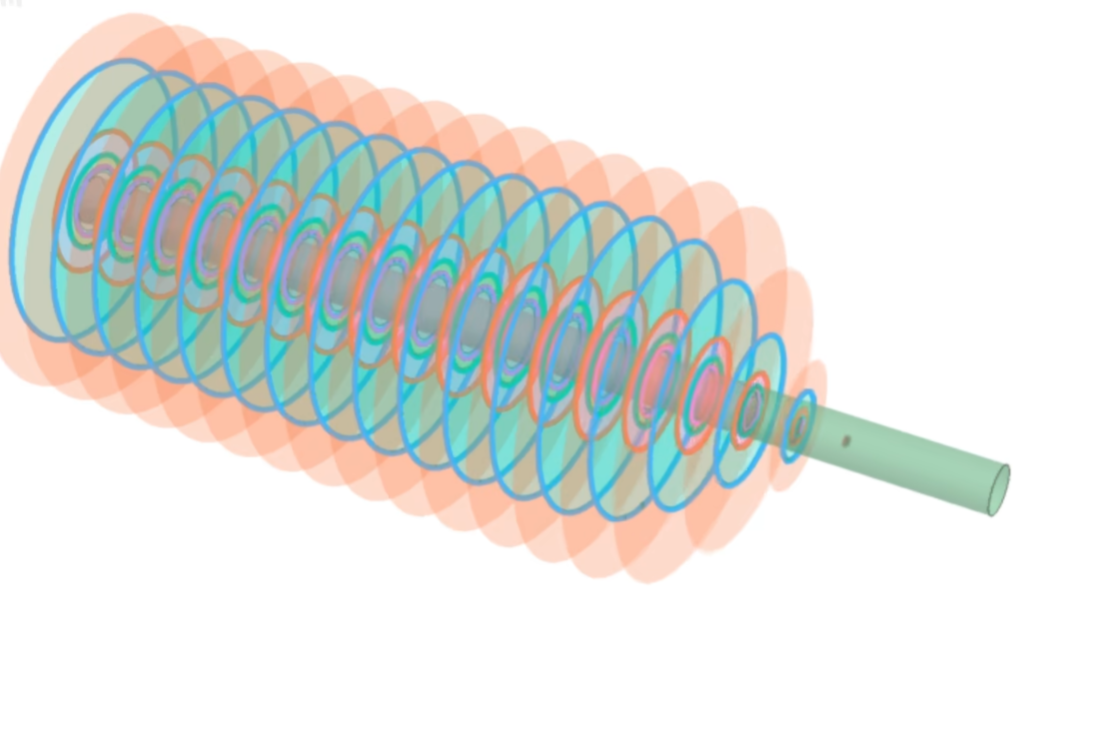

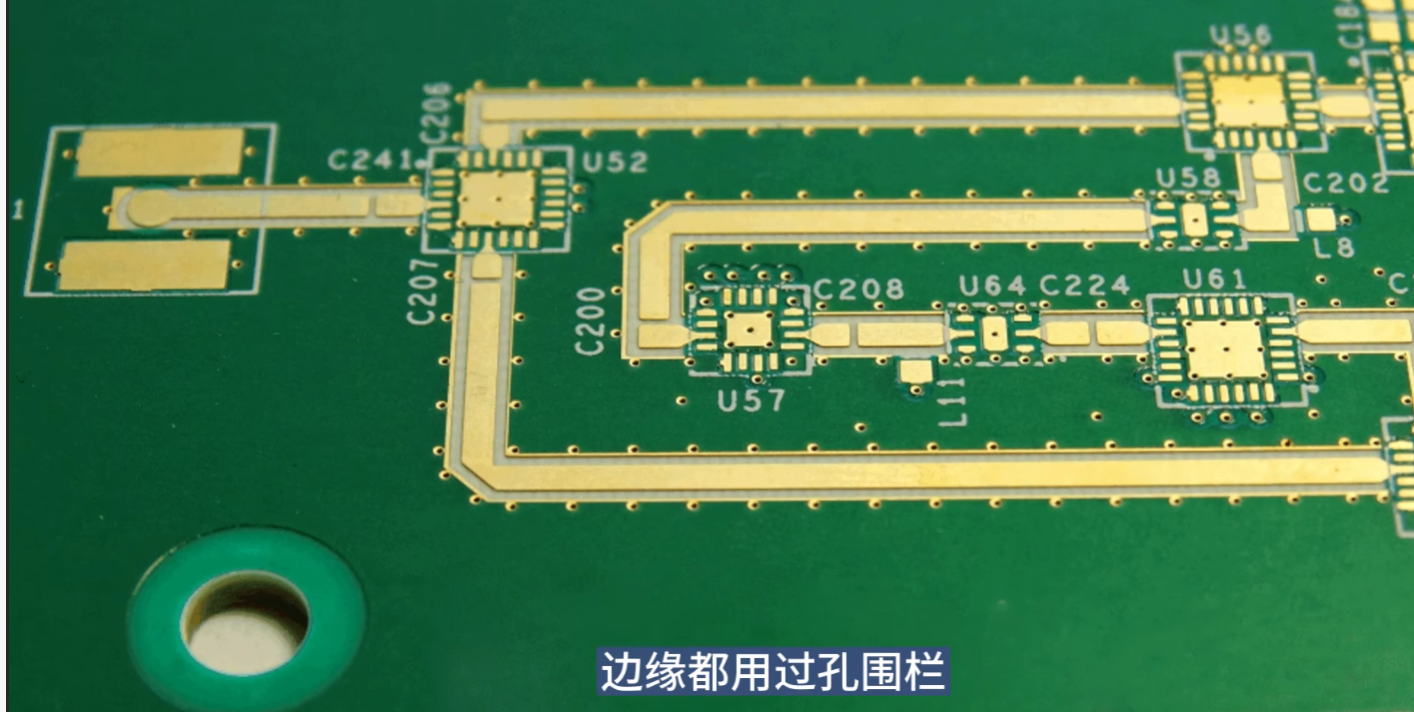

三、射频电路中的地

- 信号波长与导线尺寸相当,所以考虑的更多,应当用电磁波来理解电路中的高频电流,并用传输线理论来指导布线

比如这种RF信号,用地线包围起来,边缘都用过孔围栏

五、两个实例

重点看看去耦电容和旁路电容如何接地

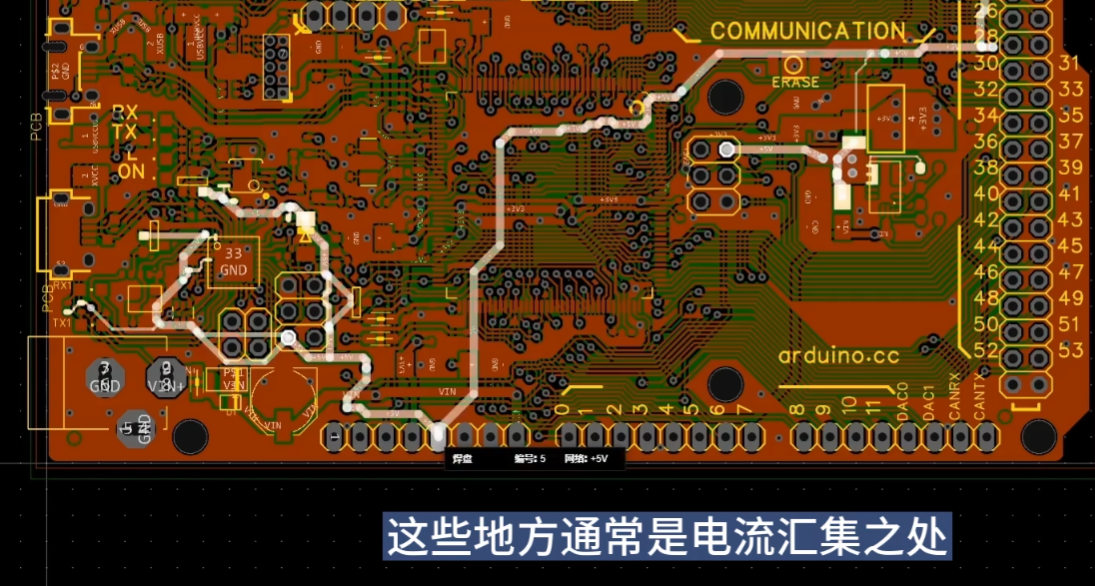

5-2、主频80Mhz,的两层板

- 电源和地基本放在底层,顶层灌水铺铜,然后放置适当的过孔,连接上下层,尤其是信号输入输出,电源输入这些地方通常是电流汇集之处,过孔就放置多一些,

- 芯片旁边具有旁路电容,芯片下方的铺铜有两个过孔,与下方的地连接,

- 电容的接地点铜箔面积比较大,或者放置过孔与下层的地连接

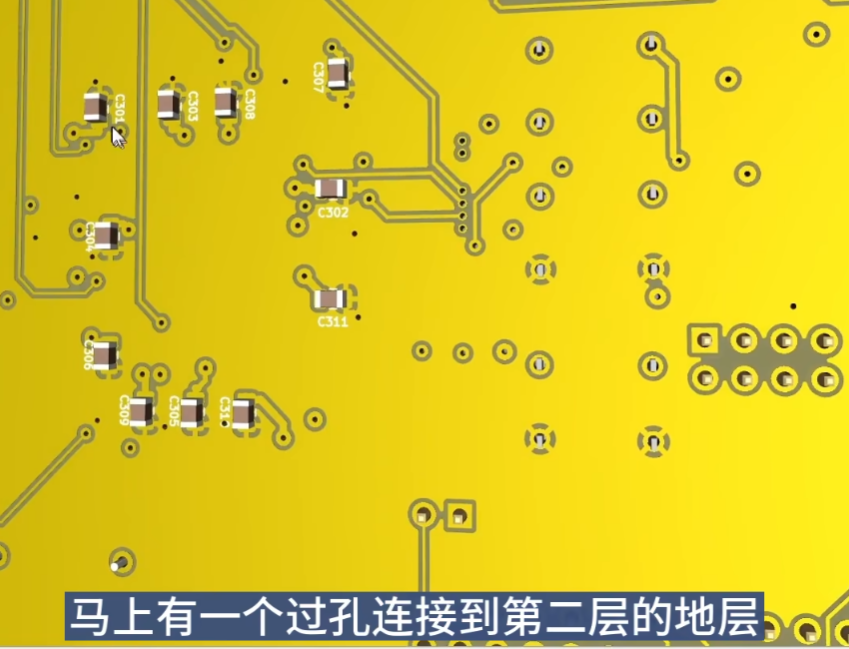

5-2四层的FPGA开发板

- 这个芯片的去耦电容全部放置在底层,物理位置全部在芯片管脚的下边,注意,他们虽然已经与底层的大片地相连接,马上有一个过孔连接到第二层的地层,这样才能达到最小阻抗到地的目标

本文探讨了在DC-DC电源设计中,去耦电容和旁路电容的正确放置规则,强调了良好接地对信号质量和电磁兼容性的重要性。讲解了如何通过减小地线感抗、避免共地干扰、使用特殊连接器和组件来抑制地弹效应。特别针对射频电路和高频应用提供了实例和最佳实践,包括多层板设计和信号线布局技巧。

本文探讨了在DC-DC电源设计中,去耦电容和旁路电容的正确放置规则,强调了良好接地对信号质量和电磁兼容性的重要性。讲解了如何通过减小地线感抗、避免共地干扰、使用特殊连接器和组件来抑制地弹效应。特别针对射频电路和高频应用提供了实例和最佳实践,包括多层板设计和信号线布局技巧。

5988

5988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?