前言

之前我们一直没有介绍与内存相关的寄存器以及页项中的各个属性位及其影响,现在我们写这篇文章来分析一下有关机制。

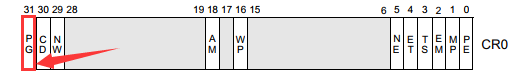

CR0.PG

Paging (bit 31 of CR0) — Enables paging when set; disables paging when clear. When paging is disabled, all linear addresses are treated as physical addresses. The PG flag has no effect if the PE flag (bit 0 of register CR0) is not also set; setting the PG flag when the PE flag is clear causes a general-protection exception (#GP). See also: Chapter 4, “Paging.”

这个PG代表paing,当该位置为1时表示开启分页模式,开启该模式,你访问的地址为线性地址而不是物理地址,要通过页表来进行转换。要注意,在打开该模式前,其首先开始保护模式,即PE位必须置为1,否则无效。

在代码中构建好页表之后,直接将这个位置为1即表示打开分页模式。

; 打开 paging

mov eax, cr0

bts eax, 31

mov cr0, eax

本文深入分析了x86/x64架构下的内存管理机制,涉及CR0和CR4寄存器中的关键位如PG、WP、CD/NW、PSE、PAE、PGE等,以及它们在分页、缓存和权限控制中的作用。同时,文章提及了CR3寄存器和PDE、PTE页表项的属性。通过对这些概念的探讨,读者能更好地理解操作系统如何管理内存。

本文深入分析了x86/x64架构下的内存管理机制,涉及CR0和CR4寄存器中的关键位如PG、WP、CD/NW、PSE、PAE、PGE等,以及它们在分页、缓存和权限控制中的作用。同时,文章提及了CR3寄存器和PDE、PTE页表项的属性。通过对这些概念的探讨,读者能更好地理解操作系统如何管理内存。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

916

916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?