前言

其实在学Windows内核时,仅知道两种分页模式,2-9-9-12,10-10-12 分页模式,其了解过还有其他模式但是平常用的很少,印象也就不深刻了。现在要写这篇文章,结合《intel手册》与《x86/x64编程体系探索》这两本书,我们来总结x86架构下的三种分页模式。

x86下分为三种分页模式:Non-PAE模式、PAE模式、4-Level模式。我们现在先来依次分析这三种模式,之后再来对比与总结。

Non-PAE模式

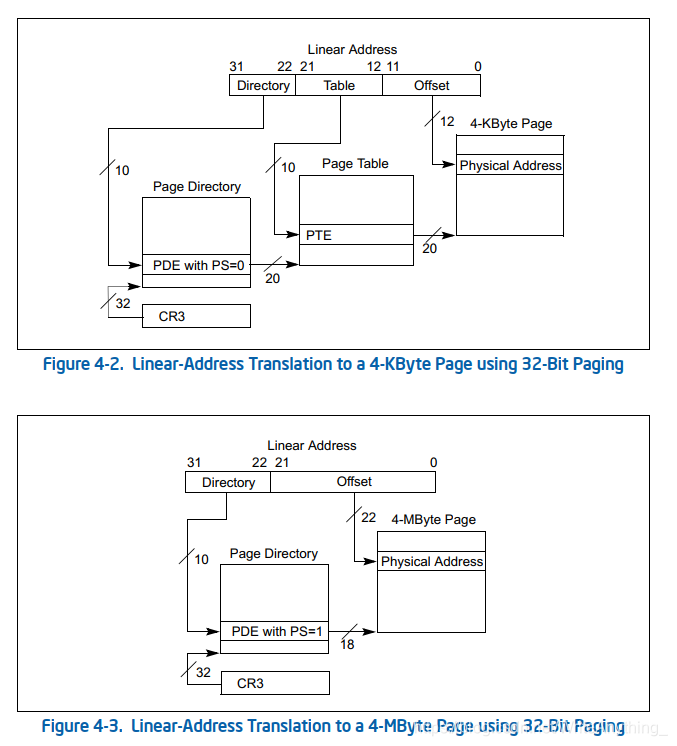

所谓Non-PAE模式,就是普通的32位分页模式,其存在10-10-12与10-22两种分页机制。我们所要看其页的大小,看其最后一位数字即可(12,22),因为在分页机制下,其最后一位是计算偏移,其也代表了页内的寻址能力(及页的大小)其分别换算为4K与4M。

Non-PAE的开启是由寄存器控制的,其当CR0.PG==1,CR4.PAE==0表示开启Non-PAE模式;但是其选择10-10-12或10-22两种模式是由其页表值所决定的,当ItemValue.PS==1时,表示其指向的是一个大页。

下面是在Non-PAE模式下10-10-12与10-22两种机制的模拟图,摘自Intel手册:

上图描述的还是很清楚的,对于Non-PAE模式来讲,32位的线性地址对应着32位的物理地址,当我们分析完其余两种模式之后,我们再来将这三种总结对比,继续往下

本文介绍了x86架构下的Non-PAE、PAE和4-Level Paging三种分页模式。Non-PAE模式包括10-10-12和10-22两种机制;PAE模式支持4KB和2MB页,采用4个PDPTE,通过CR3和PDPTE转换32位线性地址到52位物理地址;4-Level Paging模式针对超过4GB内存需求,增加PML4E,支持48位线性地址到52位物理地址转换。

本文介绍了x86架构下的Non-PAE、PAE和4-Level Paging三种分页模式。Non-PAE模式包括10-10-12和10-22两种机制;PAE模式支持4KB和2MB页,采用4个PDPTE,通过CR3和PDPTE转换32位线性地址到52位物理地址;4-Level Paging模式针对超过4GB内存需求,增加PML4E,支持48位线性地址到52位物理地址转换。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2406

2406

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?