AXI,Advanced eXtensible Interface,高级可扩展接口,是一种被广泛使用的总线协议。该协议在ARM公司推出AMBA3.0协议中首次提出,是一种面向高性能、高带宽、低延迟的片内总线。

AXI Architecture

在最开始,我们先了解下AXI总线的结构

AXI协议是以传输为基础的,并定义了五个独立的通道:

- 写请求,信号名称以AW开头。

- 写数据,信号名称以W开头。

- 写响应,信号名称以B开头。

- 读请求,信号名称以AR开头。

- 读数据,信号名称以R开头。

请求通道中传输的是描述要传输的数据性质的控制信息。

数据通道中传输的是主机和从机之间通信的数据。

响应通道中传输的是写入数据的完成信号,指示写操作是否完成。

AXI除了使用多通道的结构,并且还有一个特点就是单向通道体系结构,每个通道中,数据流是单方向传输。

每个通道都有单独的握手机制,确保数据传输的准确性。

这里提出一个问题,为什么AXI中只有写响应通道,没有独相应通道呢?

AXI结构中,只支持数据的单向传输。

写事务如下图,主机使用写请求通道发送写控制信号,再从写数据通道将数据发送至从机,但主机如何知道从机正常完成了写操作呢,由于写数据数据和写响应方不一致,因此需要额外增加一个通道,即写响应通道,让从机发送信息告知主机,是否正常完成了操作。

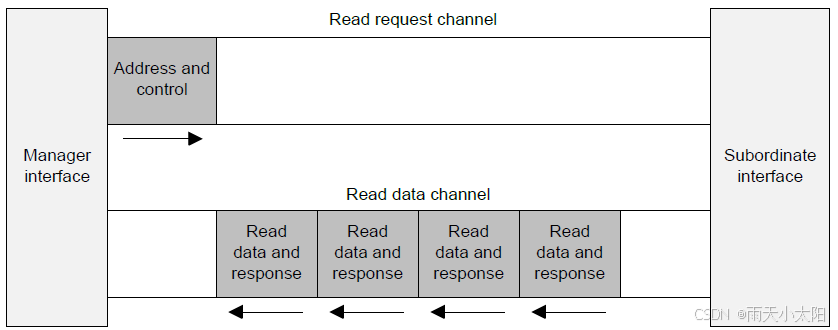

读事务如下图所示,主机通过读请求通道将读控制信息发送至从机,从机通过读数据通道将数据发送至从机。如何让主机知道读的数据是否正确呢?由于数据和响应信号传输方向一致,从机可以将读响应信号和数据一起通过读数据通道发送至主机,不需要专用的读相应通道。

结论:不是AXI的读操作不需要响应信号,而是读响应和读数据共用了读数据通道!

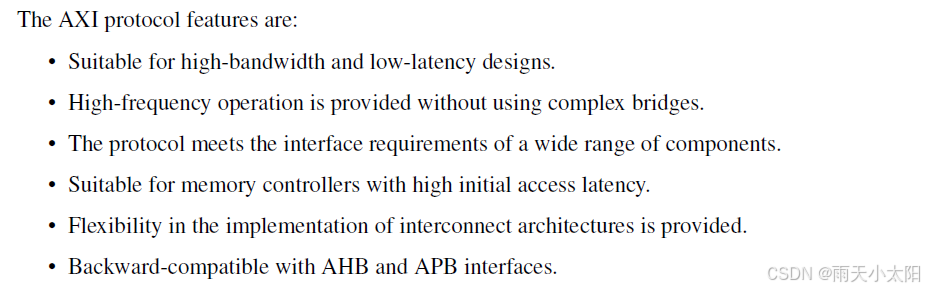

AXI Features

接下来我们将根据ARM官方手册来对AXI总线特性进行深入剖析。

我们逐条进行分析

Suitable for high-bandwidth and low-latency designs

AXI适用于高带宽和低延迟的设计,这里我们探讨下为什么AXI可以实现高带宽和低延时呢?

首先我们先了解一下如何评判总线的性能,常见的两个指标的带宽(bandwidth)和延迟(latency)。

带宽

首先先说带宽(bandwidth),总线带宽,即总线数据传输速率。带宽用来标识信号传输的数据传输能力。从带宽的公式 带宽=时钟频率*总线宽度/8(单位:Byte/s) 可以看出带宽描述的是单位时间内可以传输数据的总量,因为每秒传输的字节数越多,则带宽越高。

AXI总线宽度可以根据实际使用场景配置为8,16,32,64,128,256,512或1024,在高性能芯片设计中,AXI的总线一般为128比特。相较于AHB,APB总线架构的芯片中,总线宽度一般为32比特,AXI总线宽度更高。

AXI总线的工作时钟频率通常会在几百兆赫兹到吉赫兹范围内,相较于传统AHB总线,最高几百兆赫兹来说,工作频率更快。

因为AXI的总线宽度相较于传统总线支持位宽更高,可实现的总线时钟频率也更高,所以AXI总线性能也更高。

延迟

现在我们继续了解一个总线性能的关键指标延迟(latency)。AXI总线延迟指的是主机在发出读写请求后,到主机收到读写响应所消耗的时钟周期数。

AXI传输中的延迟消耗在哪些地方呢,首先是数据和命令在传输途径中的消耗,这个一般根据固定架构来说是固定的;再就是是从机处理命令和数据的消耗,这个对于从机来说也是固定的,那AXI总线是如何降低延迟呢,这里就要提到AXI总线的三大传输特性:

- Outstanding,不用等待上次一传输完成就开始新的传输地址的能力;

- Out-of-Order,乱序传输,不用按照原先的传输顺序,快的传输可以提前进行;

- Interleave,交织传输,指得是两笔传输同时进行,数据可以进行交错传输

Outstanding

Outstanding是总线具备不用等待上次一传输完成就开始新的传输地址的能力,这种特性可以使主机在不用管上一笔数据是否完成就可以继续发送数据操作请求。

2842

2842

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?