一、上下拉电阻的核心作用

-

消除浮空状态

-

浮空信号线的风险:当电路节点未被任何驱动源(如芯片引脚、开关或晶体管)主动拉高(High)或拉低(Low)时,信号线处于高阻抗状态(高阻态),极易受外部电磁干扰(EMI)或寄生电容影响,导致电平随机跳变(如误触发逻辑门或MCU误读)。

-

解决方案:

-

上拉电阻:将信号线通过电阻连接到电源(VCC),在无主动驱动时强制拉至高电平。

-

下拉电阻:将信号线通过电阻连接到地(GND),在无主动驱动时强制拉至低电平。

-

-

-

提供默认逻辑状态

-

在按键、开关或传感器等输入电路中,上下拉电阻可定义未动作时的默认电平。例如:

-

按键未按下时,通过下拉电阻使MCU引脚保持低电平;按下时,按键将引脚拉至高电平(或相反)。

-

-

-

匹配开漏/开集输出电路

-

开漏(Open-Drain)或开集(Open-Collector)输出(如I²C总线、某些GPIO模式)无法主动输出高电平,需依赖上拉电阻提供高电平驱动能力。

-

二、典型应用场景

1. 数字输入接口(如MCU GPIO)

-

按键/开关电路:

-

下拉电阻:按键一端接VCC,另一端通过下拉电阻接地。未按下时,MCU引脚为低电平;按下时拉高(见图2)。

-

上拉电阻:按键一端接地,另一端通过上拉电阻接VCC。未按下时为高电平,按下时拉低。

-

优势:避免引脚浮空导致的误触发。

-

-

传感器信号线:

-

部分传感器(如光电开关)输出为开集结构,需上拉电阻将信号转换为标准逻辑电平。

-

2. 总线通信协议(如I²C、1-Wire)

-

I²C总线:

-

SDA(数据线)和SCL(时钟线)均需上拉电阻,确保总线在空闲时保持高电平。

-

阻值选择需平衡总线电容和通信速率(通常1kΩ~10kΩ)。

-

-

1-Wire总线:

-

单线通信依赖上拉电阻提供电源和信号传输的复合功能。

-

3. 复位电路与使能信号

-

复位引脚(RESET):

-

通过上拉电阻保持高电平,避免意外复位;按键按下时拉低触发复位。

-

-

使能引脚(EN):

-

下拉电阻确保芯片默认禁用,上电后需主动拉高使能。

-

4. 数字逻辑门输入

-

CMOS逻辑门输入引脚需通过上下拉电阻避免浮空,防止功耗激增或逻辑错误。

三、设计考量与参数选择

1. 电阻值计算

-

基本原则:

-

足够小:确保信号上升时间满足通信速率要求(trise=R×Cload)。

-

足够大:限制电流以降低功耗

。

。

-

-

公式推导:

-

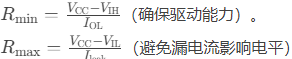

上拉电阻最小值:

-

上拉电阻最大值:

-

-

典型值范围:

-

低速信号:10kΩ~100kΩ(低功耗场景)。

-

高速信号:1kΩ~4.7kΩ(如I²C总线)。

-

2. 功耗与速度的权衡

-

低功耗设计:选择大阻值(如100kΩ),但需接受较慢的上升沿。

-

高速设计:选择小阻值(如1kΩ),减少RC延迟,但增加静态功耗。

3. 内部上下拉电阻

-

现代MCU集成方案(如STM32、ESP32):

-

可通过寄存器配置启用内部上拉或下拉电阻(典型值30kΩ~100kΩ)。

-

优点:简化PCB布局,减少元件数量。

-

缺点:阻值固定,无法适应特殊需求(如高速总线)。

-

四、常见问题与误区

-

是否需要同时使用上下拉电阻?

-

通常只需一种,同时使用可能导致电流冲突(如VCC与GND间形成分压)。

-

-

上拉电阻与限流电阻的区别

-

限流电阻用于保护电路(如LED串联电阻),而上拉电阻用于电平固定。

-

-

电平兼容性问题

-

若不同电源域的器件互联(如3.3V与5V),需注意上拉电压匹配,避免过压损坏。

-

五、实际案例解析

案例1:I²C总线通信失败

-

现象:I²C设备无法响应,示波器显示SCL/SDA电平未拉高。

-

诊断:未接或上拉电阻阻值过大(如100kΩ),导致上升时间过长。

-

解决:更换为4.7kΩ上拉电阻,并检查总线电容是否超标。

案例2:按键误触发

-

现象:MCU偶尔误检测到按键按下。

-

诊断:按键电路未接下拉电阻,引脚浮空受噪声干扰。

-

解决:增加10kΩ下拉电阻,或在代码中启用内部下拉

六、总结

上下拉电阻的核心目的是确保信号线的确定性和稳定性,具体作用包括:

-

消除浮空风险,防止误触发;

-

定义默认逻辑状态;

-

适配开漏/开集输出电路;

-

提升抗干扰能力。

实际设计中需根据信号速率、功耗和驱动能力综合选择阻值,并优先考虑是否可利用芯片内部上下拉资源以简化电路。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?