本章节对应手册中Chapter D3 Channel Signaling章节,详细阐述了ACE接口上的基本信道信令要求。以下是本章节包含的主要内容:

由于篇幅原因Channel Signal章节计划分为上下两篇内容,本片为ACE(AXI Coherency Extensions) 协议学习记录3:Channel Signaling(上),主要包含读写地址通道信号的描述。

目录

缓存行大小事务(Cache line size transactions):

3.1读/写地址通道信号

3.1.1共享域类型(Shareability Domain Types)

ACE协议引入了共享域的概念,它是指一组主设备(masters),用于确定在发起一致性或屏障事务时应该包括哪些其他主设备。ACE协议定义了四个级别的共享域:

- 非共享(Non-shareable):包含单一主设备的域。

- 内部共享(Inner Shareable):可以包含额外主设备的内部域。

- 外部共享(Outer Shareable):包含所有内部域中的主设备,并可能包含额外的主设备。

- 系统(System):包含系统中所有主设备的域。

系统域概述 -> 1.2.6.1域(domains)

表D3-1展示了ACE协议中读地址通道和写地址通道的共享域信号,这些信号由主设备(Master)发出,用于指示正在进行的读或写事务的共享域类型。

共享域信号

| 事务通道 | 信号 | 来源 | 描述 |

|---|---|---|---|

| 读地址通道 | ARDOMAIN[1:0] | 主设备(Master) | 指示读事务的共享域 |

| 写地址通道 | AWDOMAIN[1:0] | 主设备(Master) | 指示写事务的共享域 |

Note:

尽管在系统中可以存在多个非共享(Non-shareable)、内部共享(Inner Shareable)和外部共享(Outer Shareable)域,但每个域中包含的主设备(masters)必须有一个统一的定义。这意味着,无论在系统的哪个部分,属于特定共享域的主设备集合应该是一致的,以确保缓存一致性和事务的正确处理。

AxDOMAIN[1:0]信号(ARDOMEN或AWDOMAIN信号)的编码方式,定义了共享域的不同级别:

0b00:非共享(Non-shareable)域,表示不与其他主设备共享缓存行。0b01:内部共享(Inner Shareable)域,表示内部共享的一组主设备之间可以共享缓存行。0b10:外部共享(Outer Shareable)域,表示包含内部共享域的所有主设备,并可能包括更多主设备。0b11:系统(System)域,表示系统中所有主设备之间的共享。

在ACE协议中,针对不同内存类型的事务,共享域的使用受到特定的限制:

-

设备事务(Device transaction):当

AxCACHE[1]信号等于零时,表示该事务为设备事务,它必须仅使用系统级别(System level)的共享域。这意味着,设备事务不涉及缓存一致性操作,而是直接与系统内存进行交互。 -

可缓存事务(Cacheable transaction):当

AxCACHE[3:2]信号不等于零时,表示该事务为可缓存事务,它不能使用系统级别的共享域。可缓存事务涉及缓存行的共享和一致性管理,因此需要在较低级别的共享域(如内部共享或外部共享)中进行处理。

这些限制确保了系统能够根据事务的类型和内存访问的缓存属性,正确地管理和维护缓存一致性。通过这种方式,系统可以优化性能,避免不必要的缓存一致性检查,同时确保数据的一致性和完整性。

AxCACHE是AXI4协议中写地址通道(Write Address Channel)和读地址通道(Read Address Channel)的信号的一部分。这个信号用于指定事务的缓存属性,如缓存的使能状态和缓存策略。在AXI4接口中,AxCACHE通常是一个4位的字段,但在某些情况下可能会被缩减到2位或3位,具体取决于实现的需要。

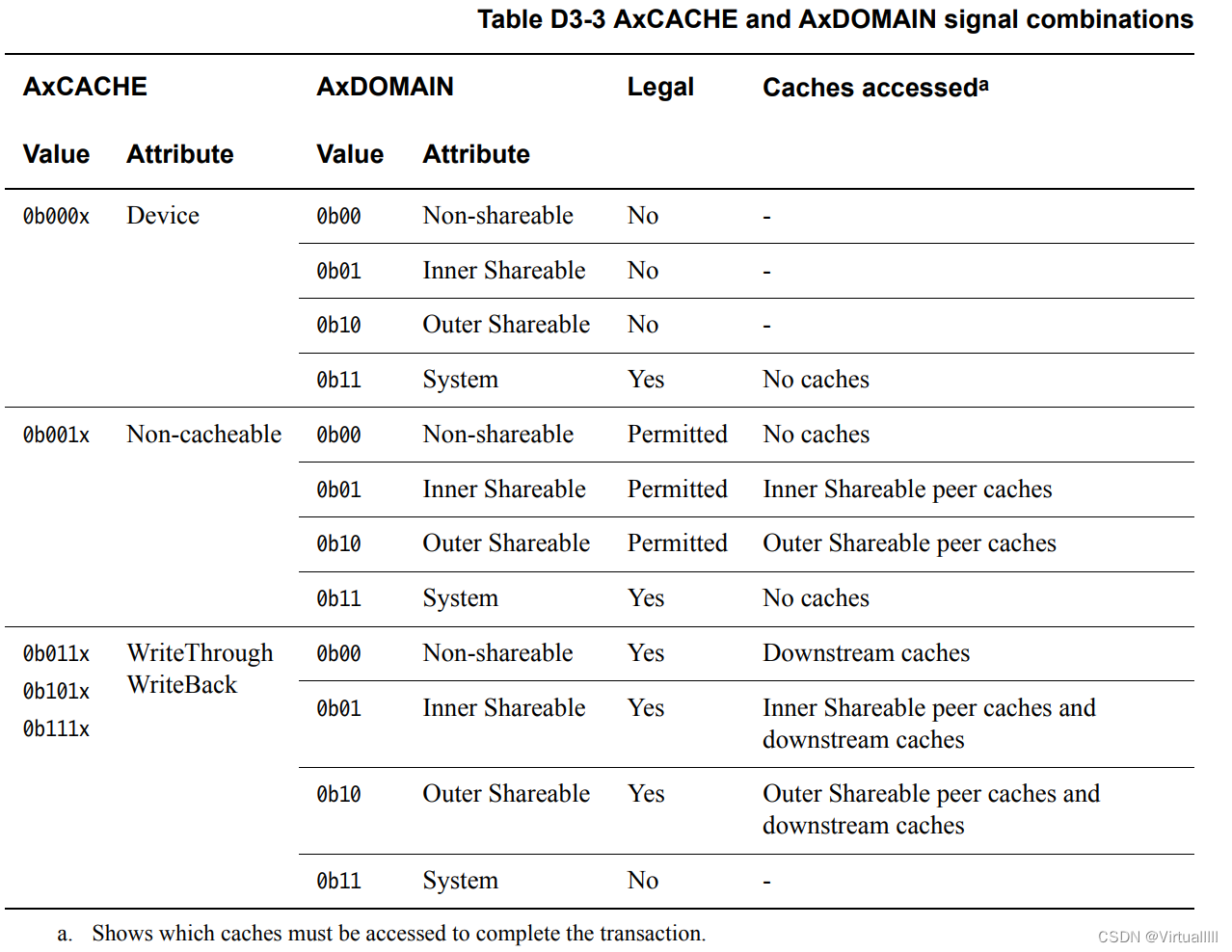

AxCACHE和AxDOMAIN信号组合

-

本地缓存访问的排除:表D3-3不包括发起主设备(initiating master)内部缓存的访问。这意味着表中描述的缓存访问仅涉及主设备之外的缓存。

-

允许但非预期的组合:表中标记为“允许”(Permitted)的

AxCACHE和AxDOMAIN组合在协议中是合法的,但并不常见。这些组合可以在内存位置可以在需要监听的域级别被缓存,但事务故意不在下游缓存时使用,例如在系统级缓存中。 -

非缓存事务的数据获取:当

AxCACHE指示为非缓存(Non-cacheable)且AxDOMAIN指示为内部共享(Inner Shareable)或外部共享(Outer Shareable)时,不要求必须从最终目的地获取数据。这可能适用于某些特殊的缓存策略或事务类型。 -

外部共享对等缓存的包含:当表D3-3显示访问的缓存是外部共享对等缓存时,这包括所有内部共享对等缓存。这意味着在处理外部共享事务时,也考虑了内部共享缓存的影响。

-

系统域内存位置的缓存限制:被指示为在系统域(System domain)的内存位置不能被任何缓存持有。这通常意味着系统域内存位置需要直接访问,不允许缓存介入,以确保一致性和可预测性。

拓展:总线协议、总线、控制器三者之间的关系

AXI总线协议:

AXI(Advanced eXtensible Interface)是由ARM公司定义的一种高性能、高带宽、低延迟的片上总线协议。它规定了在SoC(System on Chip)中不同IP核之间进行数据传输和通信的规则和标准。

AXI协议包括多个版本,如AXI3和AXI4,每个版本都有其特定的特性和改进。这些协议定义了信号集、事务类型、传输模式等,以支持复杂的数据传输需求。

总线:

- 总线是SoC中用于连接不同IP核的物理或逻辑通道,它实现了AXI协议中定义的数据传输。总线可以是物理的电气连接,如铜线或光导纤维,也可以是逻辑上的通信路径,如通过软件定义的通信接口。

- 总线的主要作用是传输数据、地址、控制信号等,使得SoC中的处理器、内存、外设等组件能够相互通信和协作。

控制器:

- 控制器是指管理和协调总线上数据传输的硬件或软件组件。在AXI协议中,控制器可以是一个独立的硬件IP核,也可以是集成在其他IP核中的控制逻辑。

- 控制器负责处理AXI事务,如发起读/写请求、处理响应、维护缓存一致性、执行事务的分割和合并等。它还可能包括地址翻译、优先级管理、错误处理等功能。

- 在某些设计中,控制器可能是可配置的,允许设计者根据系统需求来定制其行为,例如通过设置

AxCACHE信号来决定事务的可修改性。总结来说,AXI总线协议定义了SoC中数据传输的规则,总线是实现这些规则的物理或逻辑通道,而控制器是执行和管理这些规则的组件。这三者共同工作,确保了SoC中的数据能够高效、可靠地在不同组件之间传输和处理。设计者需要根据AXI协议来设计和集成总线和控制器,以实现所需的系统性能和功能。

扩展:ACE协议中提到的互连(interconnect)概念的理解

在AXI总线架构中,互连(interconnect)通常指的是连接不同IP核的中介网络或硬件组件,它实现了总线的功能,允许数据在SoC中的各个部分之间流动。互连可以被视为总线的一种实现,或者是总线概念的一个扩展。

互连的角色和功能包括:

数据传输:互连负责在SoC的不同组件之间传输数据,包括处理器、内存、外设等。

事务管理:互连管理AXI事务,包括读、写、响应等,确保事务按照AXI协议的规定正确地进行。

缓存一致性:在多缓存的SoC设计中,互连负责维护缓存一致性,处理缓存行的替换、无效化、合并等操作。

冲突解决:互连处理多个事务同时发生时可能出现的冲突,例如,当多个事务尝试访问同一内存位置时,互连需要决定事务的执行顺序。

桥接:互连可以作为不同总线标准或协议之间的桥梁,允许它们之间进行通信。

优化:互连可以根据系统的需求和性能目标对事务进行优化,例如,通过调整事务的突发长度或合并多个小事务来提高总线效率。

在理解上,互连可以被视为SoC设计中的一个枢纽,它不仅提供了物理连接,还包含了逻辑控制和优化机制,使得系统能够高效地运行。互连的设计和实现对于整个SoC的性能和可靠性至关重要。设计者需要确保互连能够支持AXI协议的所有特性,并根据具体的应用场景进行优化。

扩展:互连(interconnect)和总线控制器

互连(interconnect)和总线控制器(bus controller)是相关但不完全相同的概念。在SoC设计中,它们的关系和区别如下:

互连(Interconnect):

- 互连是指连接SoC内部各个IP核的硬件架构,它提供了数据和控制信号的传输路径。

- 互连可以包括多个层次和不同类型的总线,如AXI、AHB、APB等,它们共同构成了SoC的通信骨架。

- 互连的设计关注于优化数据流、减少延迟、提高带宽和确保事务的顺利进行。

总线控制器(Bus Controller):

- 总线控制器通常是指管理总线上事务的硬件组件或逻辑单元,它负责生成和控制事务,如发起读/写请求、处理响应、维护事务顺序等。

- 总线控制器可以是互连的一部分,或者是作为独立IP核存在的,它负责执行AXI协议中定义的控制逻辑。

在某些情况下,互连和总线控制器可能是集成在一起的,特别是在一些简化的设计或集成度较高的SoC中。在这种情况下,互连不仅提供了物理连接,还集成了控制逻辑,从而实现了总线控制器的功能。

总的来说,互连是SoC中连接不同组件的硬件架构,而总线控制器是管理这些连接上事务的硬件或逻辑单元。两者共同工作以确保数据在SoC中的有效传输和系统的稳定性。在设计SoC时,需要综合考虑互连和总线控制器的设计,以实现最佳的性能和功能。

3.1.2屏蔽域类型(barrier)

在ACE协议中,每个地址通道都有自己的屏障事务信号(barrier transaction signal),用于控制事务的顺序和确保数据的一致性。屏障事务是一种特殊的事务类型,它用于在系统中创建一个同步点,确保在此点之前的所有事务都已完成,从而为系统中的所有缓存和主设备提供了一个一致的观察点。

- 读屏障:用于确保在继续执行后续读事务之前,所有先前的读事务都已完成。

- 写屏障:用于确保在继续执行后续写事务之前,所有先前的写事务都已完成。

本文是ACE协议学习记录,聚焦读写地址通道信号。介绍了共享域类型、屏蔽域类型、共享事务类型等内容,阐述了信号组合、事务限制等要点。还扩展讲解了AXI总线协议、总线、控制器关系,以及互连和总线控制器概念,确保SoC数据高效传输。

本文是ACE协议学习记录,聚焦读写地址通道信号。介绍了共享域类型、屏蔽域类型、共享事务类型等内容,阐述了信号组合、事务限制等要点。还扩展讲解了AXI总线协议、总线、控制器关系,以及互连和总线控制器概念,确保SoC数据高效传输。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

501

501

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?