背景

- 基于Xilinx的7系列FPGA,

在通过文档《ug474_7Series_CLB.pdf》学习CLB过程中,

对7系列CLB中的多路复用器(Multiplexers)进行展开学习,遂就有了此文。

系列目录与链接

基于Xilinx的7系列FPGA,笔者在对CLB进行学习、研究时,归纳并总结出了以下博文:

1、分篇1:《7系列 之 查找表(Look-Up Table,LUT)》

2、分篇2:《7系列 之 存储单元(Storage Elements)》

3、分篇3:《7系列 之 多路复用器(Multiplexers)》

4、分篇4:《7系列 之 进位逻辑(Carry Logic)》

5、分篇5:《7系列 之 分布式RAM(Distributed RAM)》

6、分篇6:《7系列 之 7系列 之 移位寄存器(Shift Registers)》

7、总纲 :《7系列 之 可配置逻辑块(7 Series Configurable Logic Block,CLB)》

说明1:本系列基于文档文档《ug474_7Series_CLB.pdf》而写,翻译和感悟,会出现中英文混合的情况。

说明2:虽然文中会出现一些原文的部分截图,但非常支持并推荐道友们去看原汁原味的官方文档

说明3:在查阅相关资料过程中,发现一些关于相关知识点的介绍零零散散,本系列会对其进行整合,力求详尽。

说明4:如果文章有误,欢迎道友们指出、讨论,笔者也会积极改正,希望一起进步!

文章目录

Ch.1: 多路复用器(Multiplexers)

多路复用器,即数据选择器,用来将N个输入通道的数据复用到一个输出通道上。

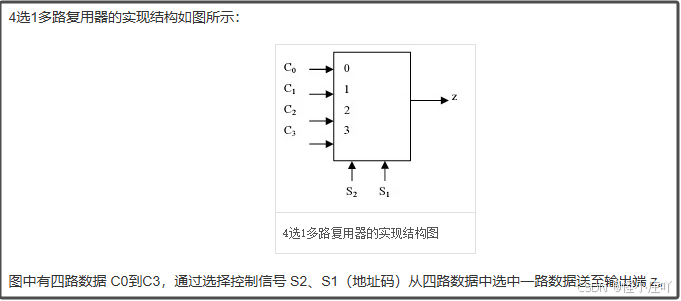

以4选1多路复用器(4:1 Multiplexer)为例,

4选1多路复用器(4:1 Multiplexer)的真值表,如下图所示:

多路复用器,作为组合逻辑器件,理论上完全可以通过LUT来实现。

Ch.2: 7系列中的多路复用器

如上图所示,7系列fpga中的每个Slice都包含3个多路复用器:F7AMUX,F7BMUX,F8MUX。

如上图所示,7系列fpga中的每个Slice都包含3个多路复用器:F7AMUX,F7BMUX,F8MUX。

2.1 ··· 4:1 Multiplexer

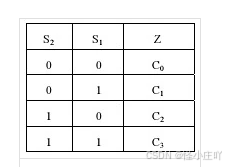

每个LUT6可以配置成4:1 MUX,

则一个 Slice中最多可以实现4个4:1 mux,如图2-21所示。

LUT6的6个输入:4个输入用于数据输入,2个输入用于选择。

LUT6的6个输入:4个输入用于数据输入,2个输入用于选择。

Verilog代码如下所示:

module Mux_top(

input s1,

input s0,

input D3,

input D2,

input D1,

input D0,

output reg O_mux

);

always @(*)begin

case({s1,s0})

2'b00 : O_mux = D0;

2'b01 : O_mux = D1;

2'b10 : O_mux = D2;

2'b11 : O_mux = D3;

default:;

endcase

end

endmodule

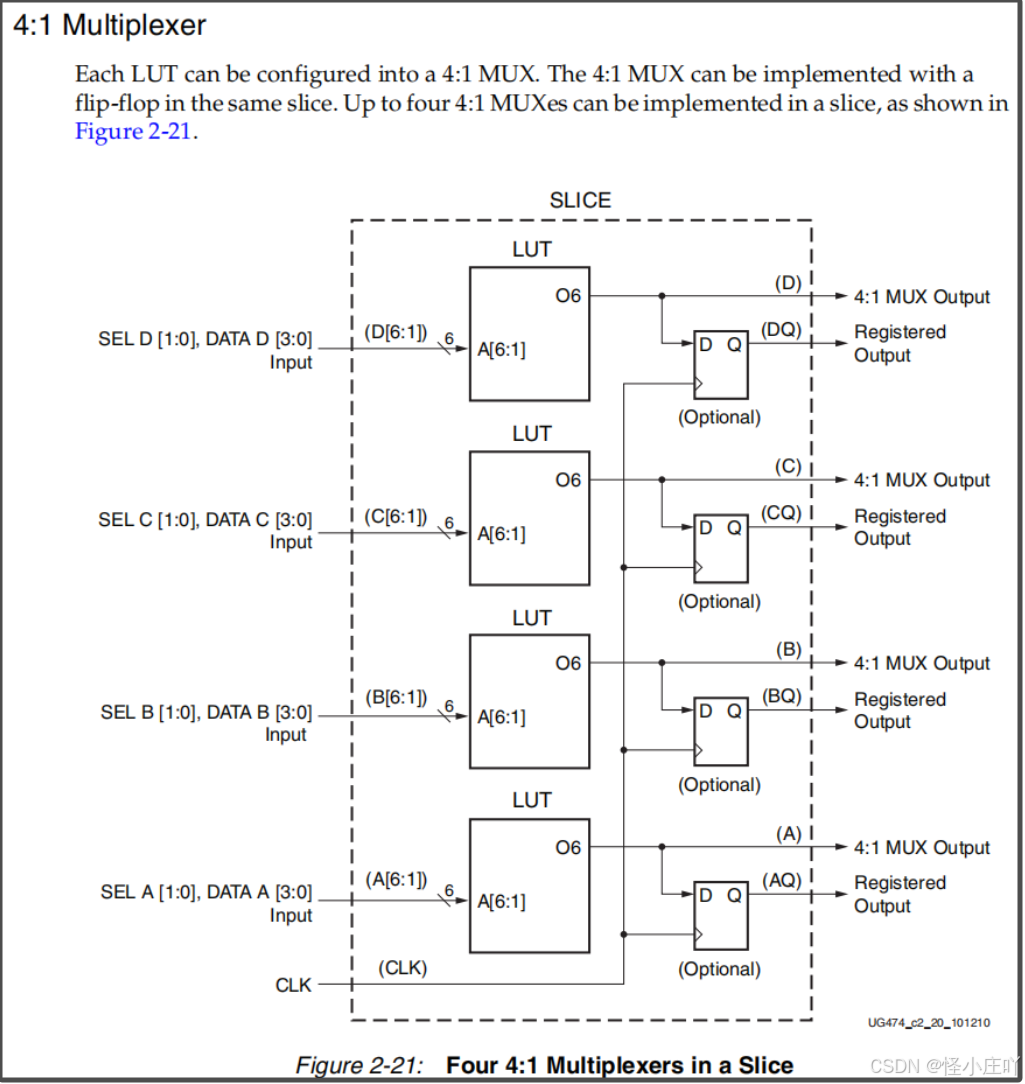

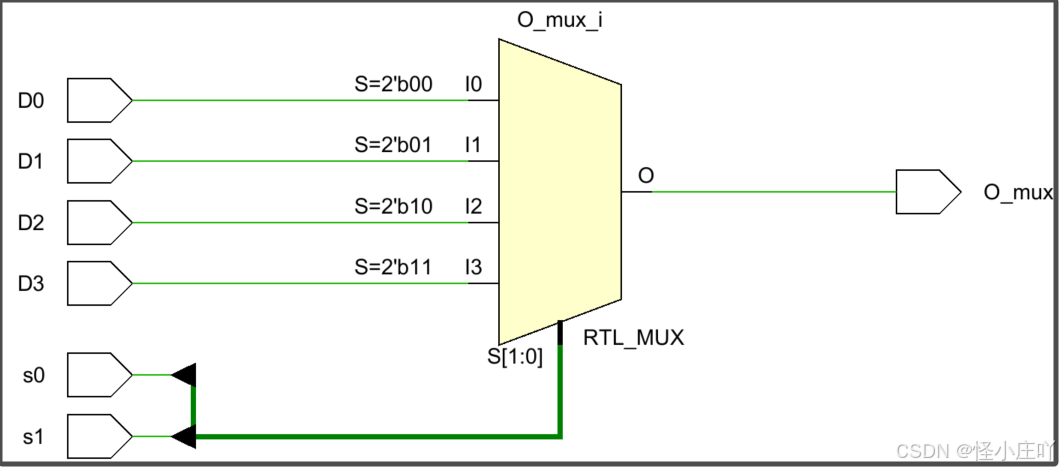

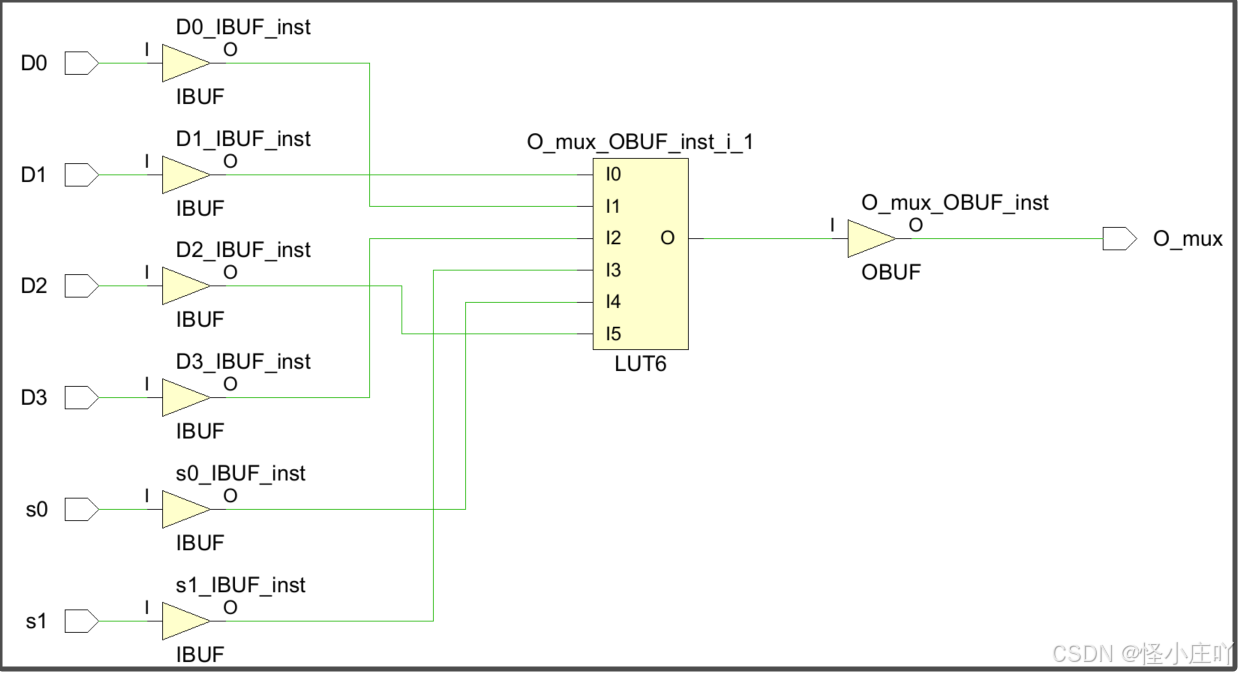

上述代码,RTL视图如下:

综合后的结果为:

果然,综合后的结果,4:1 MUX是用了LUT6来实现的。

果然,综合后的结果,4:1 MUX是用了LUT6来实现的。

LUT6可以被配置成4:1 MUX,

或者说,4:1 MUX的本质就是一个LUT6,

那么,2:1 MUX、3:1 MUX,也是可以通过LUT来实现。

但当Multiplexer需要选择的信号大于4时,LUT6就不能满足Multiplexer的需求了。

这时候,便需要使用Slice中包含3个的多路复用器了:F7AMUX,F7BMUX,F8MUX。

2.2 ··· 8:1 Multiplexer

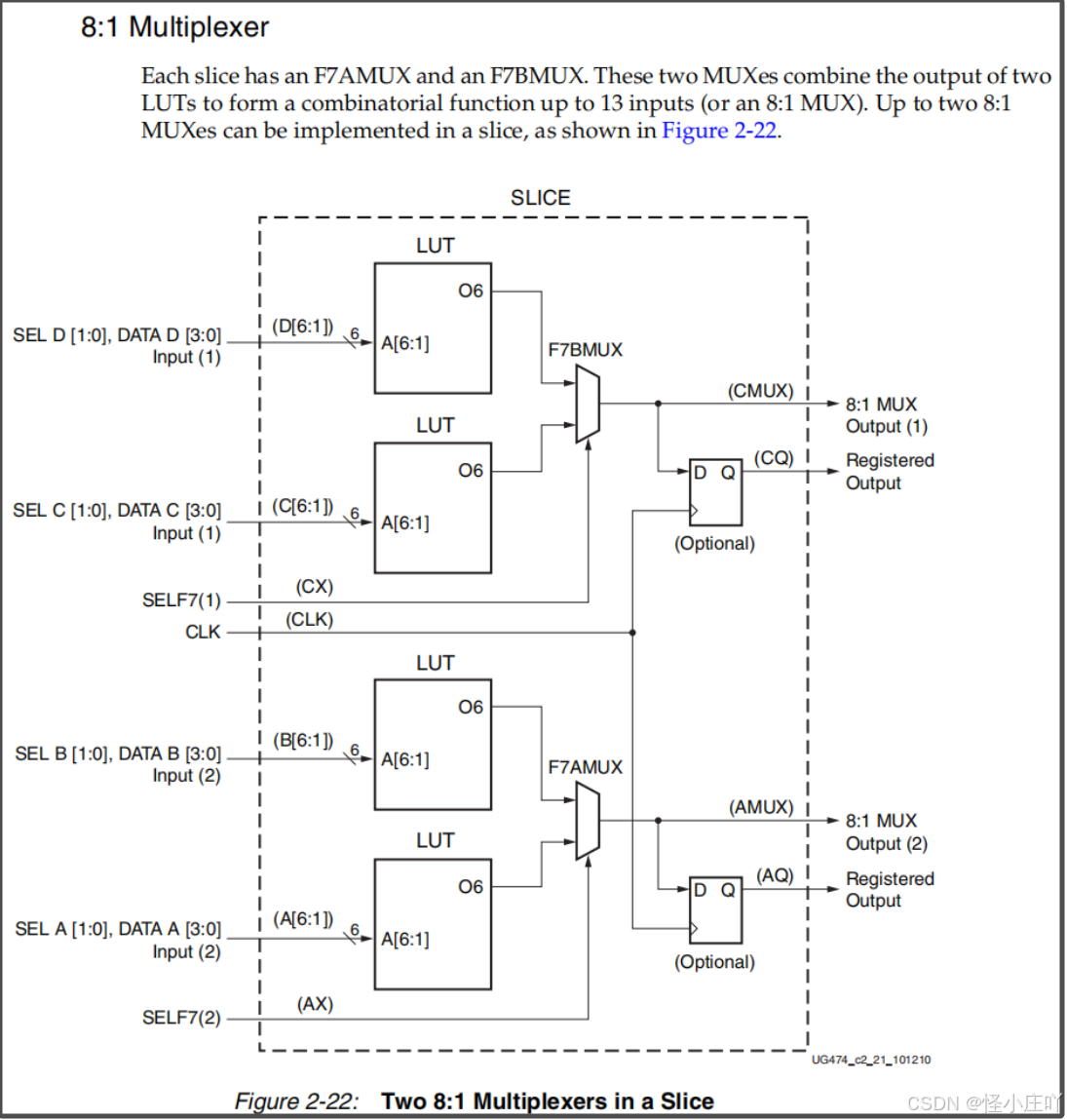

每个 Slice 有一个F7AMUX和一个F7BMUX。

这两个MUX可以将两个LUT的输出组合起来,形成13个输入的组合函数(或一个8:1 MUX)。

一个 Slice中最多可以实现2个8:1 mux,如图2-22所示。

Verilog代码如下所示:

module Mux_top(

input s2,

input s1,

input s0,

input D7,

input D6,

input D5,

input D4,

input D3,

input D2,

input D1,

input D0,

output reg O_mux

);

always @(*)begin

case({s2,s1,s0})

3'b000 : O_mux = D0;

3'b001 : O_mux = D1;

3'b010 : O_mux = D2;

3'b011 : O_mux = D3;

3'b100 : O_mux = D4;

3'b101 : O_mux = D5;

3'b110 : O_mux = D6;

3'b111 : O_mux = D7;

default:;

endcase

end

endmodule

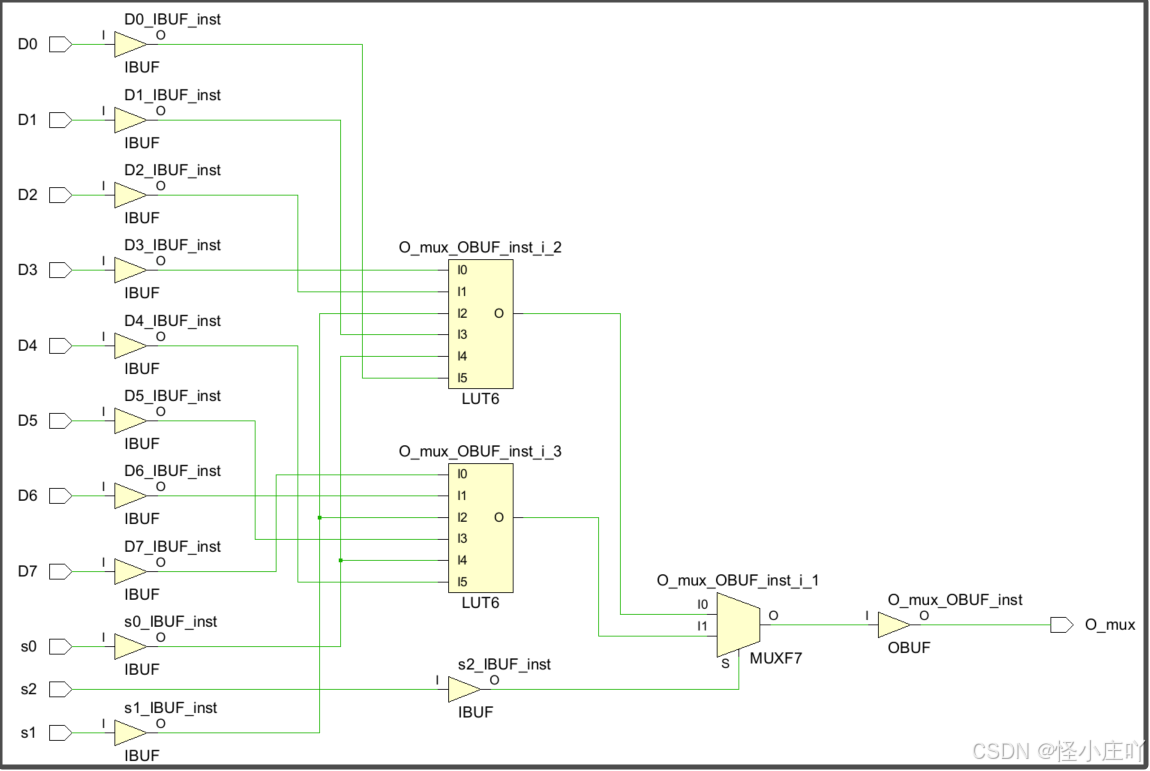

上述代码,综合后的结果为:

8:1 Multiplexer代码综合的结果就是 两个LUT6+一个MUXF7,

8:1 Multiplexer代码综合的结果就是 两个LUT6+一个MUXF7,

这与文档《ug474_7Series_CLB.pdf》中的说明一致。

2.3 ··· 16:1 Multiplexer

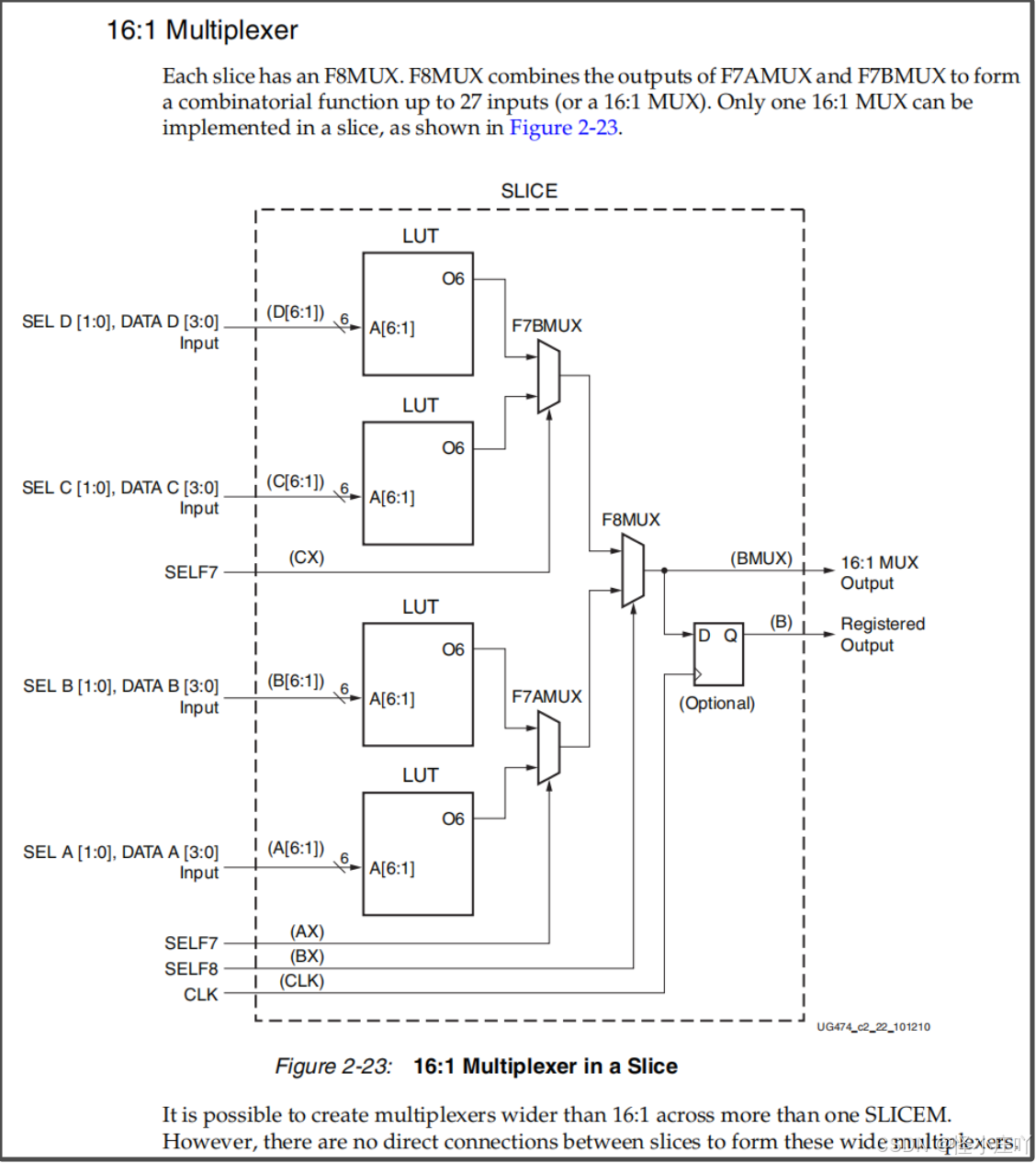

每个 Slice都有一个F8MUX。

F8MUX组合了F7AMUX和F7BMUX的输出,形成一个27个输入的组合函数(或一个16:1 MUX)。

一个切片中只能实现一个16:1的MUX,如图2-23所示。

Verilog代码如下所示:

module Mux_top(

input s3,

input s2,

input s1,

input s0,

input D15,

input D14,

input D13,

input D12,

input D11,

input D10,

input D9,

input D8,

input D7,

input D6,

input D5,

input D4,

input D3,

input D2,

input D1,

input D0,

output reg O_mux

);

always @(*)begin

case({s3,s2,s1,s0})

4'b0000 : O_mux = D0;

4'b0001 : O_mux = D1;

4'b0010 : O_mux = D2;

4'b0011 : O_mux = D3;

4'b0100 : O_mux = D4;

4'b0101 : O_mux = D5;

4'b0110 : O_mux = D6;

4'b0111 : O_mux = D7;

4'b1000 : O_mux = D8;

4'b1001 : O_mux = D9;

4'b1010 : O_mux = D10;

4'b1011 : O_mux = D11;

4'b1100 : O_mux = D12;

4'b1101 : O_mux = D13;

4'b1110 : O_mux = D14;

4'b1111 : O_mux = D15;

default:;

endcase

end

endmodule

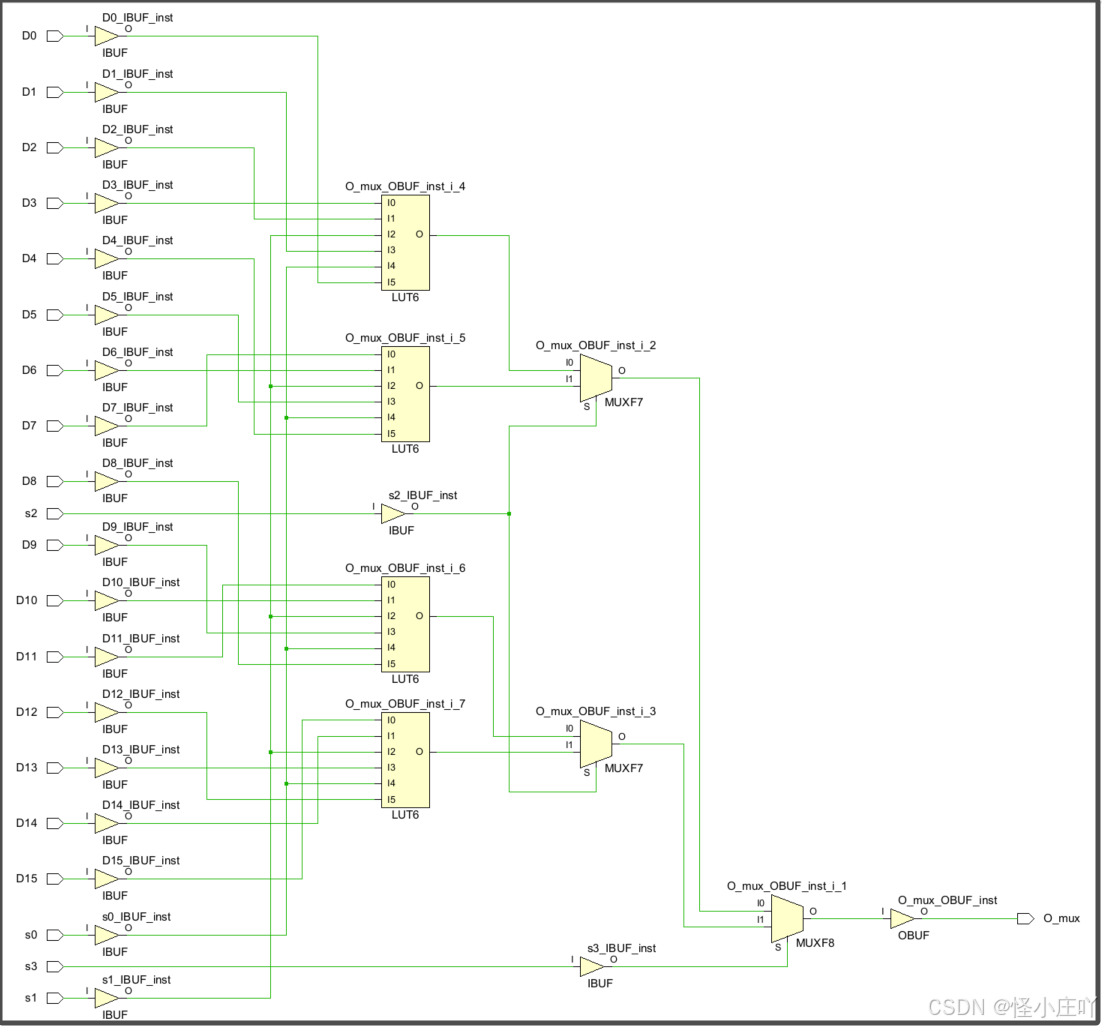

代码综合后的结果为:

毫无疑问,此处的代码综合结果也与文档《ug474_7Series_CLB.pdf》上的描述相一致。

毫无疑问,此处的代码综合结果也与文档《ug474_7Series_CLB.pdf》上的描述相一致。

2.5 ··· 16:1 Multiplexer的另一种设计思路

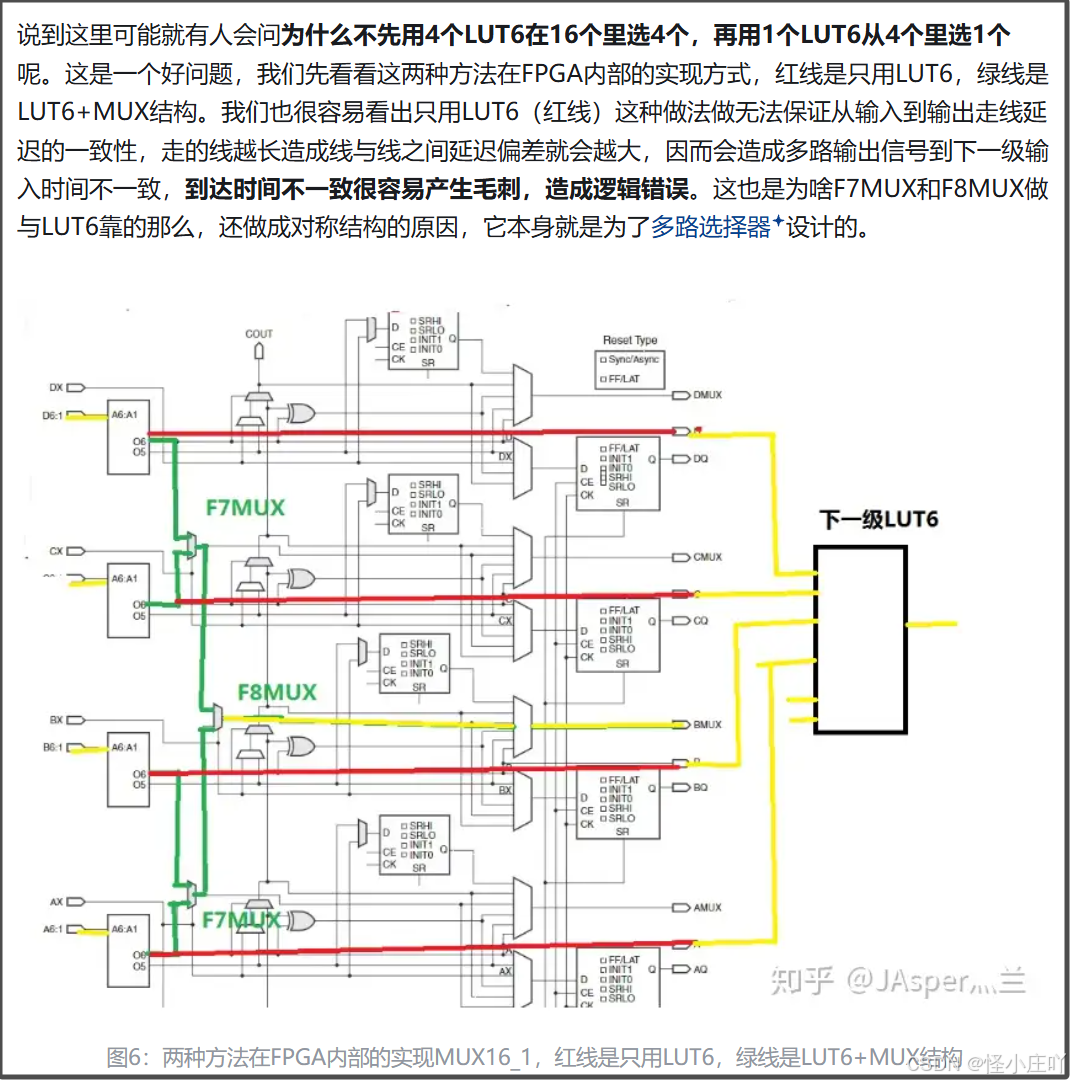

博客《FPGA从入门到精通(4) - MUX》有说到:

进而提出这么一个说法,如下图。

进而提出这么一个说法,如下图。

这与本文的第2.6章节内的第3点,倒是不谋而合。

这与本文的第2.6章节内的第3点,倒是不谋而合。

想到这里,不经感叹芯片结构之美妙、赛灵思底蕴之深厚。

2.6 ··· 后话

- 1、《ug474_7Series_CLB.pdf》上的一段原话:

”These wide input multiplexers are implemented in one level of logic (or LUT) using the dedicated F7AMUX, F7BMUX, and F8MUX multiplexers. These multiplexers allow LUT combinations of up to four LUTs in a slice. The wide multiplexers can also be used to create general-purpose functions of up to 13 inputs in two LUTs or 27 inputs in four LUTs (one slice). Although the multiplexer outputs are combinatorial, they can be registered in the CLB storage elements.“(《ug474_7Series_CLB.pdf》)

这些宽输入多路复用器是在逻辑(或查找表,LUT)的同一级使用专用的F7AMUX、F7BMX和F8MX多路复用器实现的。这些多路复用器允许在一个Slice中将多达4个LUT进行组合。这些宽多路复用器还可以用于创建最多13个输入的通用功能(两个LUT)或最多27个输入的通用功能(四个LUT,一个Slice)。尽管多路复用器的输出是组合逻辑,但它们可以在CLB存储单元中进行寄存。

-

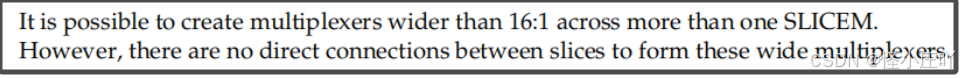

2、我们可以在多个 Slice上创建宽度大于16:1的多路复用器。

但是, Slice之间没有直接连接来实现这些 wide multiplexers。

“ 其实大家不难发现,我们在Slice中实现MUX,最基本的就是依靠LUT,当一个LUT不够满足我们的需求的时候,就通过fpga中的MUX把LUT两两组合起来构成更大规模的MUX。这样设计的一大好处就是可以使得整体的结构具有对称性,这样各个模块之间走线的延迟可以尽可能趋于一致,可以避免很多时序上的问题。”

“ 通过本文,我们知道了在fpga中实现MUX时可以使用的资源有MUX和LUT,但是还有一个问题,既然我们可以用LUT来实现MUX的功能,为什么不直接全部采用LUT呢,例如MUX8可以用2个LUT+一个MUX实现,理论上也可以用2个LUT+1个LUT实现。

之所以在fpga中还保留MUX这个设计,首先就是成本问题。MUX在数字电路中的使用频率是很高的,而MUX器件是一种晶体管较少的逻辑单元,通常查找表存储逻辑函数所需的逻辑资源以及控制连接的存储单元要消耗大量的晶体管,所以MUX在这方面有着巨大的优势。同样的用LUT来实现MUX也会造成资源的浪费。”

但是我们知道MUX2是可以用LUT6来实现的,也就是说 2个LUT6 + 1个MUXF7可以转换成2个LUT6 + 1个LUT6来实现MUX8;而4个LUT6 + 2个MUXF7+1个MUXF8可以转换成4个LUT6 + 1个LUT6来实现。那么既然LUT6可以实现MUX2的功能,FPGA里为何还要有固定的MUX这种结构?

首先可以肯定的是用LUT6来实现MUX2的效率没有固定MUX2的效率高,因为有两个输入没有利用就意味着有资源是浪费的。其次,每个SLICE中只有4个LUT6,如果只用LUT6来实现MUX16则需要5个LUT6,那么第5个LUT6则势必会布线到其他Slice,这样就容易造成不好布线和拥堵,且4个LUT6的输出分别到达第五个LUT6的时间会不同,到达时间不一致则容易产生毛刺。

参考文献

1、《ug474_7Series_CLB.pdf》

2、《FPGA原理与结构(4)——数据选择器MUX(Multiplexers)》

3、《从底层结构开始学习FPGA(4)----MUX多路选择器(Multiplexer)》

4、《FPGA从入门到精通(4) - MUX》

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?