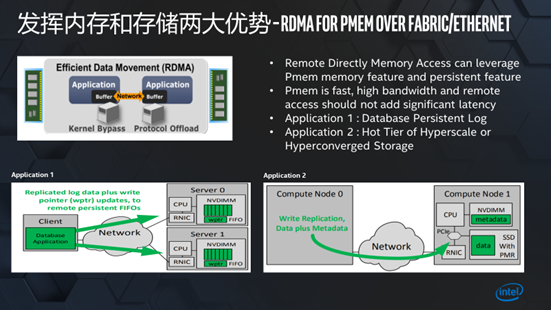

Optane PMem 融合了内存和存储这两个不同的概念的特征,在一个物理介质上得到了体现,为革命性的突破内存和存储编程概念提供了物质基础。

Optane PMem的延迟约在250ns~500ns,使持久性存储进入纳秒时代。

作为一种大容量的内存形态的存储设备,Optane Pmem 能提供10倍于DRAM 内存的容量密度。可以让更多的数据更靠近CPU,顺应了内存计算的潮流。

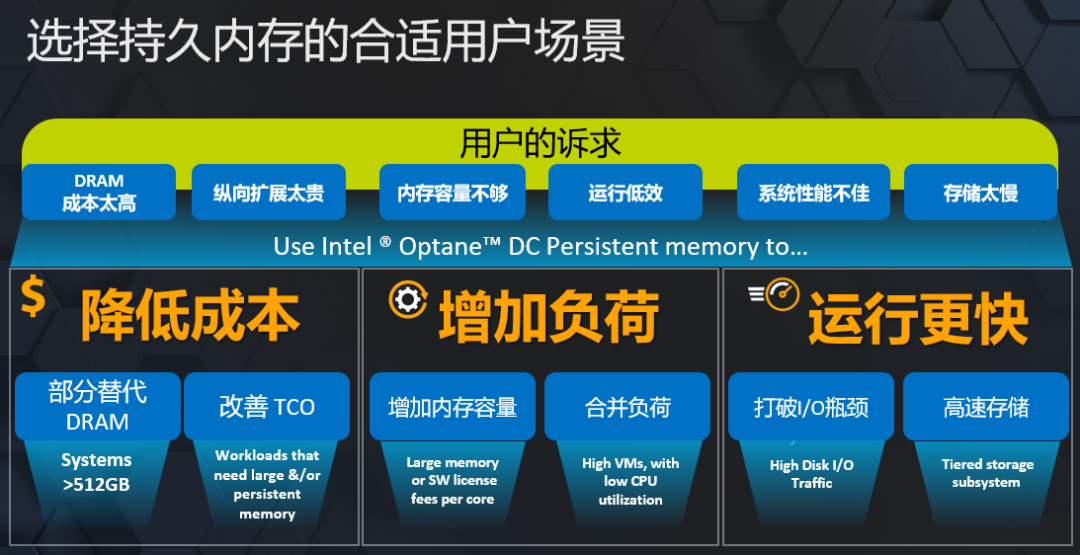

Optane单价贵,但value更多,可以帮助降低TCO

替代NAND PCIe简单,但用好并充分发挥Optane特性不简单。大多数客户都是分步走,小步快跑:短期在现有应用场景下优化;同时着眼中长期架构创新来充分发挥Optane各项优势

Optane SSD主要优势:低延迟、性能一致性/QoS、高性能(特别是随机写)、高寿命、低成本(小容量,如用于log, boot等)。某个特定应用只需要发挥其中的一部分优势即可实现很好TCO收益。所以真正合适的价格评价方法是 $/IOPs, $/PBW等

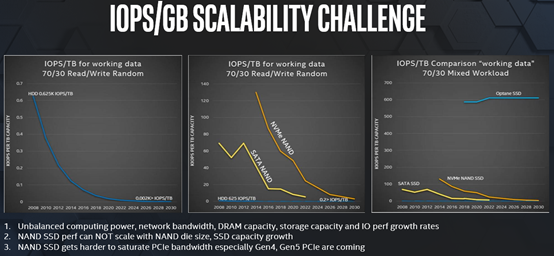

Optane SSD可以帮助NAND SSD实现更好的IOPs/TB扩展 – NAND本身的演进必然导致IOPs/TB的下降趋势 … 这样会导致CPU/network/storage能力扩展的不均衡,导致大量资源浪费

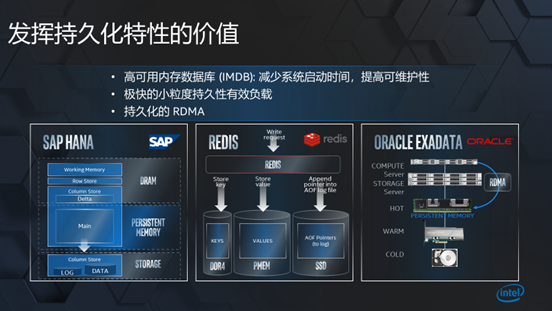

Optane可以加速应用创新

突破内存容量瓶颈,帮助用户增加服务器上的负荷,提升CPU利用率,实现更高的服务器系统的ROI

NAND演进的必然趋势:64L -> 96L -> 128/144L -> …; TLC -> QLC -> PLC … 这样才能更好地按照摩尔定律来增加容量、降低成本;如果只做其一,成本下降的趋势会逐渐收敛;必须两者兼顾

QLC/PLC等也可以开创全新的应用模式,而无需替代哪种技术

NAND die容量会不断变大(成本考虑),SSD容量也会不断增大(更加经济),小容量SSD性能会越来越差(NAND die少了,缺乏必要的并发性)

NAND SSD性能并不能很好地随容量增加而增加,需要创新的技术和方案来帮助 … Optane是当前的优选

QLC/PLC等是将来的发展趋势,并会逐渐替换HDD,但并不是简单的1:1替换,也不是一蹴而就的,需要循序渐进,并在平台、应用等方面的精耕细作

扫码入当当/京东直购《大话计算机》

扩展阅读

《大话计算机》序言⑦ by @去流浪

博主简介:冬瓜哥,《大话计算机》与《大话存储 终极版》、《大话存储 后传》图书作者。多项专利发明人。

现任某半导体公司高级资深架构师。

大话计算机 大话存储

大话计算机 大话存储

长按扫码可关注

OptanePMem融合内存与存储特性,提供低至纳秒级延迟的大容量存储,单价虽高,但能显著降低TCO。OptaneSSD优势明显,包括低延迟、性能一致性、高寿命及低成本,有助于NANDSSD实现更好的IOPs/TB扩展,加速应用创新,突破内存容量限制。

OptanePMem融合内存与存储特性,提供低至纳秒级延迟的大容量存储,单价虽高,但能显著降低TCO。OptaneSSD优势明显,包括低延迟、性能一致性、高寿命及低成本,有助于NANDSSD实现更好的IOPs/TB扩展,加速应用创新,突破内存容量限制。

3872

3872

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?