Quartus三种方式实现D触发器及时序仿真

一、D触发器

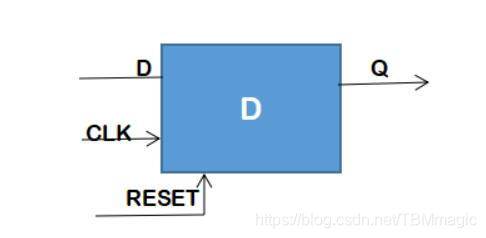

(一)D触发器结构

D触发器由四个管脚(输入信号D,输出信号Q,时钟信号CLK及复位信号RESET)组成

其功能是当RESET为低电平(0),Q处于低电平状态;当RESET为高电平(1),通过观察CLK状态,当CLK信号由0变1(上升沿)的时候,若D为低电平,Q就为低电平,若D为高电平,Q就为高电平。

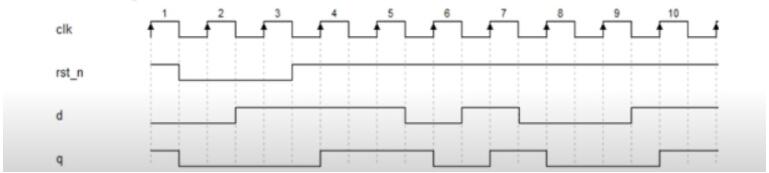

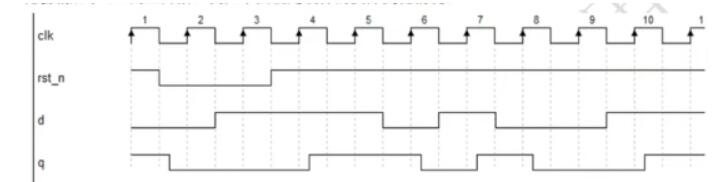

(二)D触发器的波形图

初始状态:

设置复位信号(rst_n)为1,d为0,q为1

变化过程:

rst_n为0的时候,q的值始终为0;rst_n为1的时候,当clk由0变为1,q的值根据d值而发生变化(值同)

q值发生变化的时候,存在一定的延时(上升沿的时候q的值为变化之前的值)

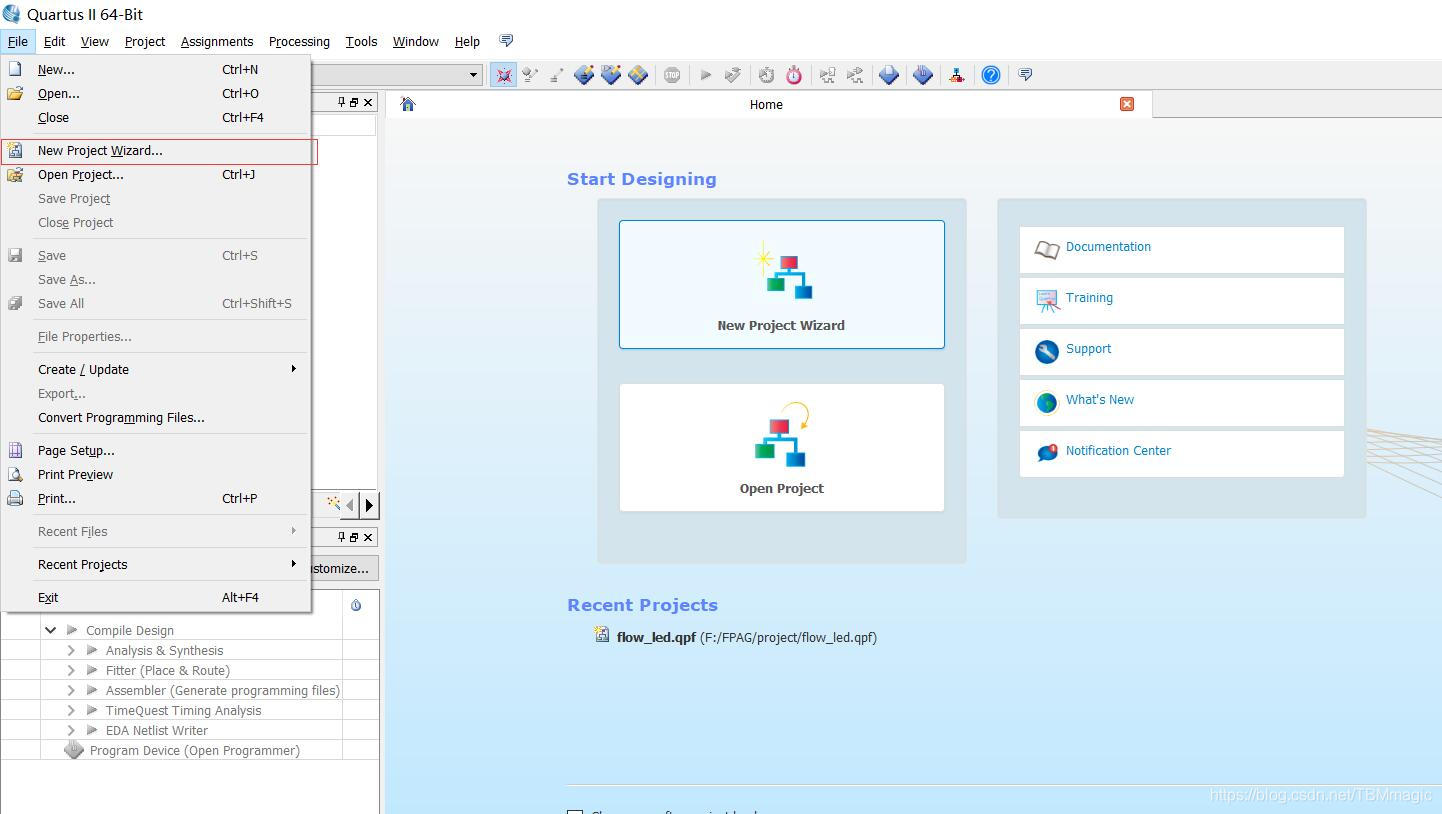

二、Quartus输入原理图及时序仿真

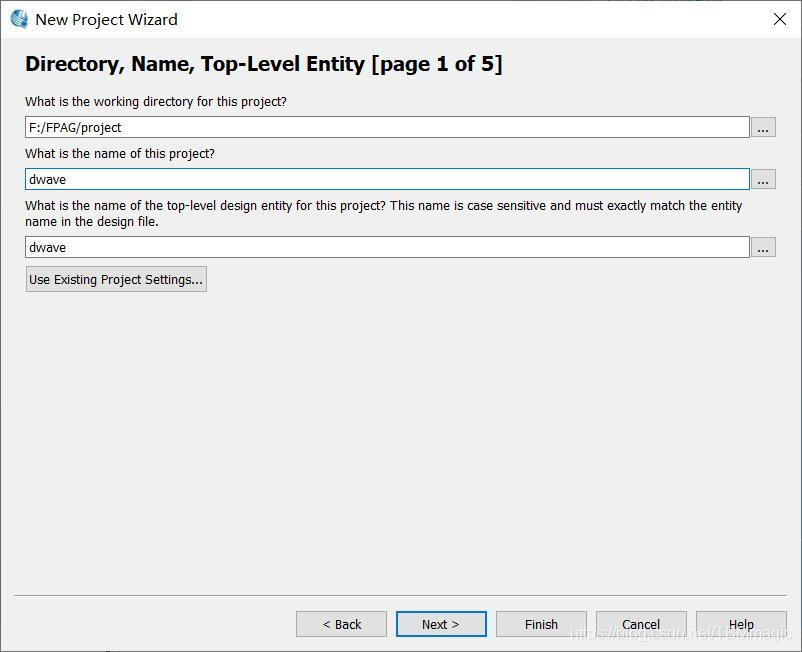

(1)创建工程

填写工程名称

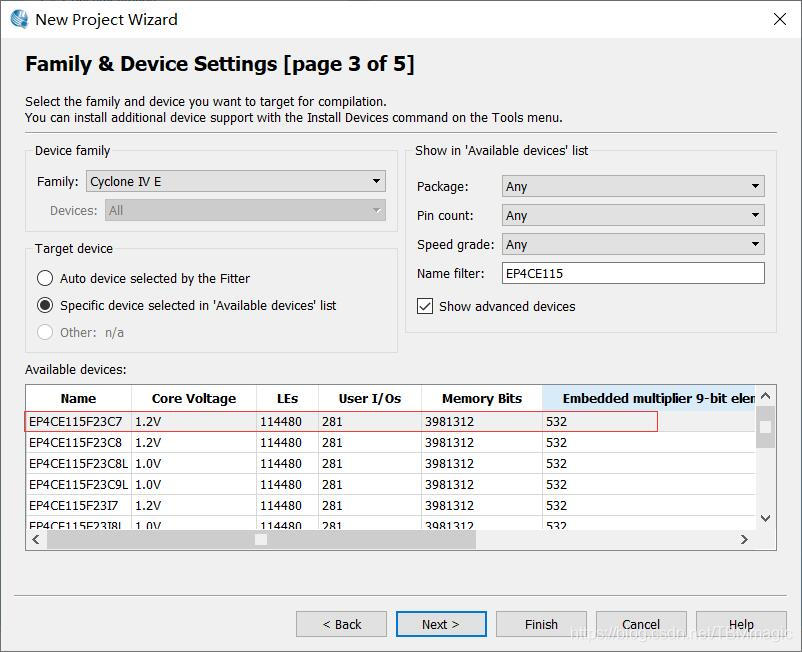

选择芯片系列及类型

一路Next完成工程创建

(2)创建方框文件

File->new->Block Diagram/

本文详细介绍了如何在Quartus中通过输入原理图、调用D触发器模块以及使用Verilog语言实现D触发器,并进行时序仿真。涵盖了从工程创建、方框图设计、编译到波形文件生成和仿真全过程。

本文详细介绍了如何在Quartus中通过输入原理图、调用D触发器模块以及使用Verilog语言实现D触发器,并进行时序仿真。涵盖了从工程创建、方框图设计、编译到波形文件生成和仿真全过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1834

1834

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?