u-boot 源码版本:u-boot-2017.05-rc2

u-boot文件介绍

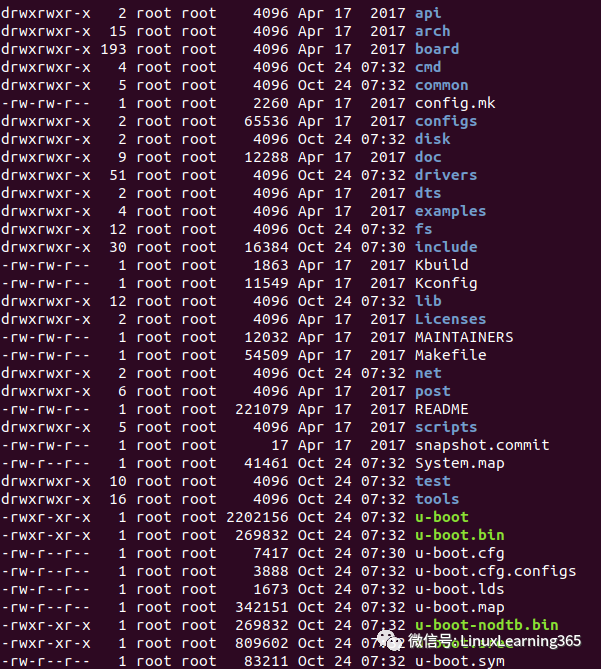

u-boot源码中文件内容如下:

针对有代表性的文件,我们简单介绍其功能

config.mk文件

是一个Makefile文件,在某个Makefile中会去调用它Makefile文件

这个是uboot源代码的主Makefile,将来整个uboot被编译时就是用这个Makefile管理编译的。api文件夹

硬件无关的功能函数的API。uboot移植时基本不用管,这些函数是uboot本身使用的。arch

与处理器相关的文件。cmd

u-boot命令文件,uboot中的命令都在该部分中。common

这个文件夹下放的是一些与具体硬件无关的普遍适用的一些代码。譬如控制台实现、crc校验的。但是更多的主要是两类:一类是cmd开头的,是用来实现uboot的命令系统的;另一类是env开头的,是用来实现环境变量的。configs

configs文件夹:存放uboot配置文件,一般半导体或开发板厂商会制作好一个配置文件,供用户在此基础上进行修改,配置文件统一命名为“xxx_defconfig”,xxx表示开发板名字。

使用"make xxx_defconfig"命令,即可配置uboot。fs

文件系统:FAT、JFFS2、EXT2等net

网络协议:NFS、TFTP、RARP、DHCP等等tools

编译S-Record或U-Boot映像等相关工具,制作bootm引导的内核映像文件工具mkimage源码就在此disk

磁盘驱动的分区处理代码drivers

包含几乎所有外围芯片的驱动,网卡、USB、串口、LCD、Nand Flash等等include

头文件,包括各CPU的寄存器定义,文件系统、网络等等lib

公用库函数u-boot

初步链接后得到的uboot文件u-boot-nodtb.bin

在u-boot的基础上,经过objcopy去除符号表信息之后的可执行程序u-boot.bin

在需要dtb的情况下,直接由u-boot-dtb.bin复制而来,也就是编译u-boot的最终目标u-boot.lds

uboot的连接脚本System.map

连接之后的符号表文件u-boot.cfg

由uboot配置生成的文件

uboot第一启动阶段

/*

* set the cpu to SVC32 mode

*/

//设置cpu进入管理员模式,并且关闭FIQ和IRQ

mrs r0, cpsr

bic r0, r0, #0x1f

orr r0, r0, #0xd3

msr cpsr, r0#ifdef CONFIG_S3C24X0

/* turn off the watchdog */

//关闭看门狗

# if defined(CONFIG_S3C2400)

# define pWTCON 0x15300000

# define INTMSK 0x14400008 /* Interrupt-Controller base addresses */

# define CLKDIVN 0x14800014 /* clock divisor register */

#else

# define pWTCON 0x53000000

# define INTMSK 0x4A000008 /* Interrupt-Controller base addresses */

# define INTSUBMSK 0x4A00001C

# define CLKDIVN 0x4C000014 /* clock divisor register */

# endif

ldr r0, =pWTCON

mov r1, #0x0

str r1, [r0]/*

* mask all IRQs by setting all bits in the INTMR - default

*/

//设置所有中断配置为默认配置

mov r1, #0xffffffff

ldr r0, =INTMSK

str r1, [r0]

# if defined(CONFIG_S3C2410)

ldr r1, =0x3ff

ldr r0, =INTSUBMSK

str r1, [r0]

# endif//跳转到CPU初始化处进行,在其中主要是执行 caches 的关闭 和 MMU的关闭,之后跳转到

//lowlevel_init 中执行,进行系统总线的初始化。

#ifndef CONFIG_SKIP_LOWLEVEL_INIT

bl cpu_init_crit

#endif#ifndef CONFIG_SKIP_LOWLEVEL_INIT

cpu_init_crit:

/*

* flush v4 I/D caches

*/

mov r0, #0

mcr p15, 0, r0, c7, c7, 0 /* flush v3/v4 cache */

mcr p15, 0, r0, c8, c7, 0 /* flush v4 TLB */

/*

* disable MMU stuff and caches

*/

mrc p15, 0, r0, c1, c0, 0

bic r0, r0, #0x00002300 @ clear bits 13, 9:8 (--V- --RS)

bic r0, r0, #0x00000087 @ clear bits 7, 2:0 (B--- -CAM)

orr r0, r0, #0x00000002 @ set bit 1 (A) Align

orr r0, r0, #0x00001000 @ set bit 12 (I) I-Cache

mcr p15, 0, r0, c1, c0, 0

#ifndef CONFIG_SKIP_LOWLEVEL_INIT_ONLY

/*

* before relocating, we have to setup RAM timing

* because memory timing is board-dependend, you will

* find a lowlevel_init.

本文介绍了u-boot源码的主要文件结构和启动阶段。config.mk用于Makefile调用,主Makefile负责整个编译过程。在硬件层面,涉及arch目录的处理器相关代码,cmd目录包含命令文件,common目录包含通用代码。启动阶段,lowlevel_init关闭缓存并初始化,board_init_f进行硬件初始化,board_init_r调用一系列初始化函数,最后run_main_loop执行命令行操作。

本文介绍了u-boot源码的主要文件结构和启动阶段。config.mk用于Makefile调用,主Makefile负责整个编译过程。在硬件层面,涉及arch目录的处理器相关代码,cmd目录包含命令文件,common目录包含通用代码。启动阶段,lowlevel_init关闭缓存并初始化,board_init_f进行硬件初始化,board_init_r调用一系列初始化函数,最后run_main_loop执行命令行操作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2198

2198

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?