ESD 保护元件─ 未来不可避免的设计任务

随着晶片功能高度整合与电晶体密度的提升,晶片本身对静电耐受度逐步降低。现在晶片对于静电的耐受程度,有些仅有约1kV~2kV的”元件等级”,此程度的耐受度仅可防止晶片于工厂内生产或产品整机制作中遭受静电破坏;在产品设计时,多数设计者会参照”系统等级”的IEC61000-4-2静电放电波形,来模拟产品在终端遇到的静电放电;此外,若产品使用于不稳定的环境中,如室外或电力设备不完善的地区,有些设计者会再额外参考IEC61000-4-5来模拟雷击耦合或带电插拔等持续时间更长的突波。

图 1. ESD测试方式与模拟情况

换言之,在测试要求不变甚至更严苛的情况下,晶片本身却逐渐脆弱,因此如何在不影响原有功能下,设计有效且经济的保护方案来提升系统对静电的耐受度就逐渐受到重视。

以下介绍静电防护方案从过去到现在的演变,及如何有效地挑选合适的静电保护元件。

Varistor ─ 静电防护的早期手段

以前的晶片并不像现在将许多功能整合在一起,相比之下,它制程线宽大,电晶体密度较低,且有足够的空间设计防护电路,因此有着更强大的自我保护能力;此外,较大的产品体积拉开了静电打入敏感线路的距离,加上以前产品多使用金属外壳,而金属外壳有效地宣泄静电能量,造就以前设计的产品对静电耐受本身就高,因此设计者在对外接口或晶片周围添加Varistor后,就可以有效的避免产品遭受静电破坏。

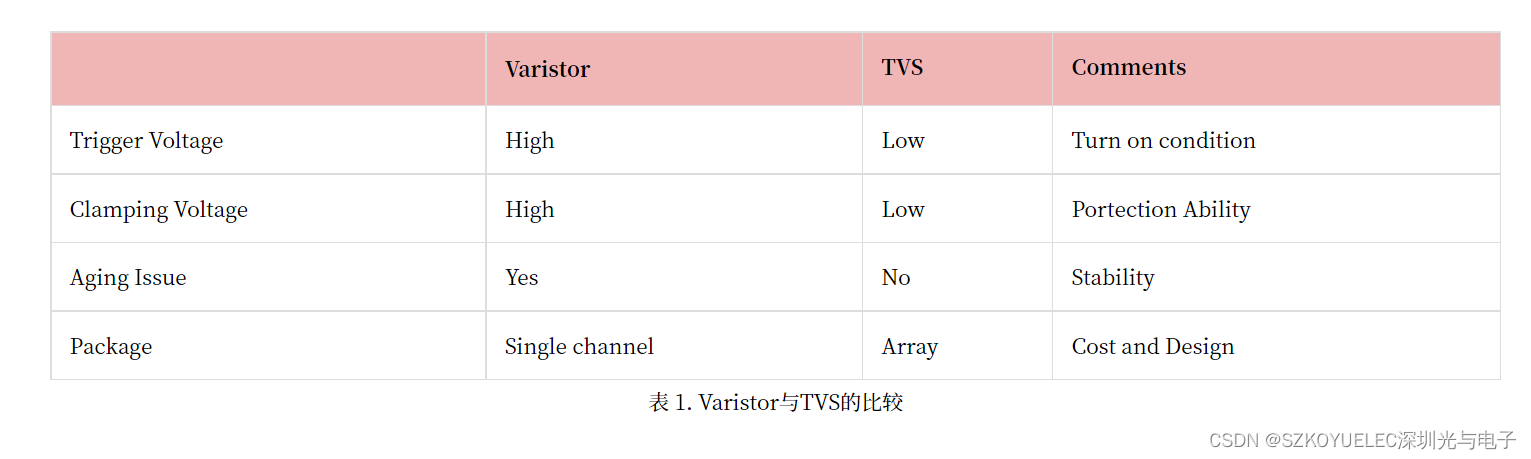

Varistor是一个透过材料特性,在面对过电压时产生导通路径的保护元件;然而,Varistor本身并不是一个理想的静电保护元件,因为材料特性导致它有老化现象,加上较高的启动电压与钳制电压,使得Varistor即使成功的启动,它所提供的保护能力却并不一定符合系统需求;但在产品本身良好放电路径与放电距离晶片较大的情况下,Varistor的保护能力在过去仍然被设计者采纳。

晶焱科技静电防护方案及TVS挑选指南

晶焱科技静电防护方案及TVS挑选指南

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

5万+

5万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?