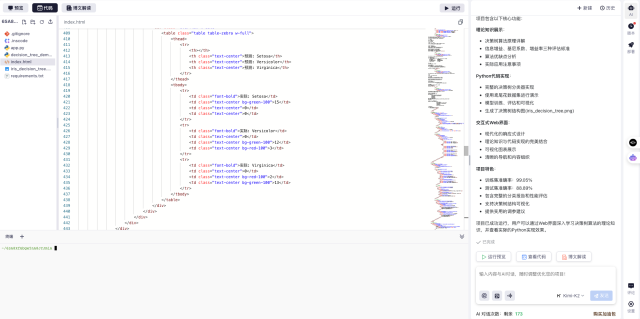

快速体验

- 打开 InsCode(快马)平台 https://www.inscode.net

- 输入框输入如下内容

帮我开发一个Cache直接相联映射模拟系统,用于计算机组成原理教学演示。系统交互细节:1.展示8行cache结构 2.支持主存地址输入 3.可视化命中/缺失判断过程 4.显示数据块传输动画。注意事项:需模拟二级存储器延迟效果。 - 点击'项目生成'按钮,等待项目生成完整后预览效果

实验核心要点解析

-

地址映射机制 直接相联映射的核心在于主存块与cache行的固定对应关系。实验中主存地址被划分为tag、index和offset三部分,其中index字段直接决定数据块存放的cache行号。这种设计使得查找时只需检查指定行的valid位和tag匹配情况,大幅简化了硬件电路。

-

硬件电路实现

- 使用3-8译码器将index字段转换为行选信号

- 通过三态门控制cache行的数据输出

- 比较器同时验证valid位和tag位判断命中

-

多路选择器根据offset选择数据块中的具体字

-

缺失处理流程 当发生缺失时,系统通过Miss信号触发二级存储器的块交换操作。这个设计模拟了真实CPU中cache与主存的交互过程,包括:

- 暂停地址计数器

- 等待多个时钟周期完成块传输

-

通过BlkReady信号通知数据就绪

-

性能优化关键 实验特别强调命中情况下的单周期响应能力,这正体现了cache在现代CPU中的核心价值。通过观察命中率数据,可以直观理解cache大小、映射方式对系统性能的影响。

实验难点突破

-

三态门控制逻辑 需要精确控制哪些cache行的数据可以输出到总线,确保只有命中行的数据能够被正确读取。这个环节容易因使能信号处理不当导致总线冲突。

-

时序同步问题 块交换过程中的多周期等待需要正确处理各模块的协调工作,特别是BlkReady信号与时钟信号的同步关系,这是保证数据完整写入的关键。

-

调试技巧 建议采用分模块验证法:

- 先单独测试地址译码功能

- 再验证命中判断电路

- 最后整合数据输出通路

扩展思考方向

- 如何修改设计支持组相联映射?

- 增加写操作支持需要考虑哪些额外逻辑?

- 不同块大小对命中率的影响如何量化分析?

平台使用体验

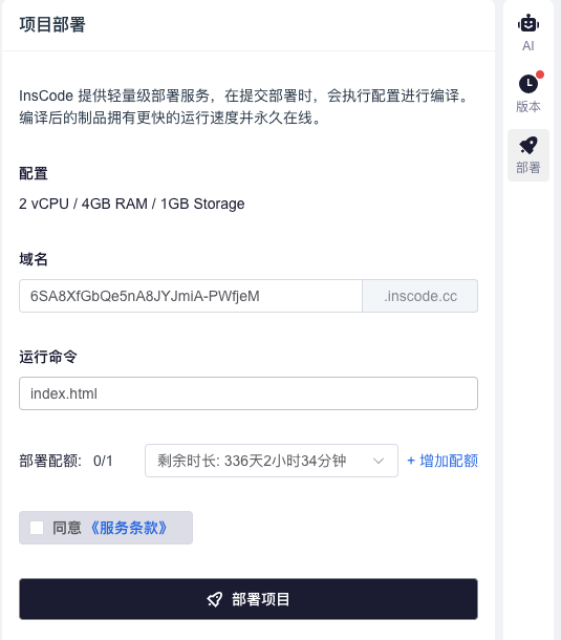

在InsCode(快马)平台上可以快速搭建这个实验的演示版本,无需安装Logisim等专业工具就能体验cache工作原理。平台的一键部署功能特别适合展示这种带有可视化交互的教学案例。

实际操作中发现,用自然语言描述需求就能生成基础框架,再通过内置编辑器微调细节非常高效。对于计算机组成原理这类需要直观演示的知识点,这种可视化方式比单纯看理论更容易理解。

创作声明:本文部分内容由AI辅助生成(AIGC),仅供参考

Cache直接相联映射实验解析

Cache直接相联映射实验解析

73

73

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?