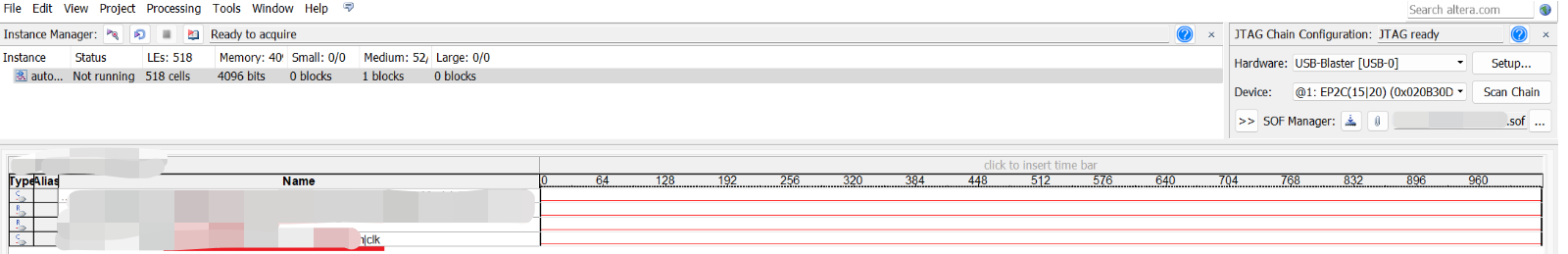

- 仿真结果与预期高度一致,在将模块代码汇总并进行在线调试时,发现时钟信号呈现为一条平直的直线。

- 经过多次对比分析,最终定位到以下错误代码内容:

// 边沿检测逻辑

wire btn_pressed = ~btn_sync_2 && btn_prev;

reg[15+1:0] data_reg;

// 更新按钮的前一状态

always @(posedge clk) begin

btn_prev <= btn_sync_2;

end

// wire clk;

// assign clk = CLKIN; // 将这两个注释取消才能得到正确结果

-

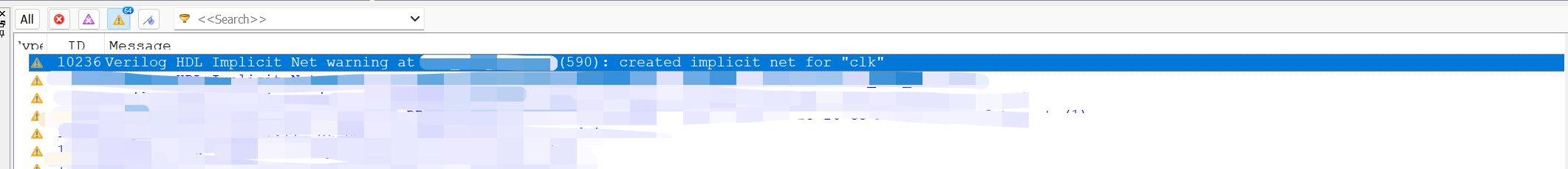

原来在多次的调试与修改中,注释掉了原来应有的变量clk,但是在进行综合时没有报错,只有如下警告:

-

Warning (10236): Verilog HDL Implicit Net warning at ***.v(590): created implicit net for “clk”

909

909

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?