1. 引言

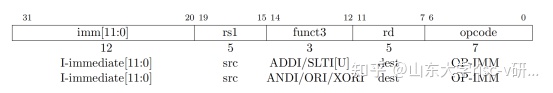

本篇主要简单介绍一下现代处理器的设计思想,方便对一些后续内容的更新与解释;首先任何处理器,处理信息的最小单位都是指令,换句话说无论是你双十一刚买的iPhone 14 pro max还是体重秤上日益膨胀的数据,靠的都是一条条辛苦耕耘的指令;一条RISC指令可以十分简化的划分为三部分(实际情况要复杂很多),分别是操作码,操作数,以及目的寄存器(地址);以一条加法指令来说,告诉计算机这是加法运算就是操作码,被加数和加数就是操作数,所得的结果最后放到目的寄存器里;为了后面介绍一些CPU的具体结构,这里将所有指令再简单粗暴的分为三大类分别是运算类的指令,load/store类指令,以及条件控制类指令(实际情况也复杂很多,下图是risc-v立即数加法的指令结构);

对于指令就先简单的介绍到这里,后续会展开介绍一下指令的在处理器内部的执行过程,感兴趣想深入了解可以自行下载risc-v指令集spec,下载地址放在文章末尾;再简单介绍一下经典的CPU结构;

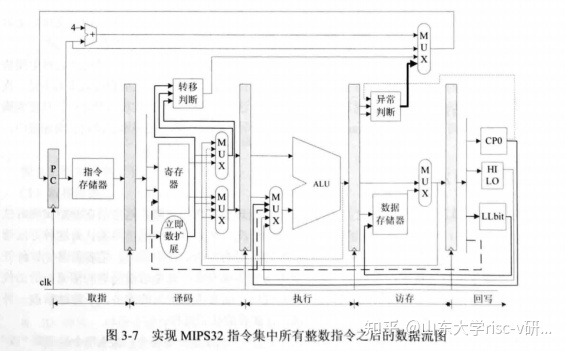

2. 经典五级流水线

经典五级流水线是由:取值,译码,执行,访存,写回五级流水构成;(下图为MIPS的经典五级流水)

由于risc-v中有单独的访存指令,在一般risc-v的处理器中,将访存操作(也就是上述所说的load、store指令)放到执行级里,所以一般的risc-v处理器架构可以简单理解为四部分,取指,译码,执行,写回;以一个单发射顺序哈弗架构的risc-v处理器来举例,取指就是从I-cache(或者其他的指令存储单元 ITCM等,I-cache中的指令是从FLASH回填进来的,这部分后面会展开将

本文介绍了现代处理器的设计思想,包括RISC-V指令结构、经典五级流水线、分支预测以及乱序执行的概念。讨论了超标量处理器如何通过乱序执行提高性能,并解决了数据相关性问题。同时,提到了Cache在多核处理器中的一致性问题及其作用。

本文介绍了现代处理器的设计思想,包括RISC-V指令结构、经典五级流水线、分支预测以及乱序执行的概念。讨论了超标量处理器如何通过乱序执行提高性能,并解决了数据相关性问题。同时,提到了Cache在多核处理器中的一致性问题及其作用。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1361

1361

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?