1、IIC读写时序

【注】数据传输时,先传输最高位,且每一个字节后必须跟随一位应答位。

读时序:

①主机发出起始信号,即开始标志位,紧跟着发出从机地址(7、8、10位),之后还有一位读写位(R/W),其中0为写,1为读。

②对应地址的从机接收到起始信号后,发送应答信号(Ack)。

③主机收到应答信号后,发送要写入的寄存器的地址

④从机发送应答信号。

⑤主机收到应答信号后,发送数据。

⑥从机发送应答信号。

⑦主机收到应答信号后,发送停止信号,完成此次单字节数据传输。

【注】多字节发送,只需在完成单字节传输后,紧跟着发送下一个字节即可,每个字节都需要等待收到从机的应答信号后,才可以继续发送。

读时序:

①主机发出起始信号,紧跟着发送从机地址,以及一位写操作标志(1)

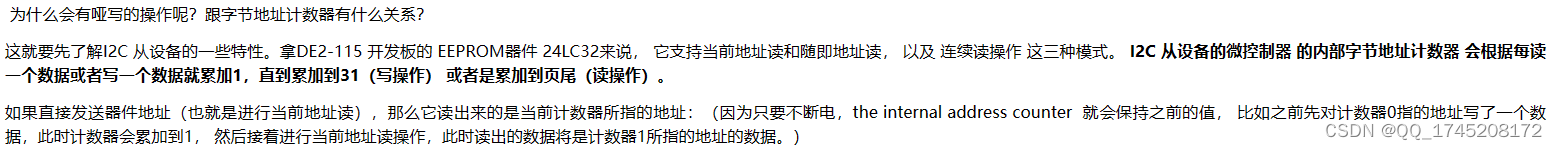

【注】此处的操作为哑写操作,目的是为了归零IIC从机内部的字节地址计数器,理解为初始化从机地址,保证正确发送到指定的从机。

②从机发送应答信号。

③主机收到应答信号后,发送要读写的从机寄存器地址。

④从机发送应答信号。

⑤主机收到应答信号后,主机再发送一次起始信号,紧跟着发送从机地址和读操作标志(0)

⑥从机发送应答信号,紧跟着发送寄存器中的数据。

⑦本次传输以主机发送nAck信号和Stop结束标志结束。

【注】nAck信号是接收端在第九个时钟信号是拉高SDA表示不应答。

【注】起始信号:SCL为高,SDA由高到低;停止信号:SCL为高,SDA由低到高。

2、iic寻址(7、8、10)

7位寻址:第一个字节的前7位为从机地址,第8位(最低位)为读/写位。

8位寻址:从机地址中包含了读写位,需要提取出来从机地址。

【注】判断7、8位寻址,看从机地址是从0x07-0x78之间,则为7位寻址,否则为8位寻址。

10位寻址:传输时,前两个字节包含10Bit地址,第一个字节中有特殊的保留地址来指示当前传输的地址格式为10bit地址。

3、iic最多可以搭载2^7=128个设备,除去保留地址16个,还有112个可以用做从机地址。

【注】由于IIC协议规定了总线电容不能超过400pF,模拟IIC外部有上拉电阻,电阻和总线电容会产生一个RC延时效应(电路中的电容和电阻之间的耦合效应使得在放电的过程中,电流被慢慢地释放),电容越大,则信号的边沿越缓,有可能带来信号质量风险。实际设计中经验值大概是不超过8个器件。

4、iic时钟同步与总线数据仲裁

时钟同步是通过IIC总线上的SCL之间的线与来完成的。如果有多个主机产生时钟信号,则所有主机发送高电平,SCL为高电平,否则为低。

总线仲裁是所有主机上的SDA都写1时,SDA的数据才是1,否则为0。

数据仲裁:SCL线负责时钟,SDA线负责数据仲裁。同步一个主机每发送一个bit数据,在SCL处于高电平时,就检查看SDA的电平是否和发送的数据一致,如果不一致,这个主机便知道自己输掉仲裁,然后停止向SDA写数据。仲裁的过程可能要经过多个bit的发送和检查,实际上两个主机如果发送的时序和数据完全一样,则两个主机都能正常完成整个的数据传输。

5、如何修改iic的传输速率

8位串行双向数据传输速率的五中模式:标准模式为100kbit/s,快速模式为400kbit/s,快速增强模式为1Mbit/s,高速模式为3.4Mbit/s,超快速模式下5Mbit/s。

STM32的IIC外设可以通过控制时钟控制寄存器(CCR),修改SCL时钟信号的占空比,从而控制传输速率。可选择 I2C 通讯的“标准/快速”模式,这两个模式分别 I2C 对应 100/400Kbit/s 的通讯速率。计算结果得出 CCR 为 30,向该寄存器位写入此值则可以控制 IIC 的通讯速率为400KHz

I2C 协议在 SCL 高电平时对 SDA 信号采样,SCL 低电平时 SDA准备下一个数据,修改 SCL 的高低电平比会影响数据采样。CCR 寄存器中有一个 12 位的配置因子 CCR,它与 I2C 外设的输入时钟源共同作用,产生 SCL 时钟。

3、DS18B20时序

【上电状态下默认的精度为12位(所以最后获取的数据要乘以0.0625得到实际温度)】

1初始化时序

首先拉低总线保持480us,发出复位脉冲,之后释放总线(上拉电阻拉高/直接拉高),延时15-60us,保证DS18B20能够监测到上升沿,之后DS18B20拉低总线表示初始化完成,之后延时240us让DS18B20释放总线。

2写时序

【所有写的时间间隔大于60us】【相邻两个写时隙必须要有最少1us的恢复时间】【由低到高】

通过总线拉低产生写时隙,【写1时隙】总线在15us内由上拉电阻恢复为高电平【写0时隙】主机在拉低总线产生写时隙后为保证至少60us的延时,要继续拉低总线。

在产生时隙后,DS18B20会在15~60us内采样单总线,在此时间内,总线为高电平,则为1。

3读时序

总线发出读暂存器指令[0xBE]或读电源模式指令[0xB4]后,开始读时序。

【所有读的时间间隔大于60us】【相邻两个读时隙必须要有最少1us的恢复时间】

读时序开始后,总线必须保持1us,然后总线被释放(拉高)。之后DS18B20接管总线,在15us内,DS18B20拉低总线输出0,之后总线被上拉电阻恢复为高电平。

4校验

DS18B20中特有的64位光刻ROM存储器,64位光刻ROM的排列最后8位是前面56位的循环冗余校验码(CRC=X8+X5+X4+1)。光刻ROM的作用是使每一个DS18B20都各不相同,这样就可以实现一根总线上挂接多个DS18B20的目的。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?