一、GPIO介绍

1、GPIO是什么

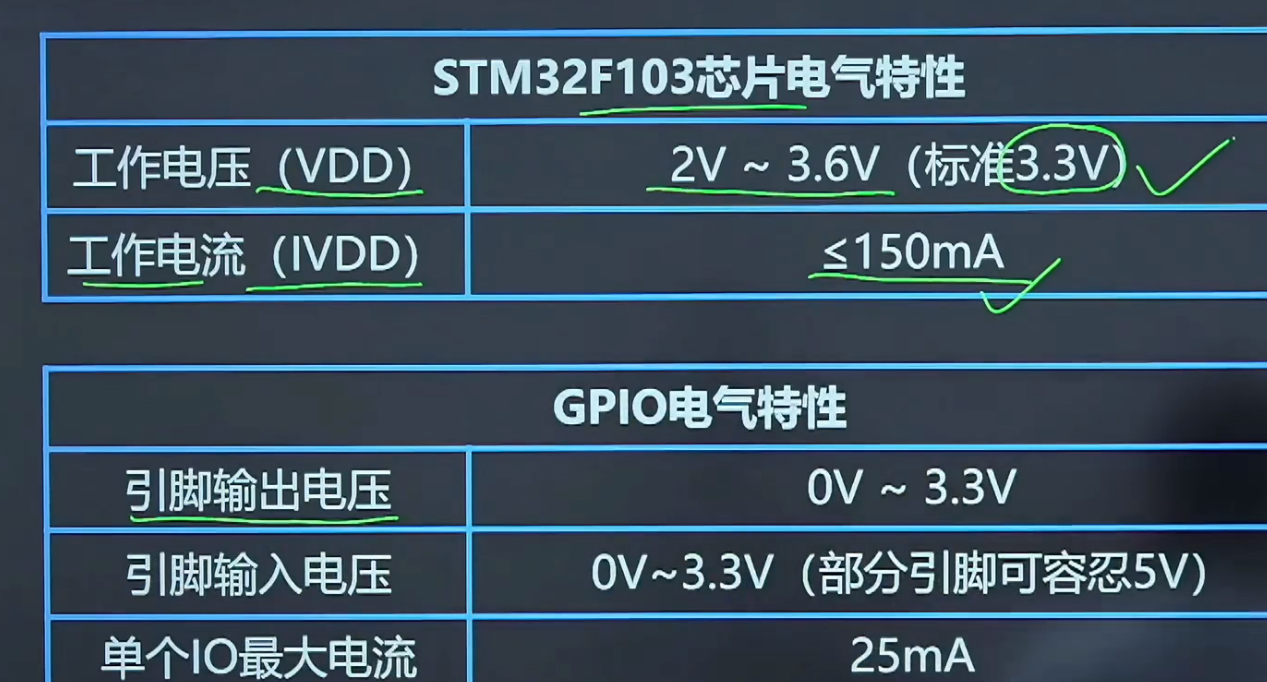

2、GPIO电气特性

手册寻找

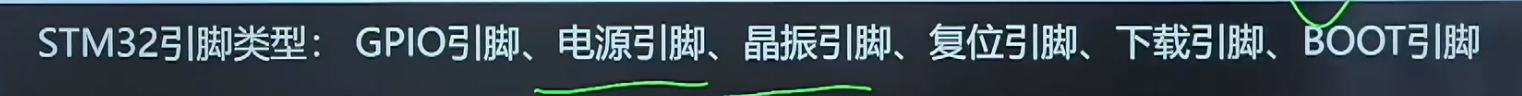

3、GPIO引脚分布

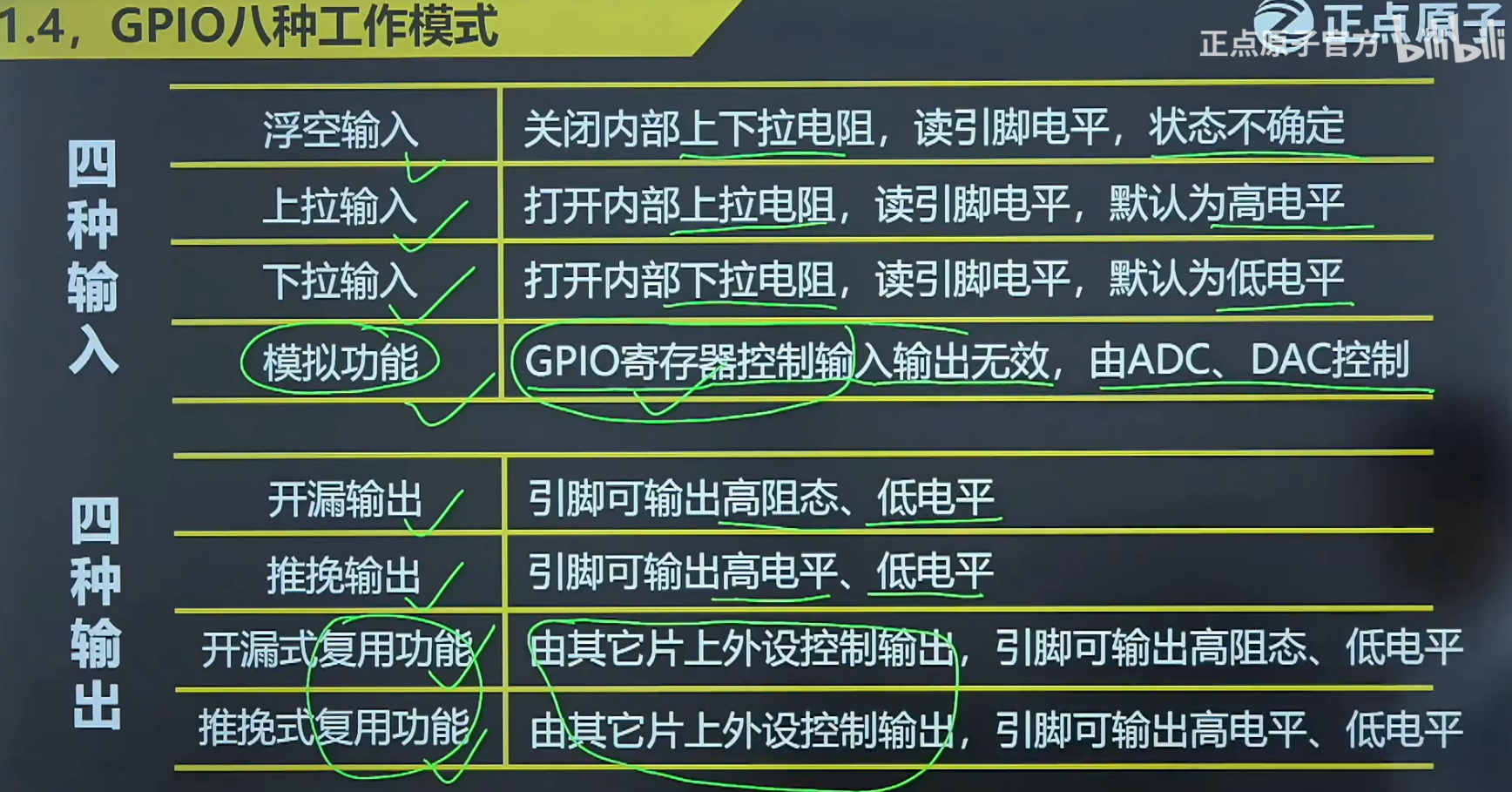

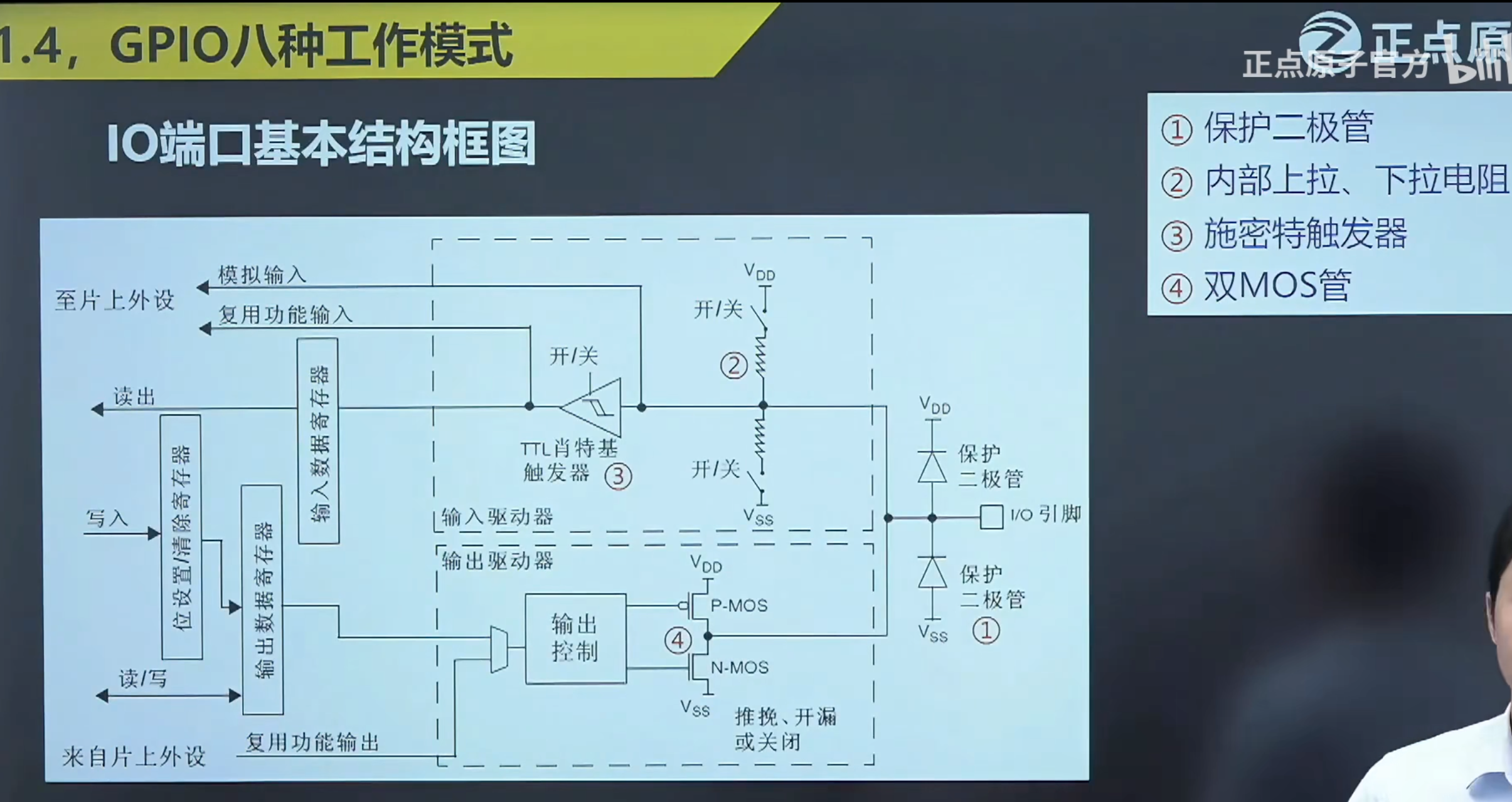

4、GPIO八种工作模式

上图注解:

1. 保护二极管 (Protection Diodes)

在图中,它们通常被画在I/O引脚的两侧,一端连接到VDD(电源),另一端连接到VSS(地)。

-

作用:静电放电保护和过压钳位。

-

工作原理:

-

当引脚上的电压意外地高于VDD(例如,由静电引起)时,上方连接到VDD的二极管会正向导通,将高电压泄放到电源轨上,防止内部精密电路被击穿。

-

当引脚上的电压意外地低于VSS(例如,负电压静电)时,下方连接到VSS的二极管会正向导通,将负电压钳位到地电平。

-

-

重要性:这是防止芯片在恶劣电气环境中被损坏的第一道防线。注意:它们不能用于承受持续的过压或作为稳压电路,大电流会使其烧毁。

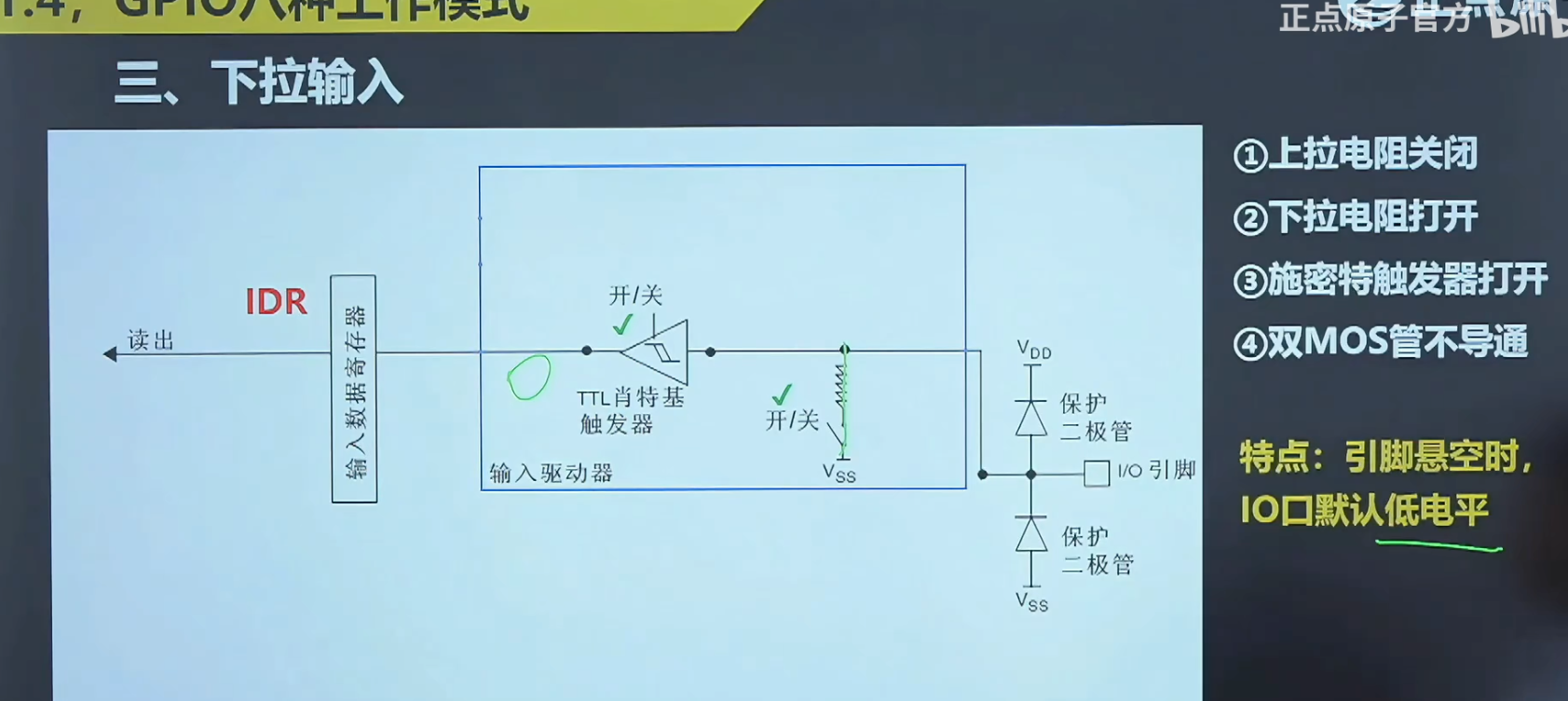

2. 上下拉电阻 (Pull-up / Pull-down Resistors)

在图中,它们通常通过一个开关(MOSFET)连接到VDD(上拉)或VSS(下拉)。

-

作用:确保引脚在悬空(未连接或高阻态)时有一个确定的逻辑电平,防止其电平随机浮动。

-

工作原理:

-

上拉电阻:当开关闭合,电阻将引脚通过高阻值电阻连接到VDD,使引脚在悬空时保持稳定的高电平。

-

下拉电阻:当开关闭合,电阻将引脚通过高阻值电阻连接到VSS,使引脚在悬空时保持稳定的低电平。

-

-

应用场景:

-

配置为输入时,用于读取开关状态(如按键,按下时连接到地,松开时由上拉电阻拉高)。

-

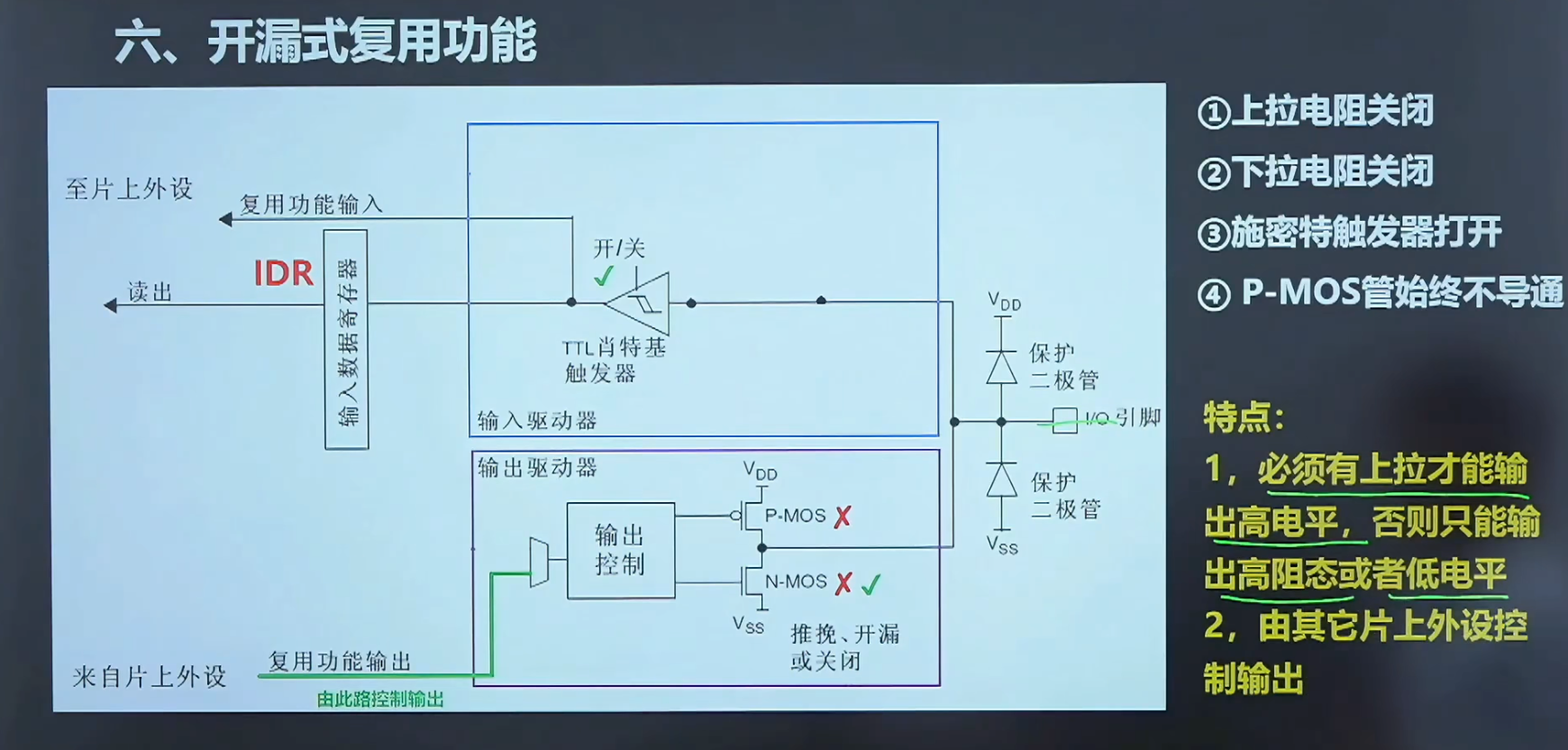

在开漏输出模式下,上拉电阻是必需的,用于提供高电平。

-

3. 肖特基二极管 (Schottky Diodes)

在标准的GPIO框图里,保护二极管通常是普通的PN结二极管。但肖特基二极管因其低正向压降和高速开关特性,有时也会被用于高性能或低电压应用的I/O保护电路中。

-

作用(如果使用):更快速、更高效的钳位保护。

-

优势:相比普通PN结二极管(约0.7V压降),肖特基二极管的压降更低(约0.2-0.3V)。这意味着在过压发生时,它能更早、更快地导通,为敏感电路提供更迅速的保护,尤其是在低电压供电的芯片中。

4. MOS管 (MOSFETs) - P-MOS 和 N-MOS

它们是GPIO输出能力的核心,构成了输出驱动器。

-

作用:驱动负载,提供电流输出能力。

-

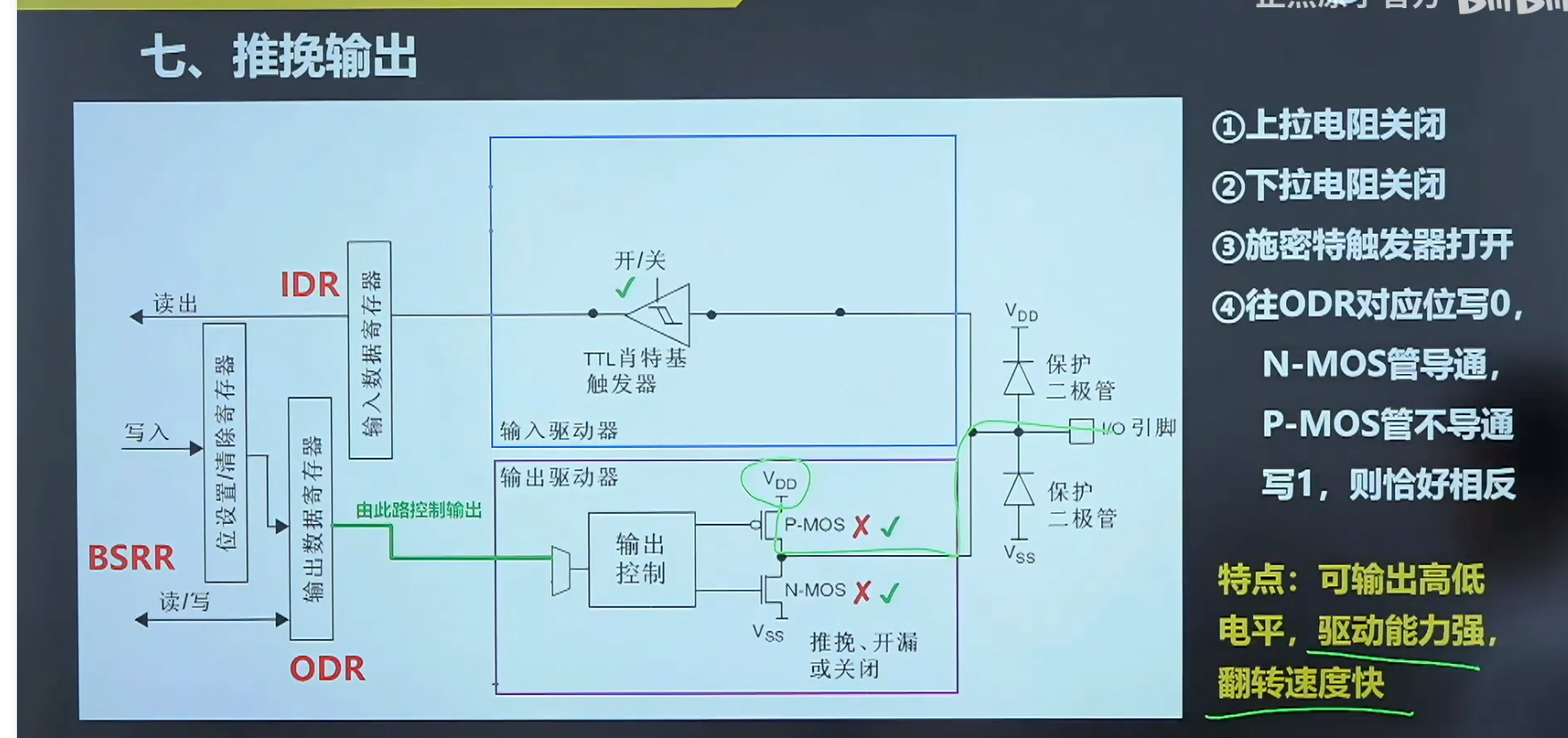

工作原理(推挽输出模式):

-

P-MOS:作为上拉开关。当输出高电平时,P-MOS导通,N-MOS截止,电流从VDD通过P-MOS流向引脚,对外输出高电平。

-

N-MOS:作为下拉开关。当输出低电平时,N-MOS导通,P-MOS截止,电流从引脚通过N-MOS流向VSS,将引脚拉低至地电平。

-

-

其他模式:

-

开漏输出:在此模式下,P-MOS被永久禁用。只有N-MOS工作。当N-MOS导通时,输出低电平;当N-MOS截止时,引脚呈高阻态,电平由外部上拉电阻决定。这种模式便于电平转换和实现“线与”逻辑。

-

总结与协同工作

我们可以把这些元件想象成一个团队,共同管理一个I/O引脚:

-

MOS管(P-MOS & N-MOS) 是 “肌肉” ,负责大力推拉电流,驱动外部电路。

-

上下拉电阻 是 “定锚” ,确保在没人主动控制(悬空)时,引脚不会“随波逐流”,而是稳定在一个已知状态。

-

保护二极管 是 “保镖” ,随时准备吸收来自外部的电压“攻击”(静电、浪涌),保护内部脆弱的“大脑”(核心电路)。

-

肖特基二极管 是 “精英保镖” ,在需要更快速、更灵敏反应的场合执行保护任务。

通过软件配置寄存器,微控制器的CPU可以灵活地控制这些开关和驱动器,让同一个物理引脚扮演数字输入、数字输出、模拟输入或专用外设接口等不同角色,这就是GPIO强大灵活性的根源。

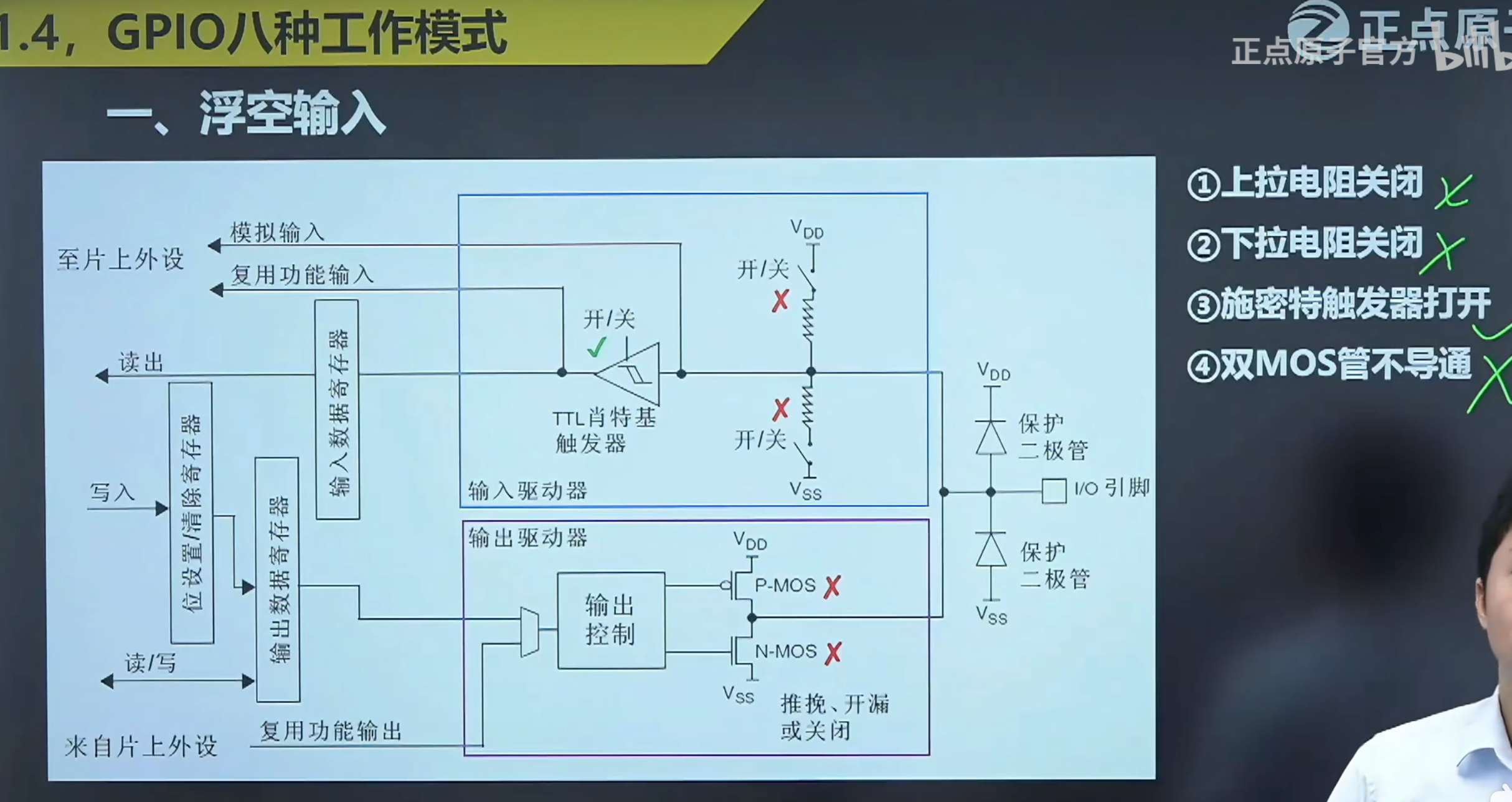

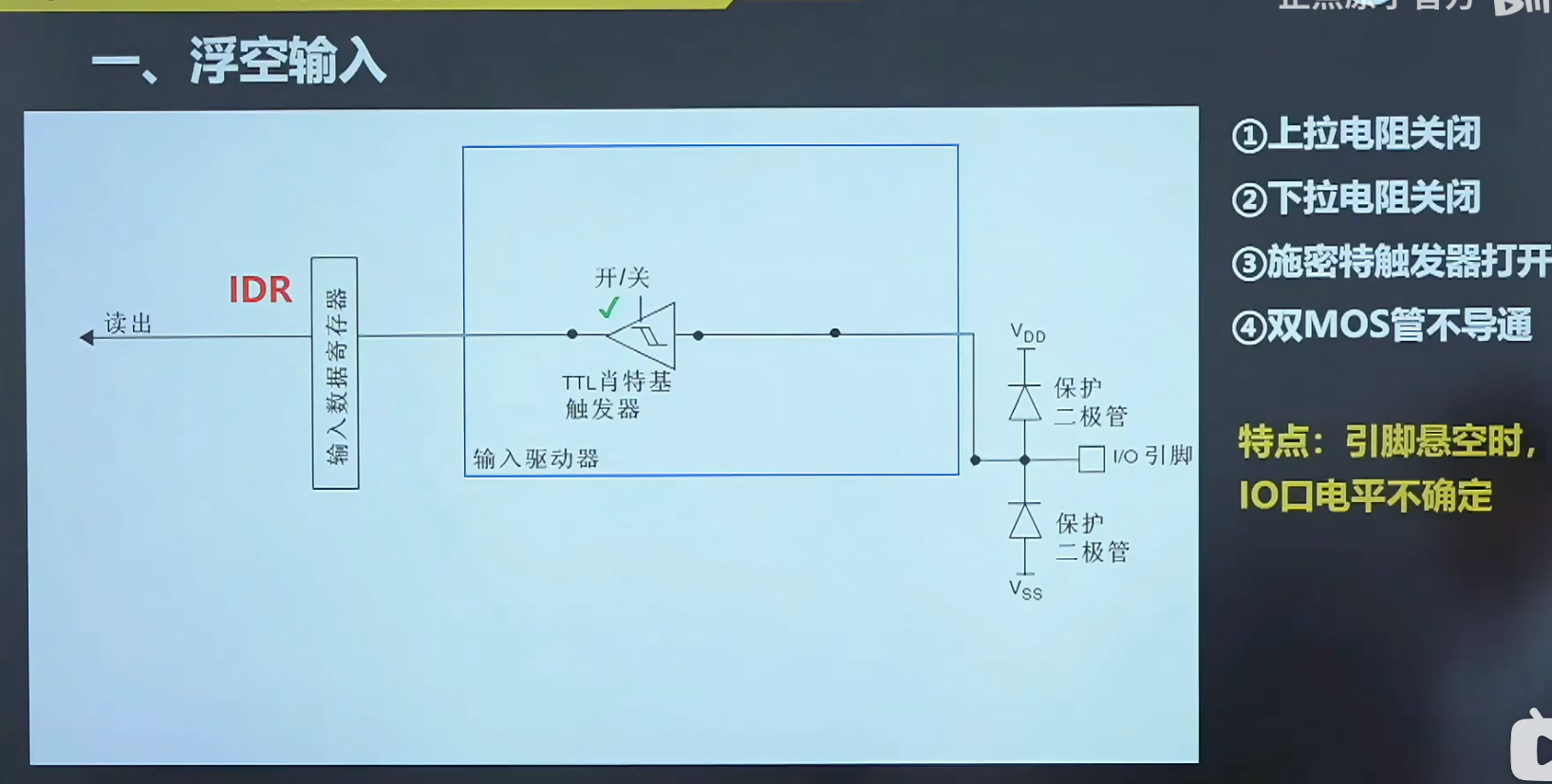

(1)、浮空输入

易受外界干扰

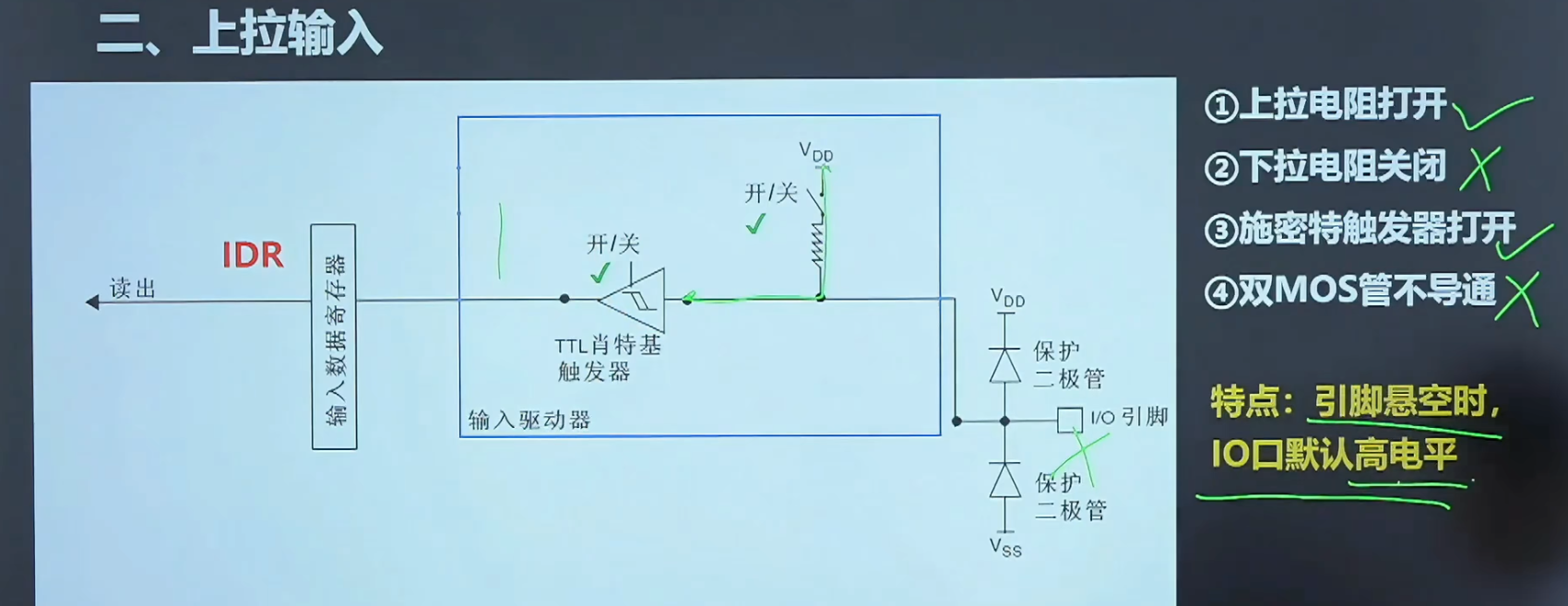

(2)、上拉输入

(3)、下拉输入

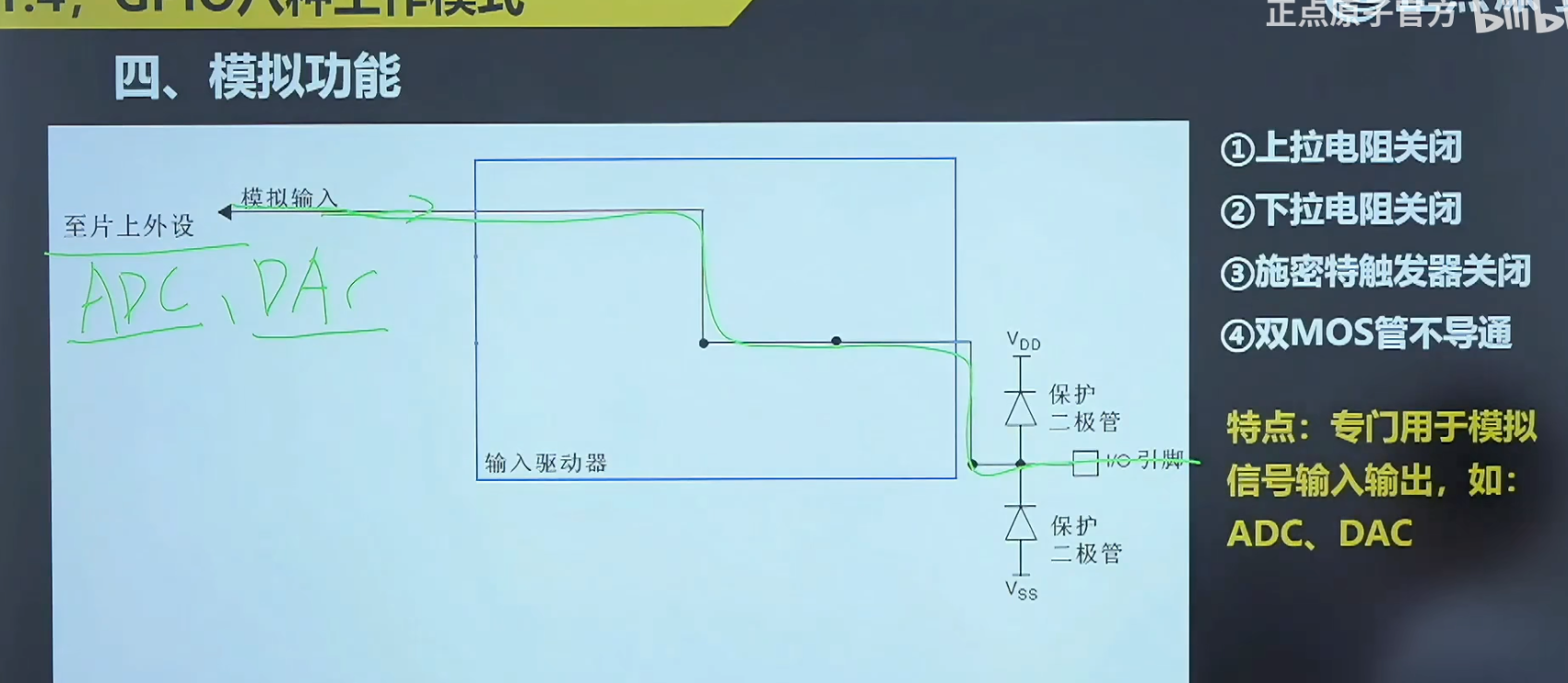

(4)、模拟功能

(5)、开漏输出

(6)、开漏式复用功能

(7)、推挽输出

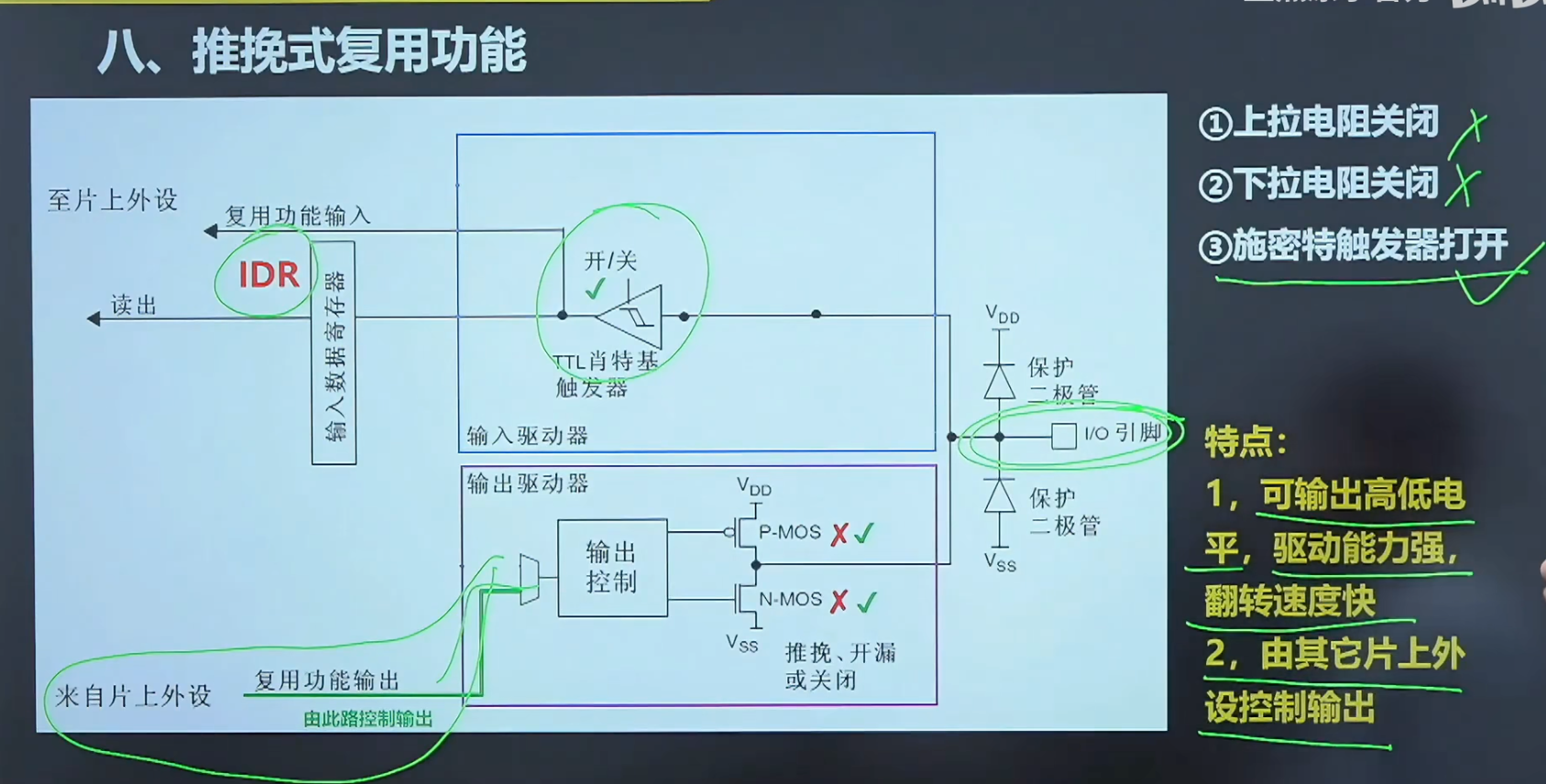

(8)、推挽式复用功能

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?