本项目源于B站立创开发板发布

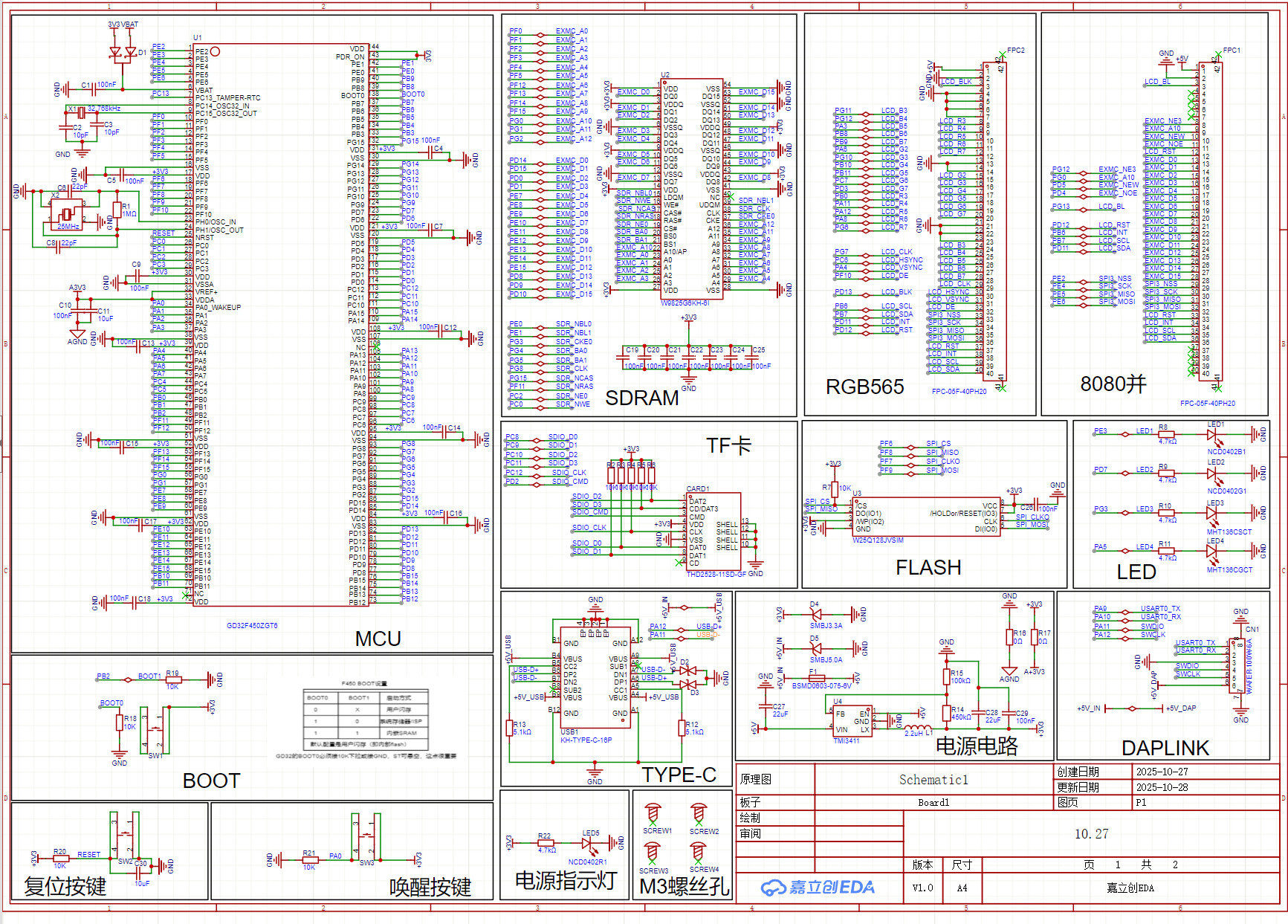

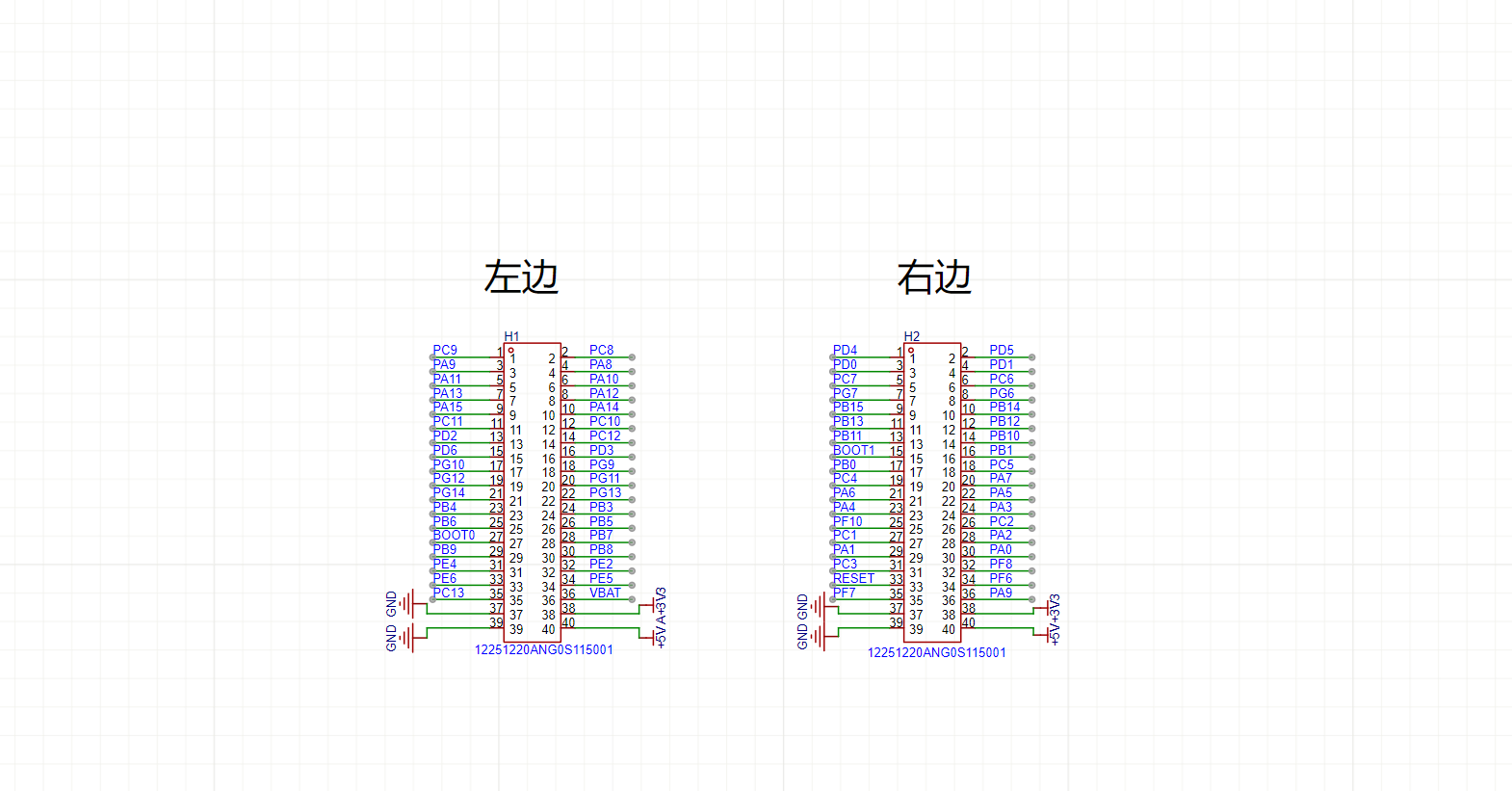

一、原理图

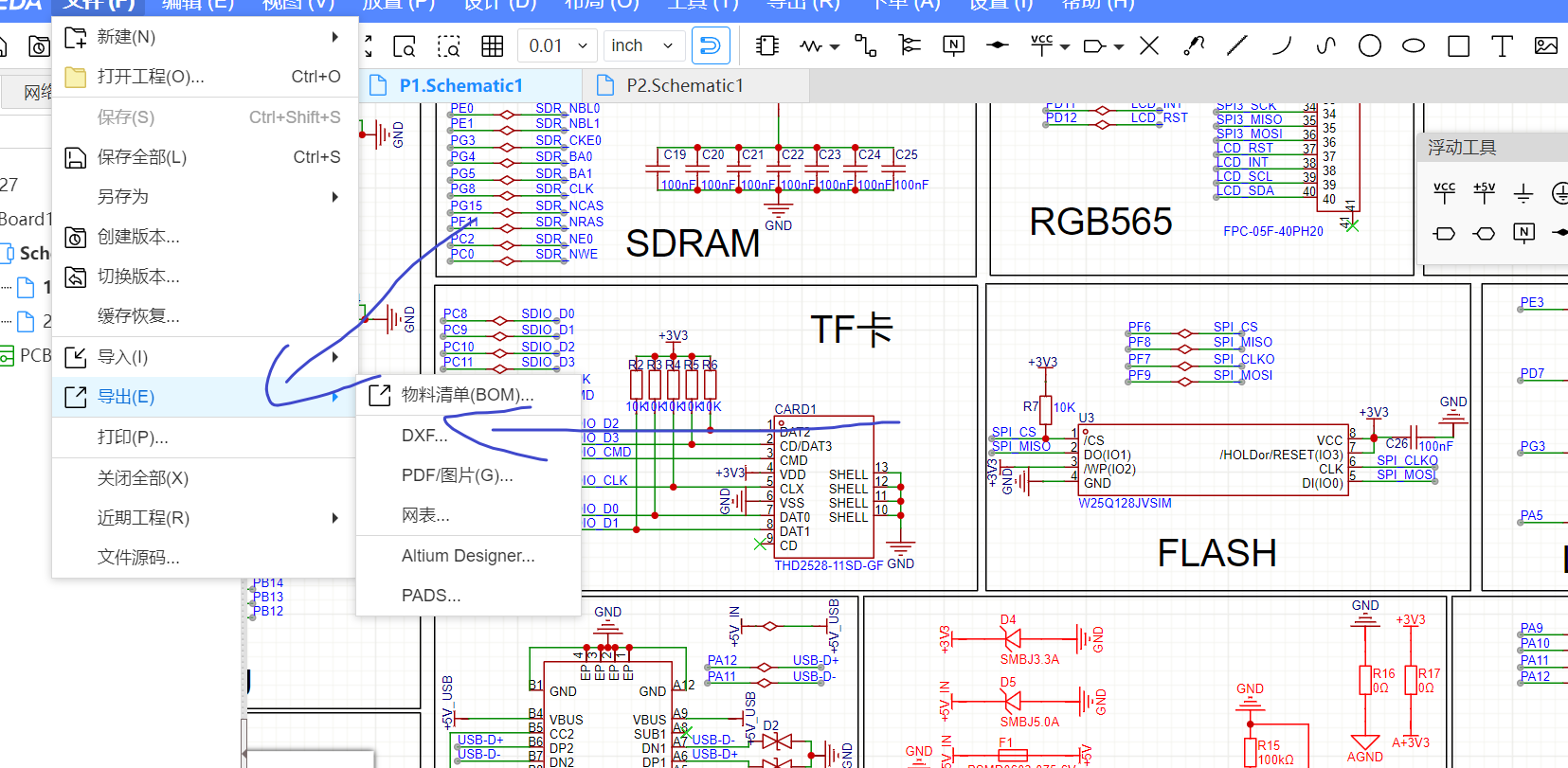

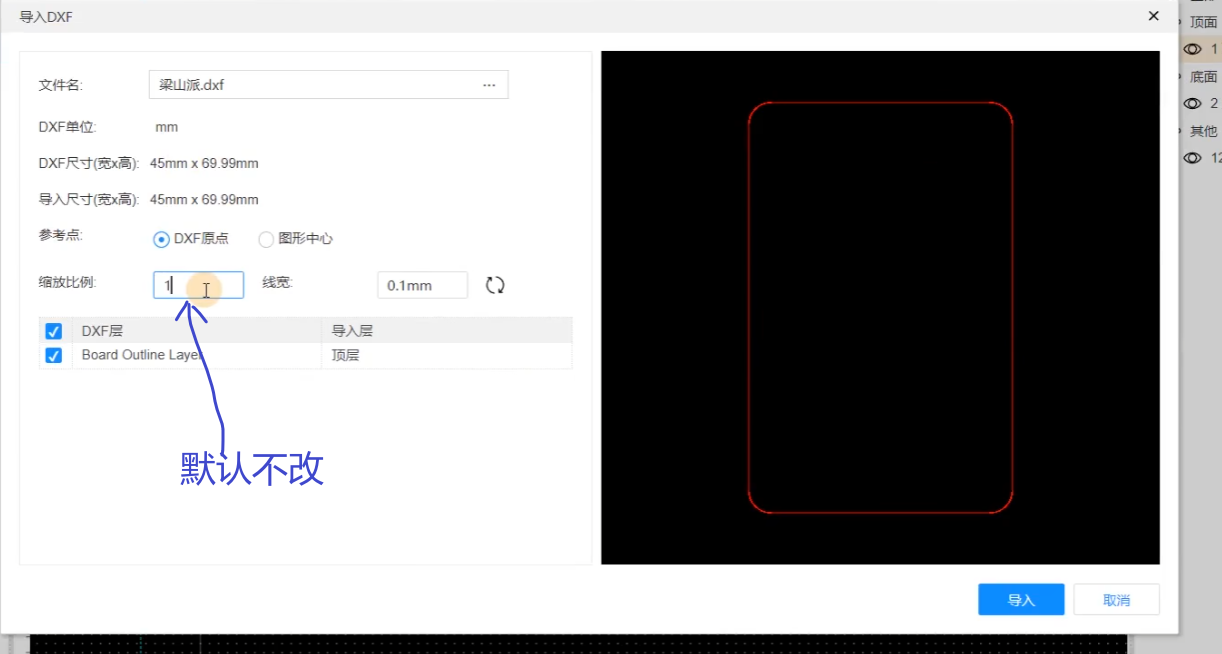

二、板框导入与层叠设计

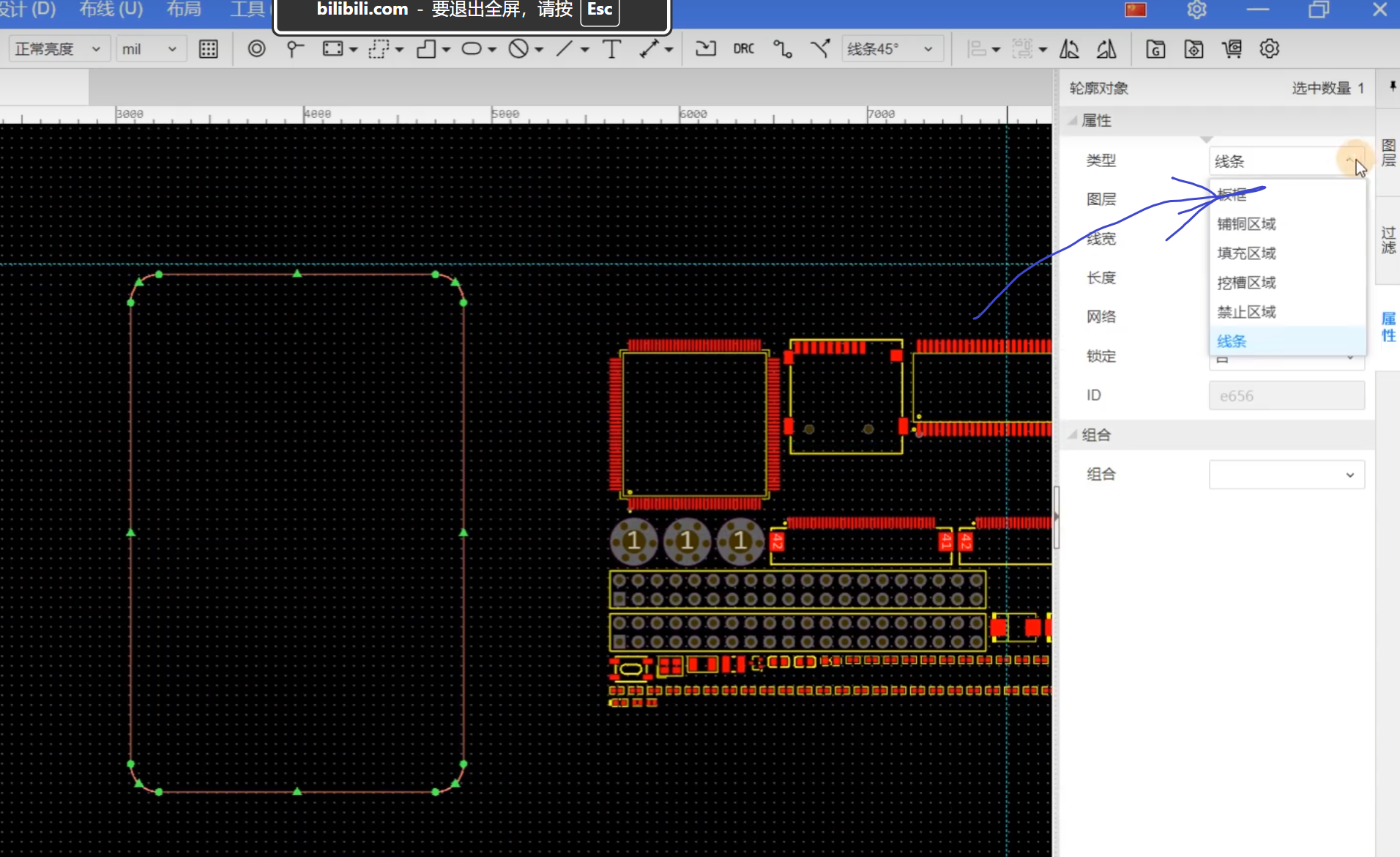

1、板框导入

导入DXF文件

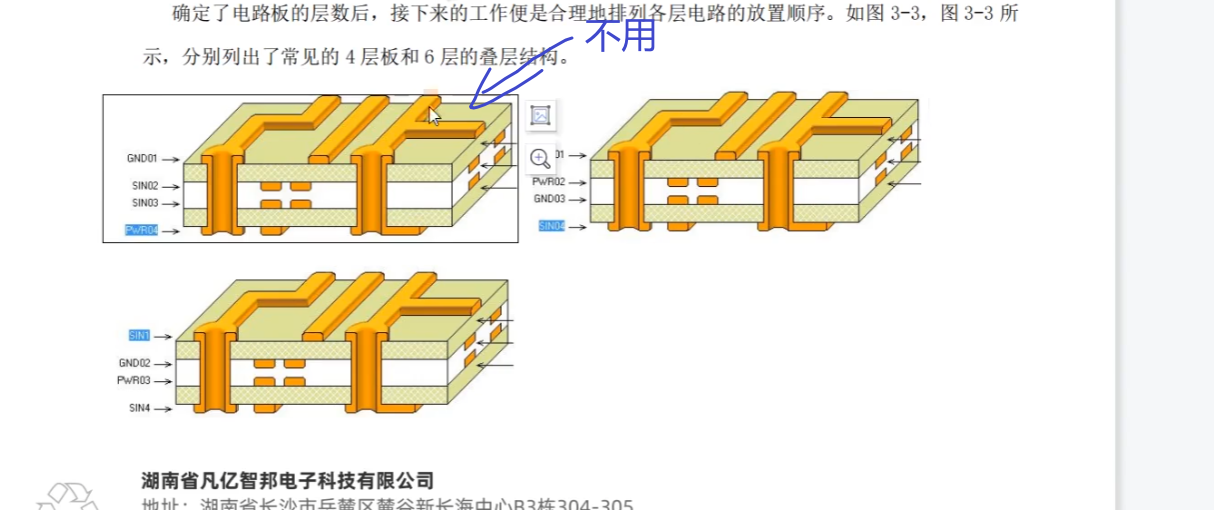

2、层叠设计

多层PCB板的必要:随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。

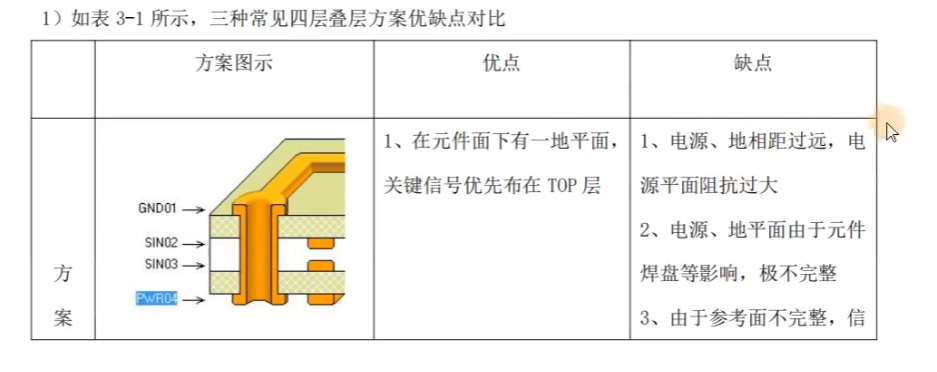

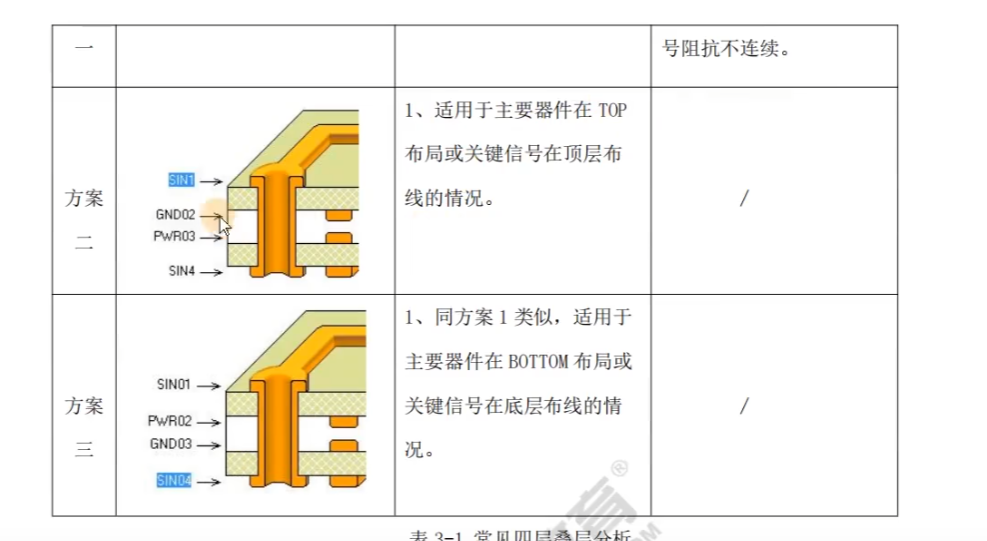

2.1层叠选择

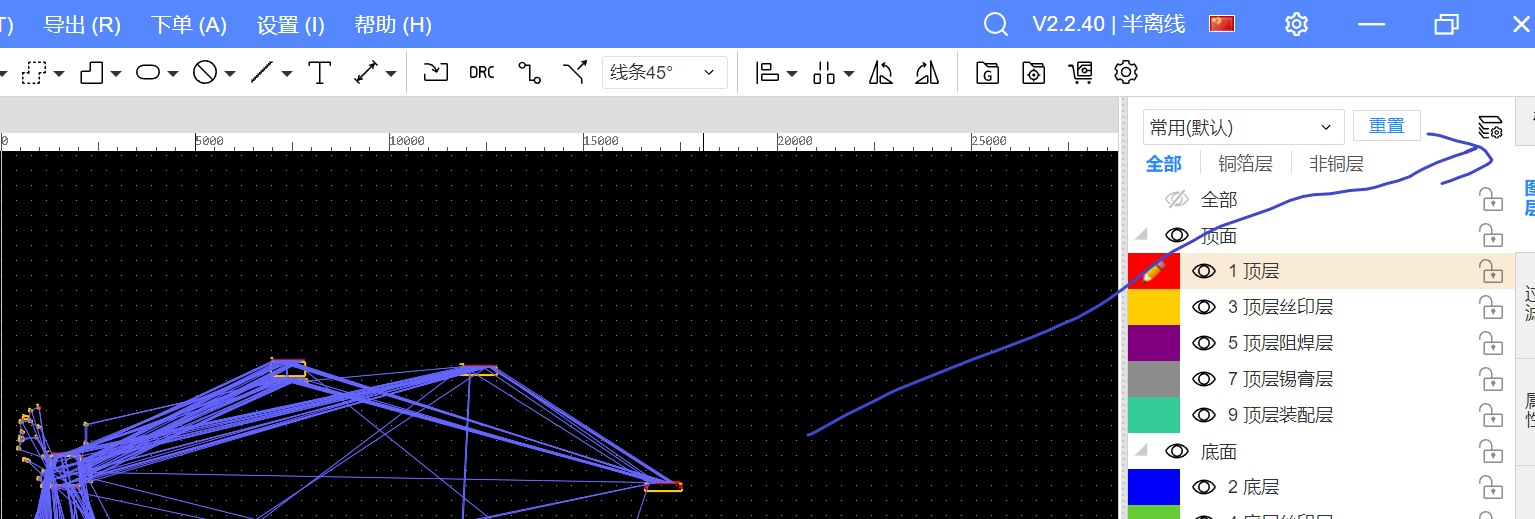

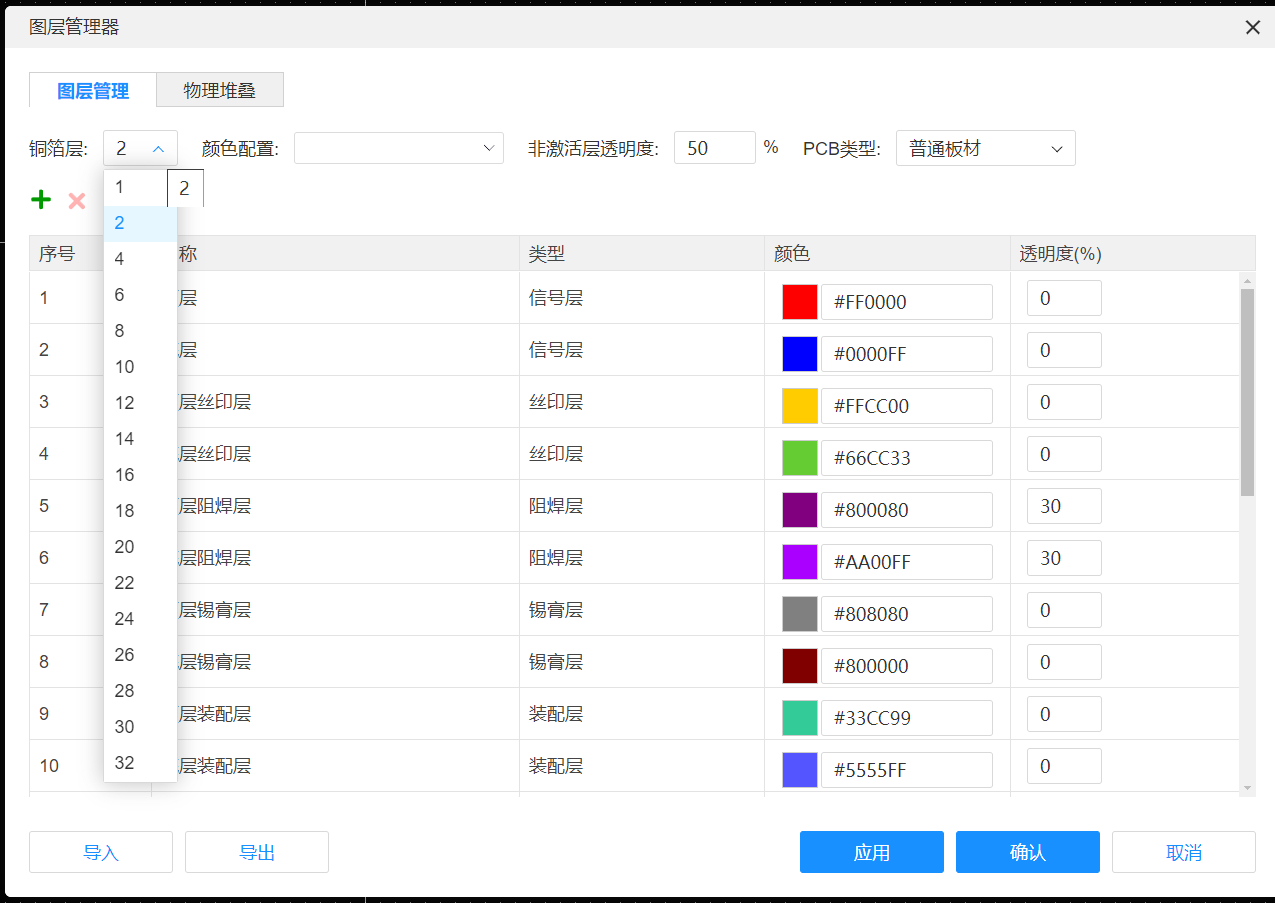

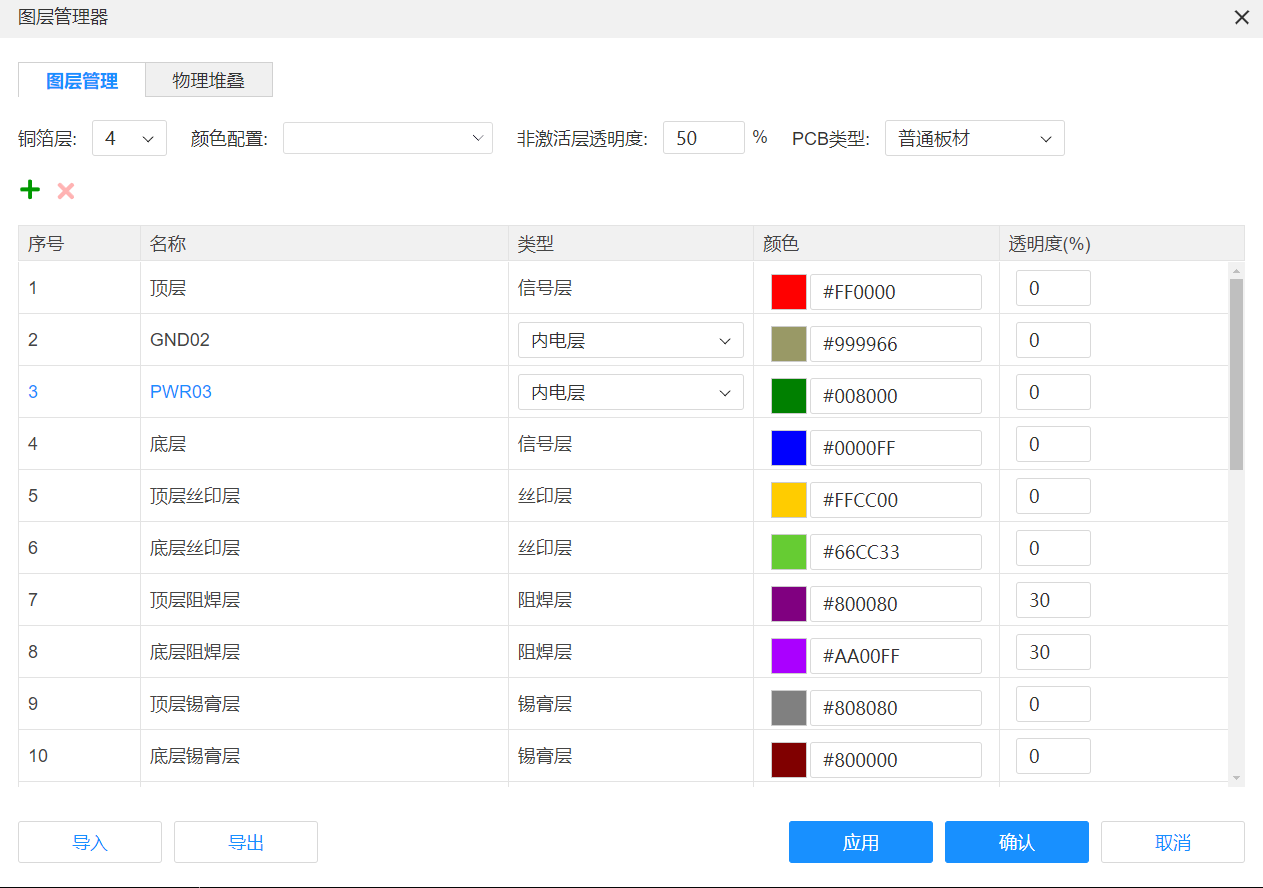

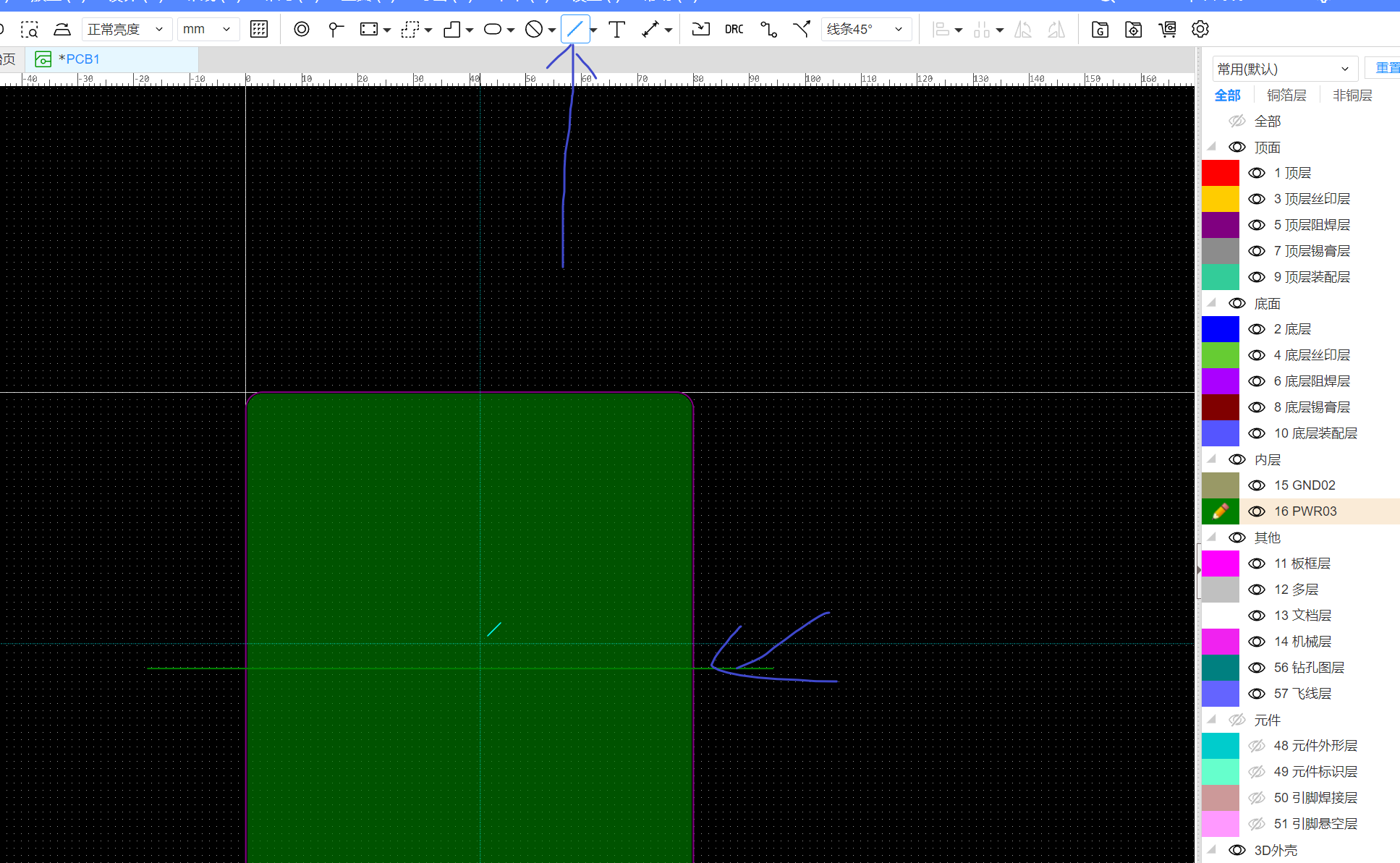

2.2图层设置

注释:内电层默认有铜皮

内层分割采用折线(快捷键Alt+L),绘制之后重新铺铜

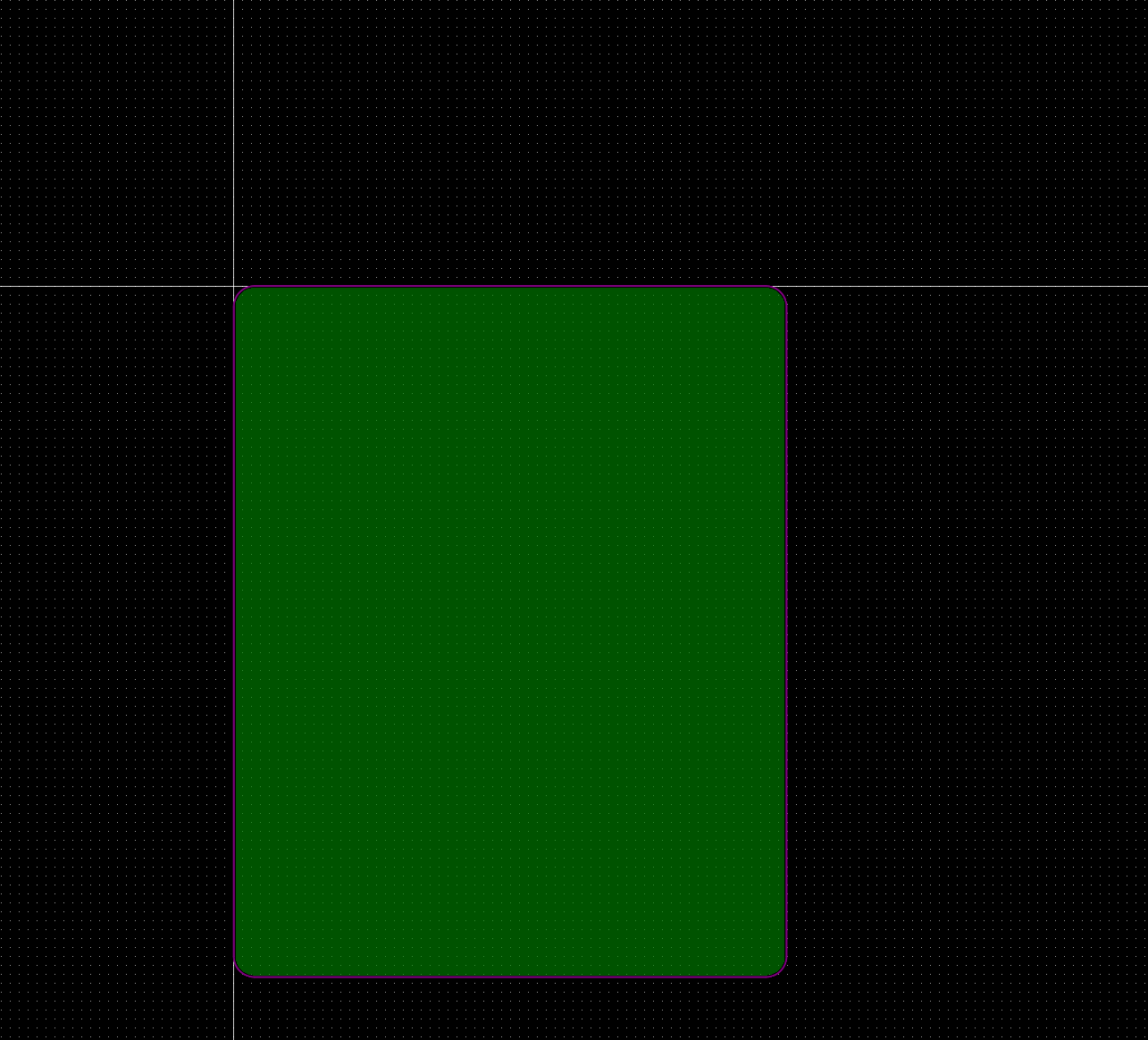

20H原则:20H原则是指电源层相对地层内缩20H的距离,H表示电源层与地层的距离。当然也是为抑制边缘辐射效应。在板的边缘会向外辐射电磁干扰。将电源层内缩,使得电场只在接地层的范围内传导,有效的提高了emc。若内缩20H则可以将70%的电场限制在接地边沿内;内缩100H则可以将98%的电场限制在内。我们要求地平面大于电源或信号层,这样有利于防止对外辐射干扰和屏蔽外界对自身的干扰,一般情况下在pcb设计的时候把电源层比地层内缩1mm基本上就可以满足20H的原则

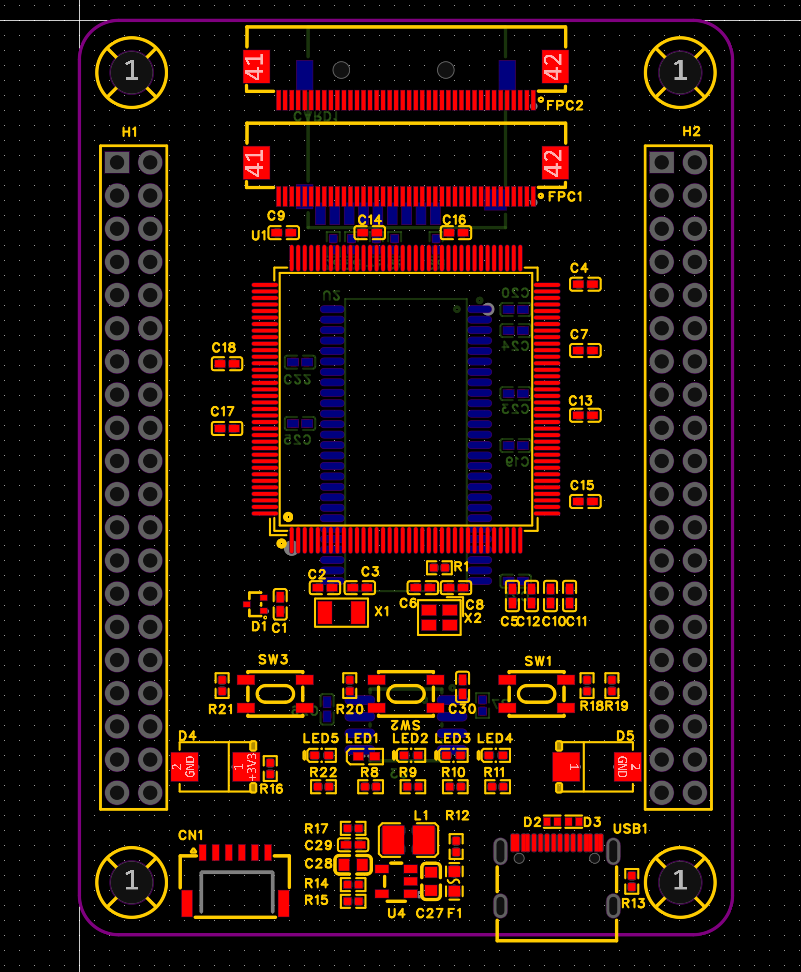

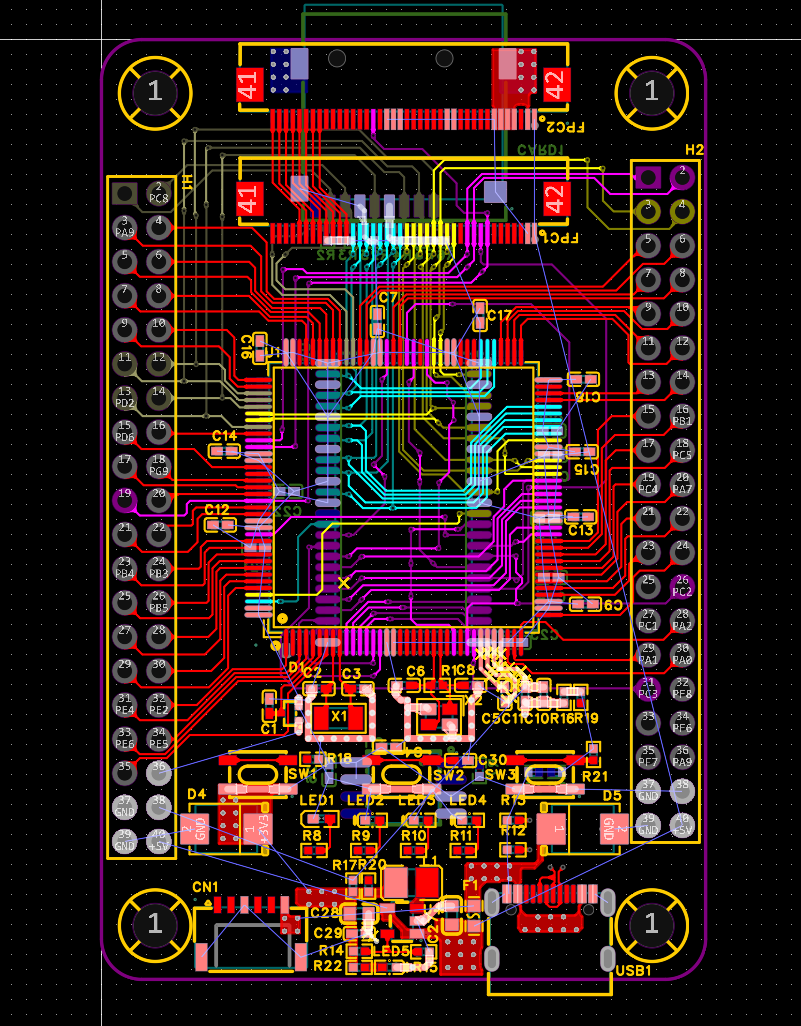

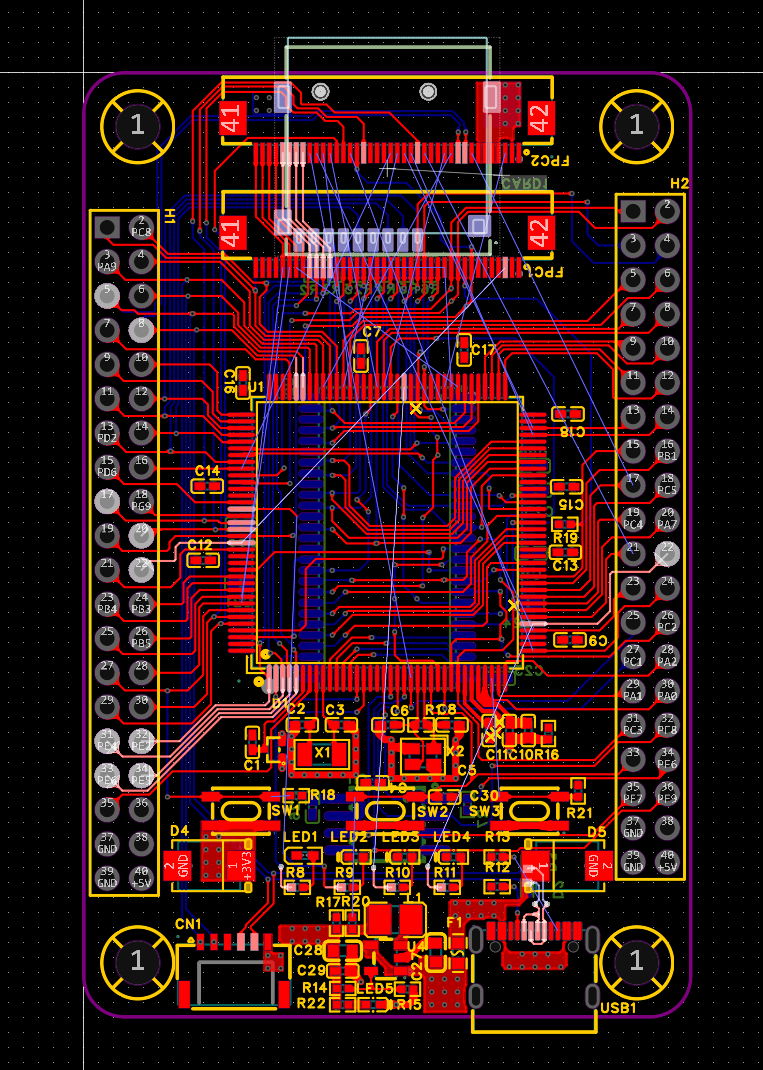

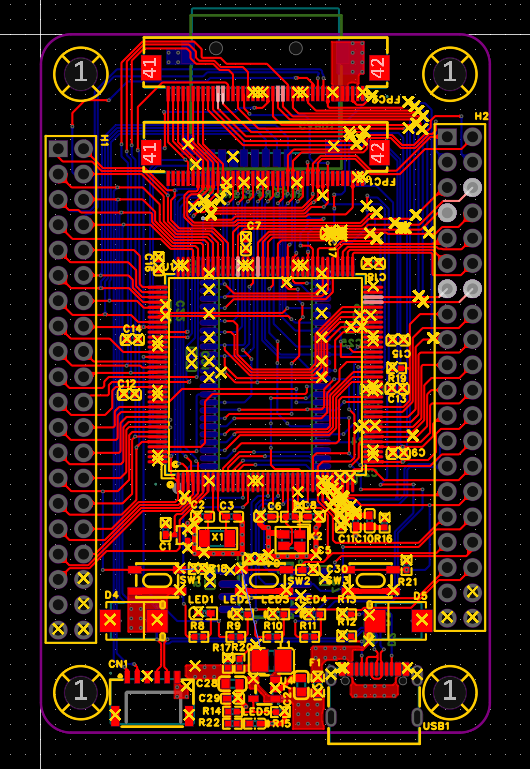

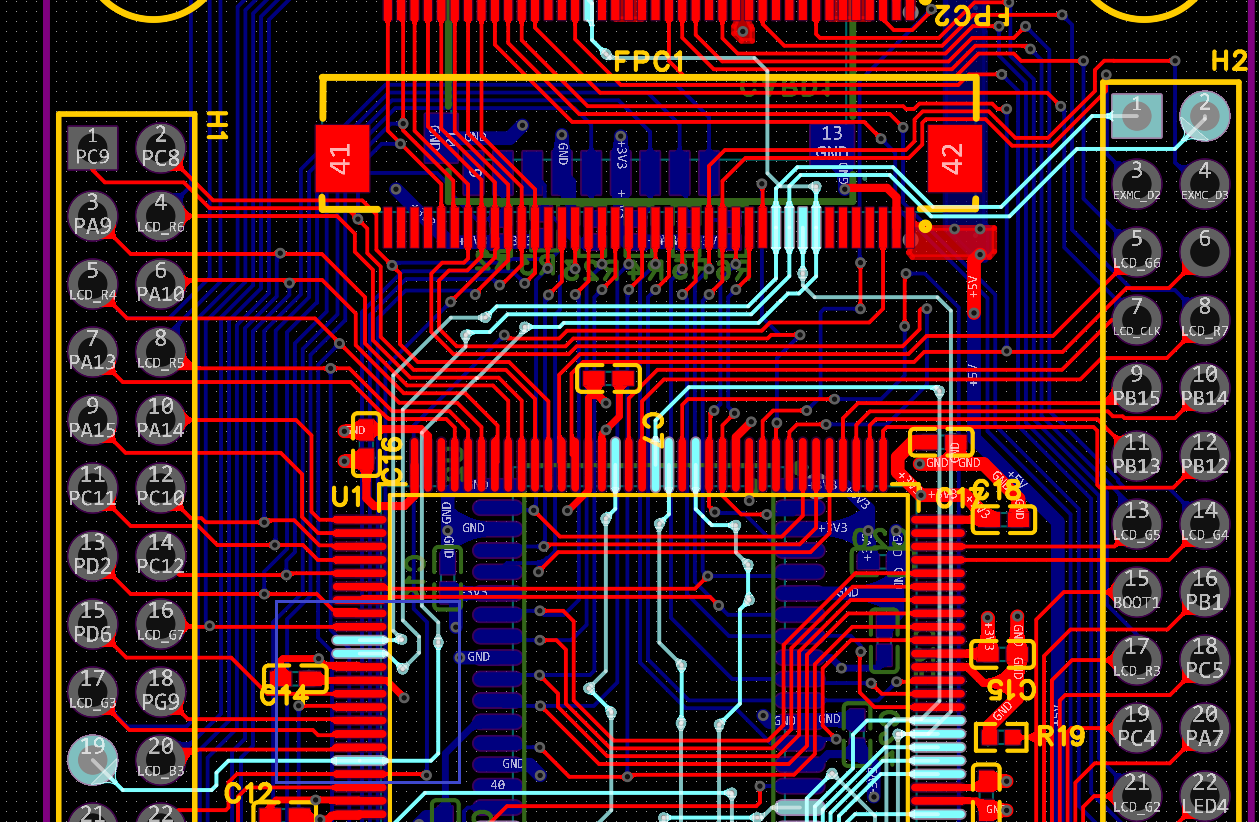

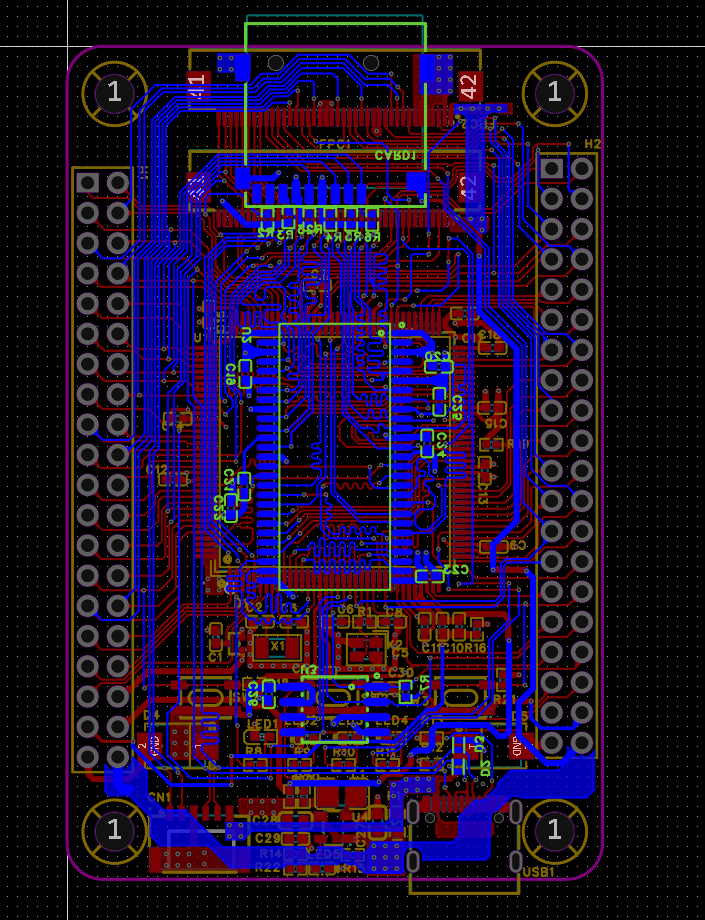

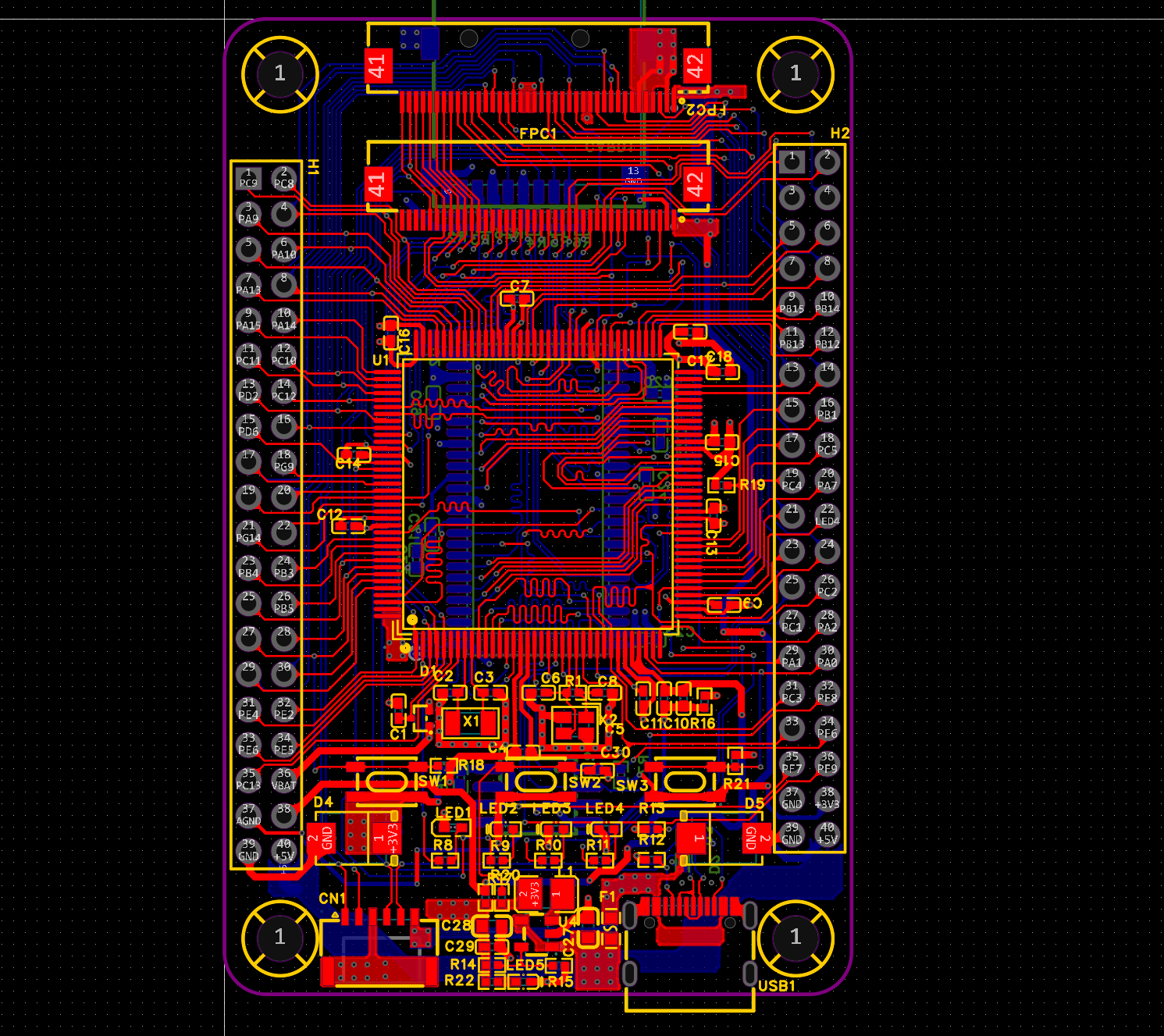

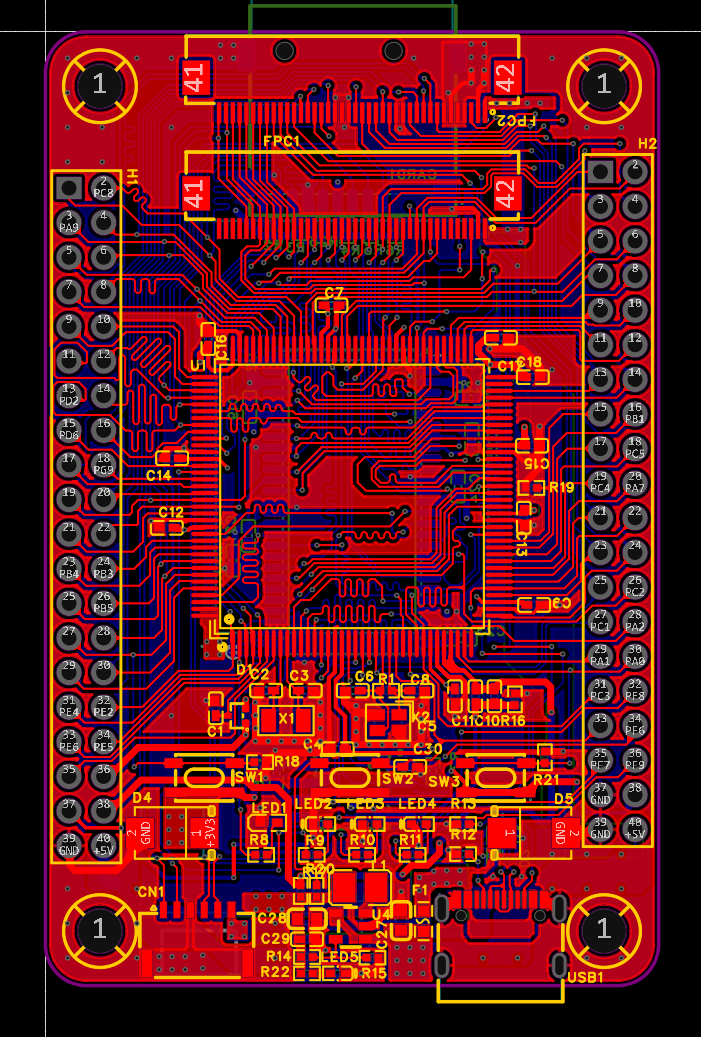

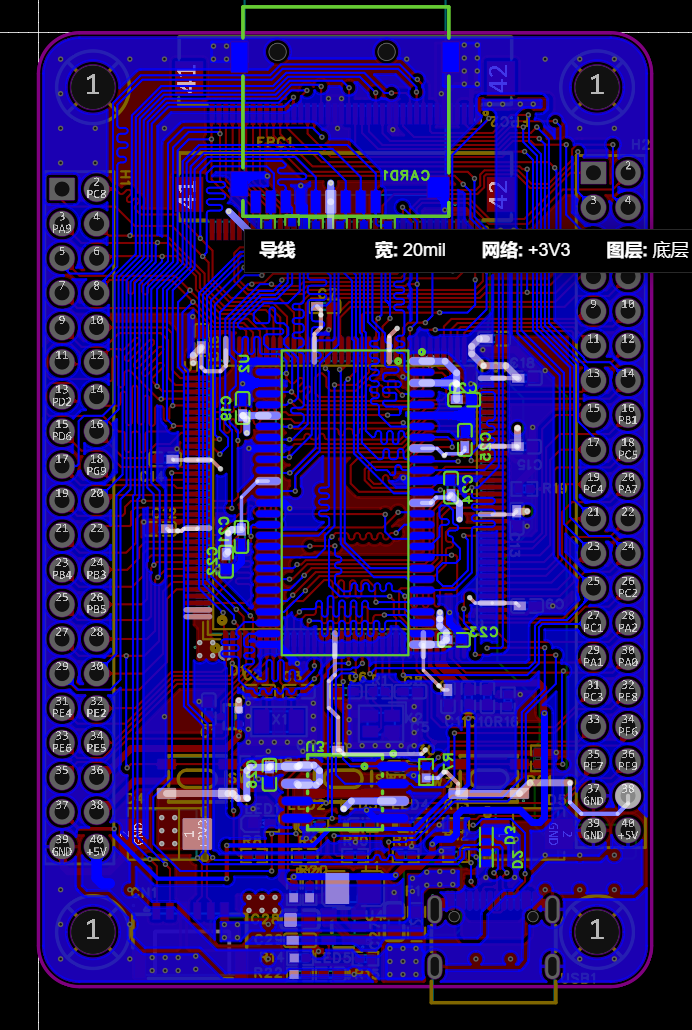

三、布局

注释: Shift + S---单层显示

Alt + T----切换层

Alt + B----切换顶层

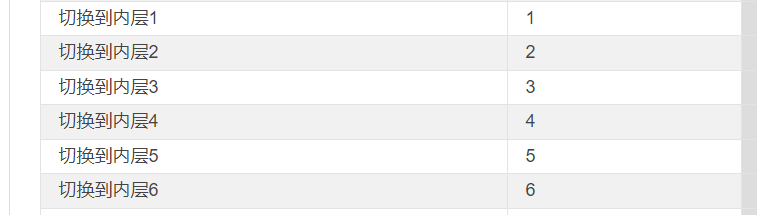

内层快捷键

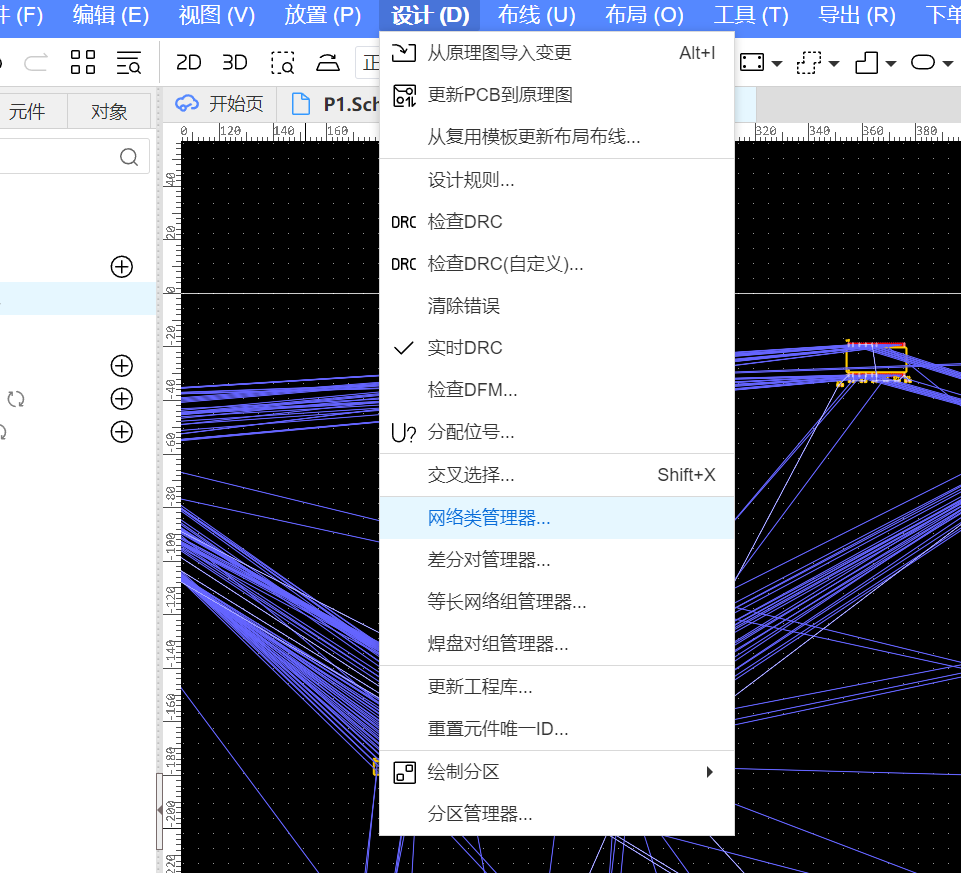

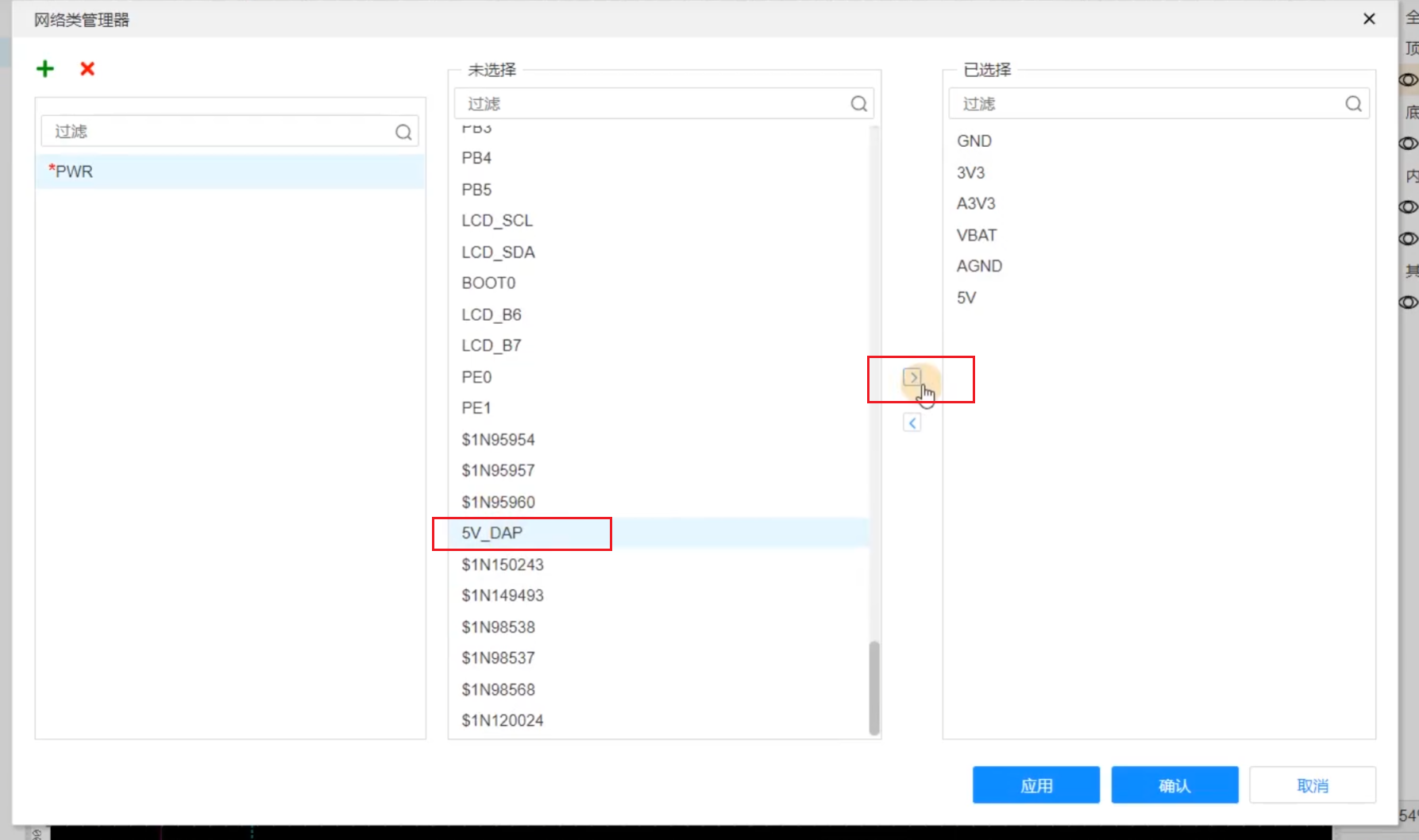

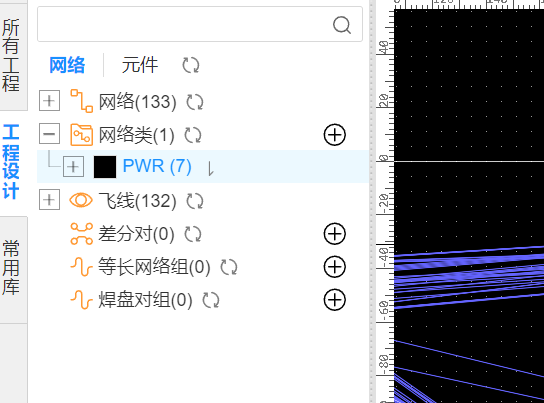

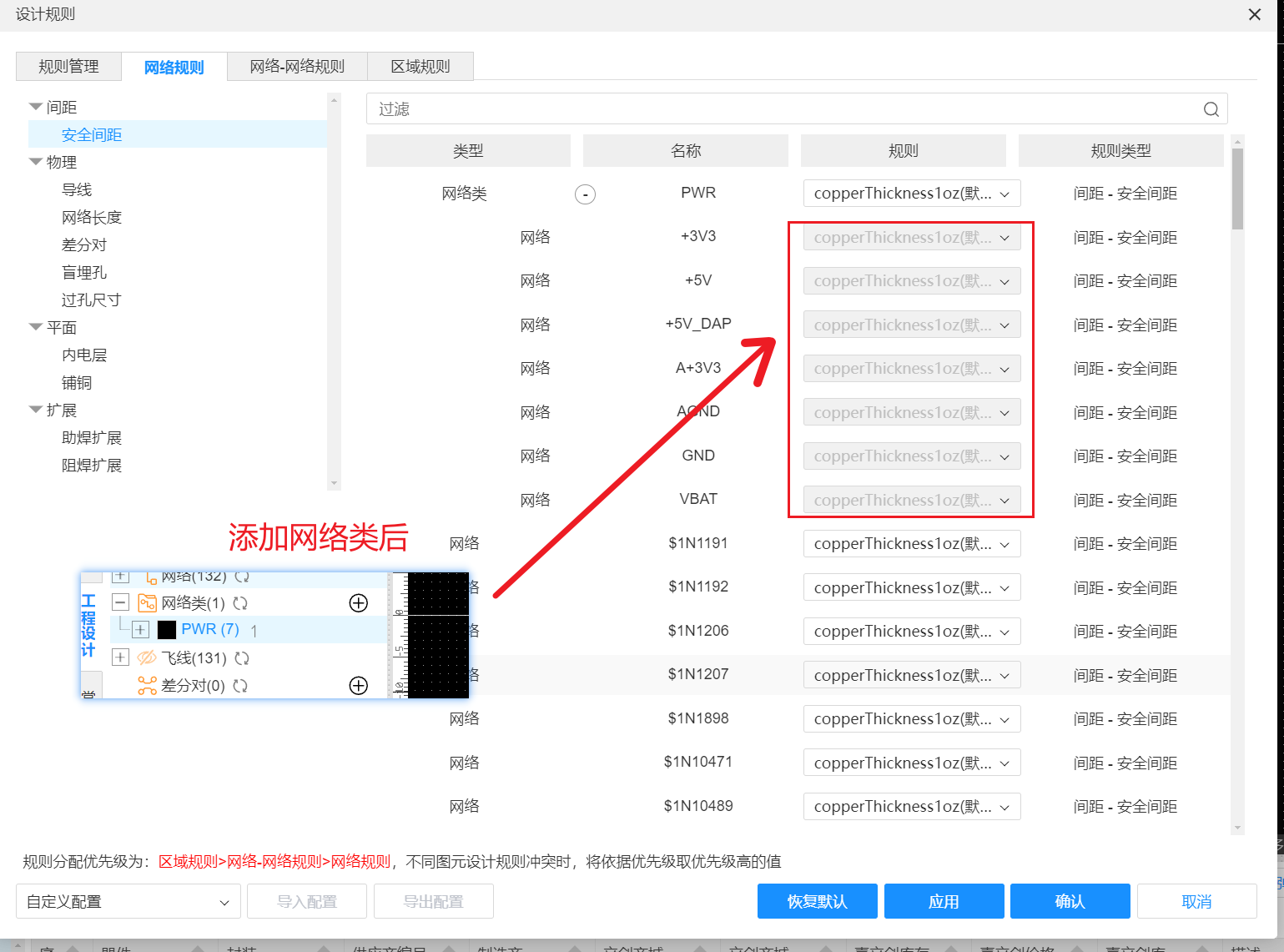

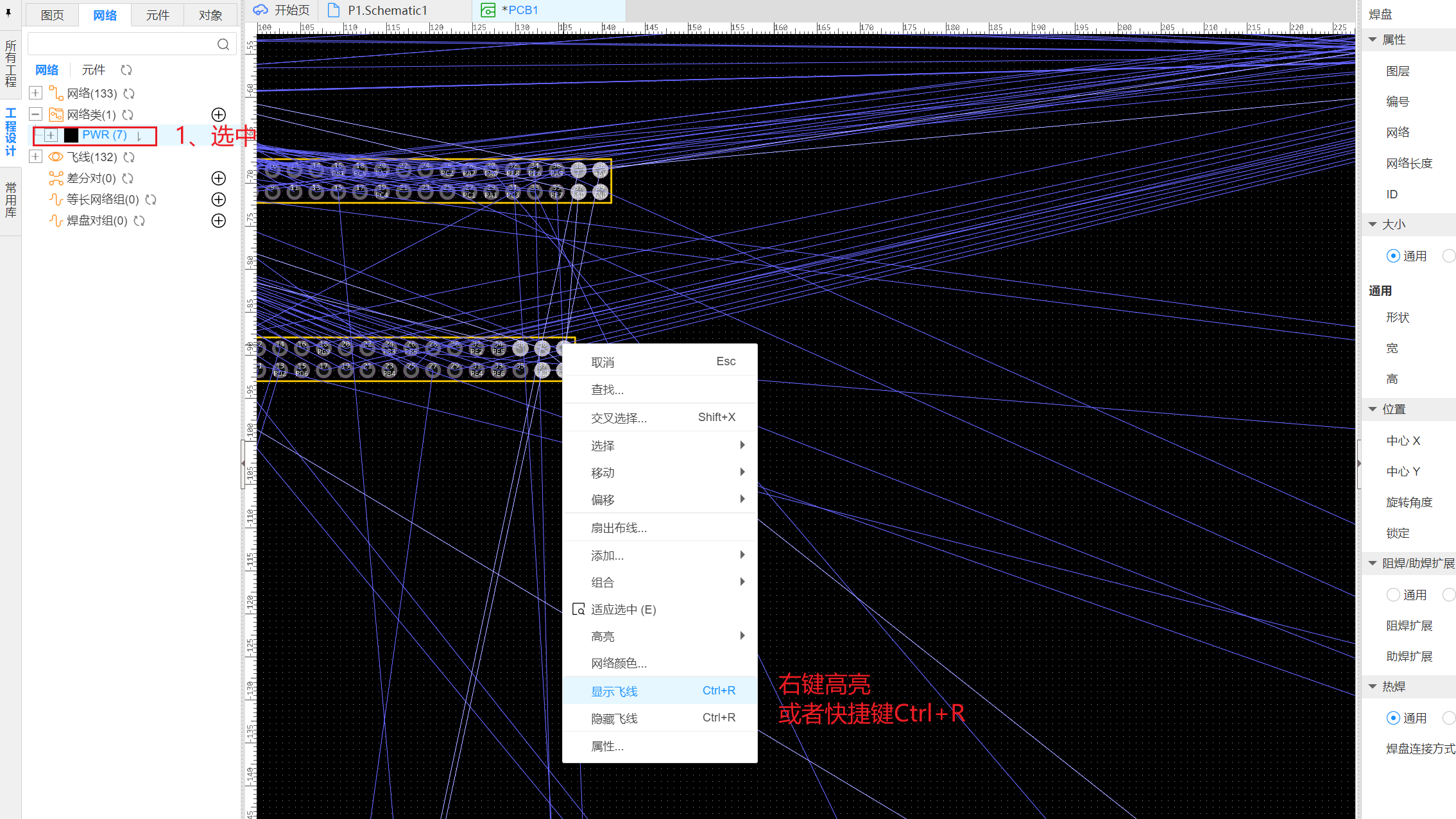

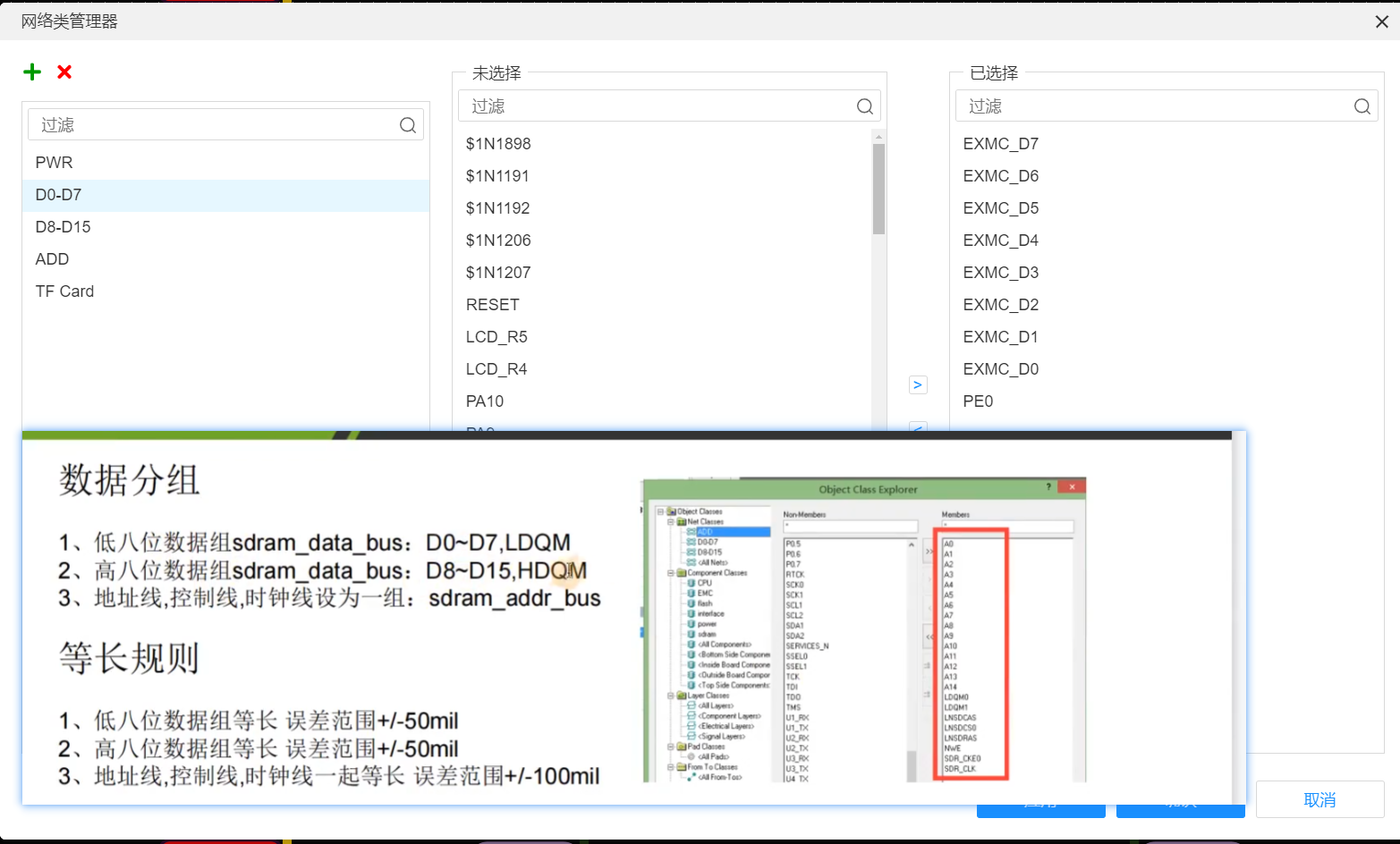

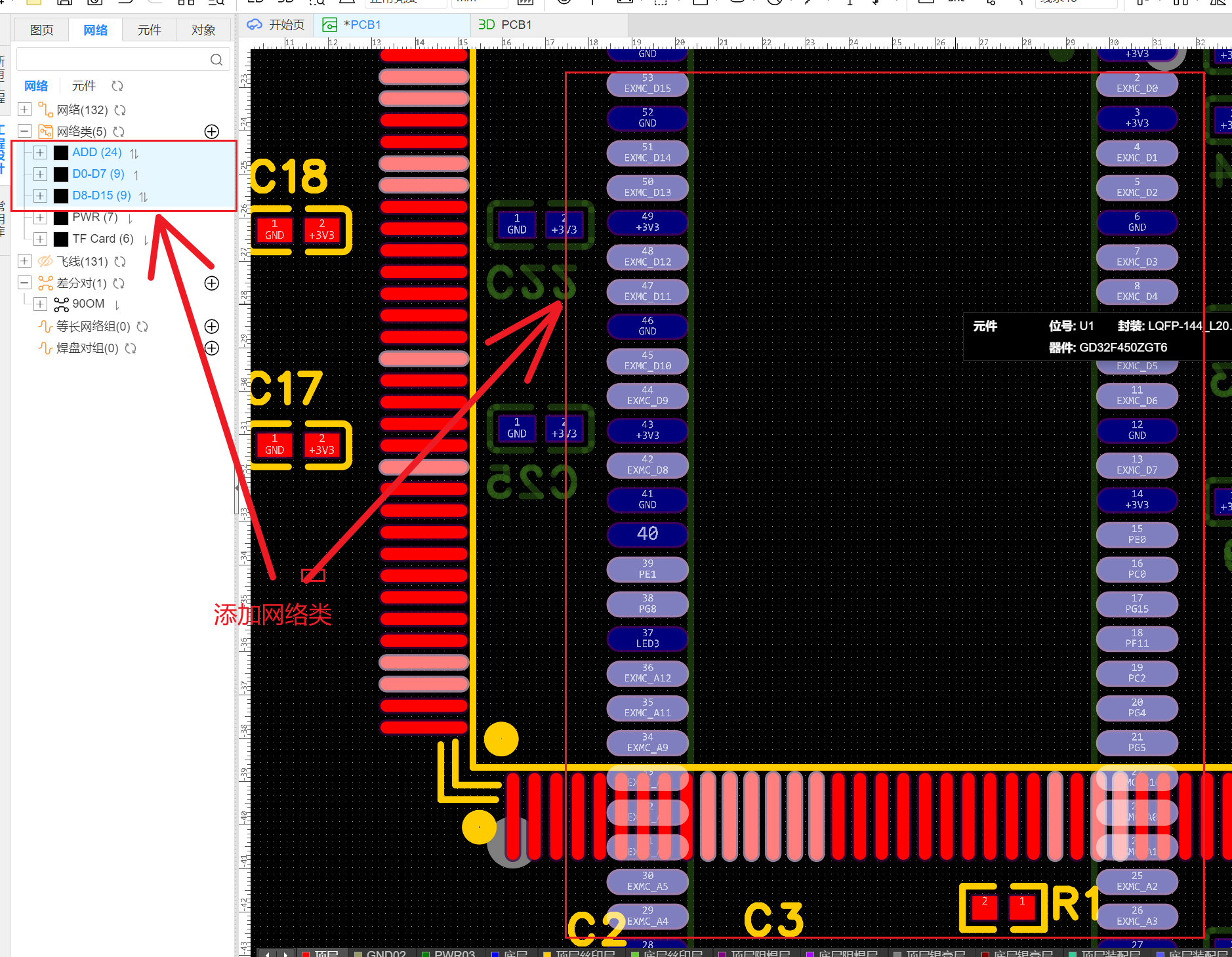

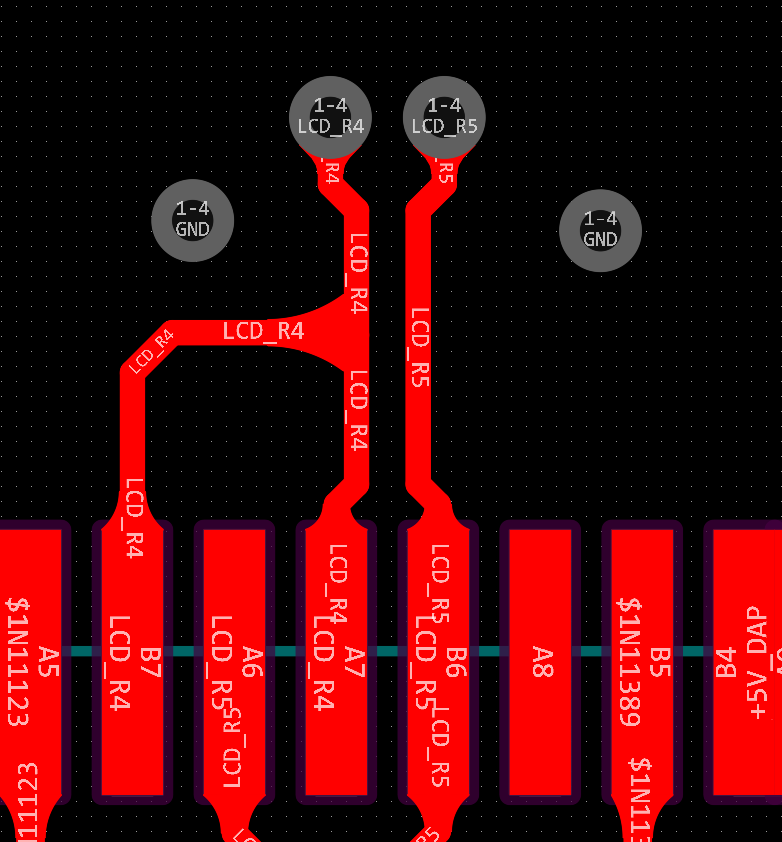

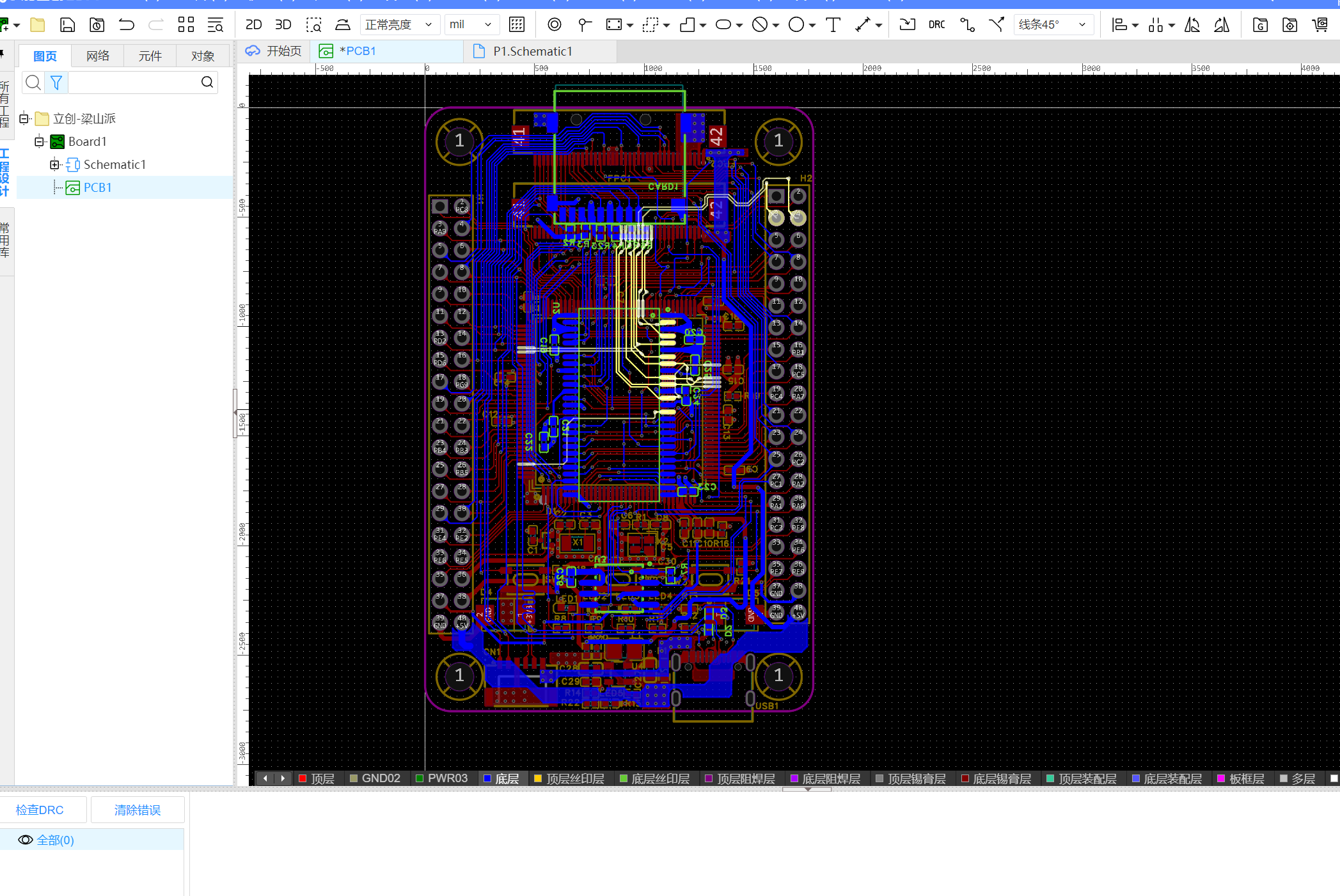

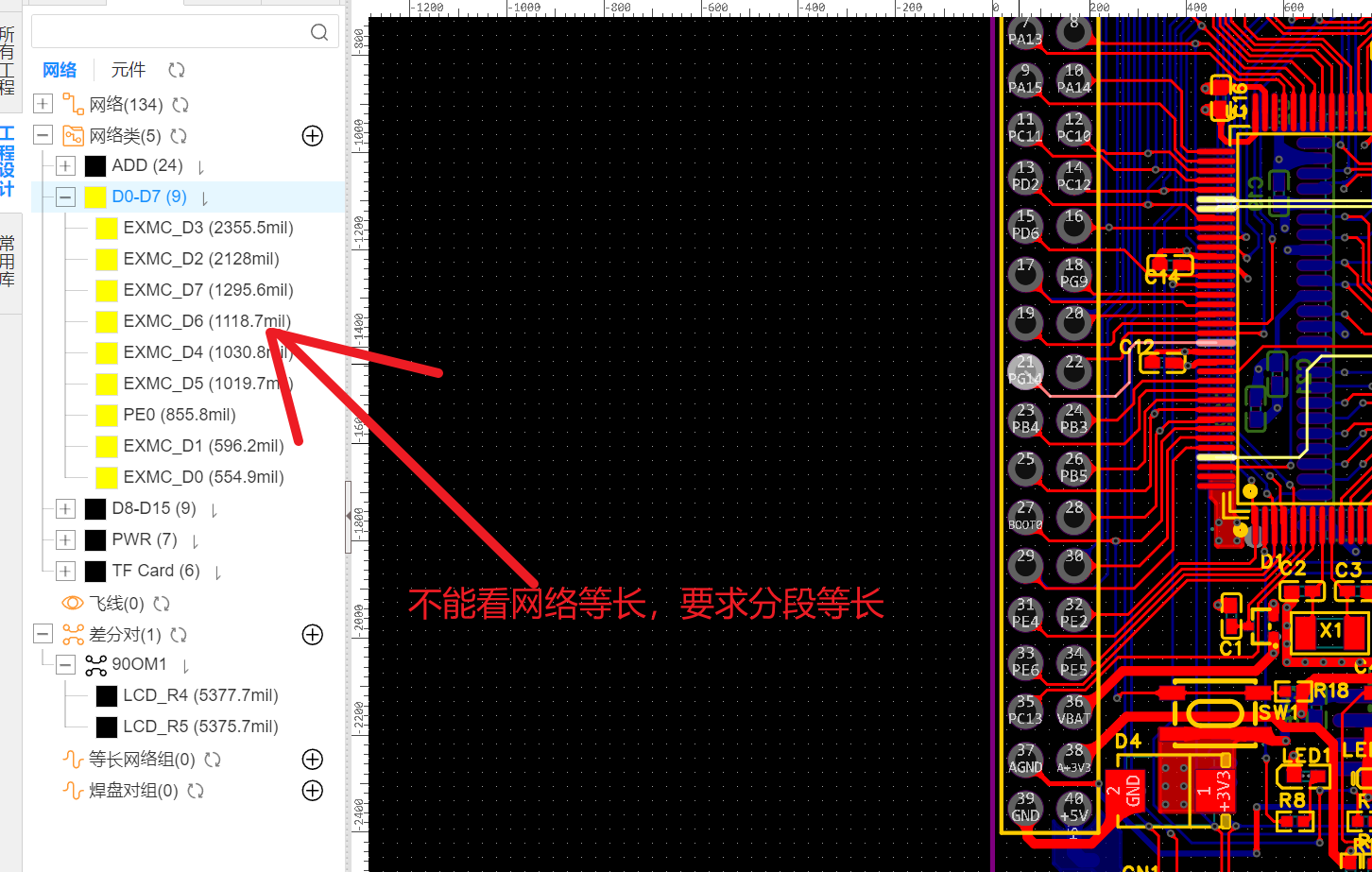

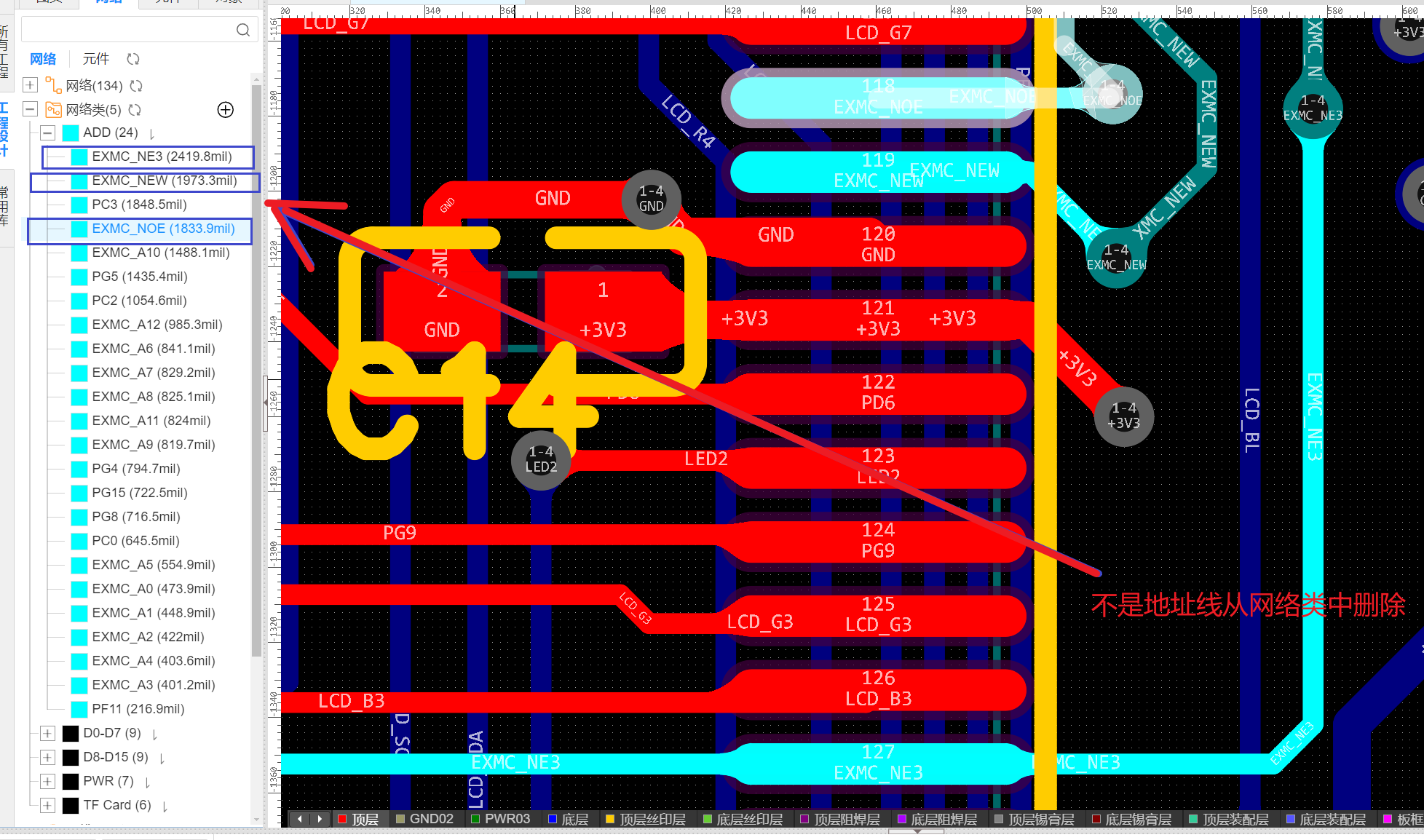

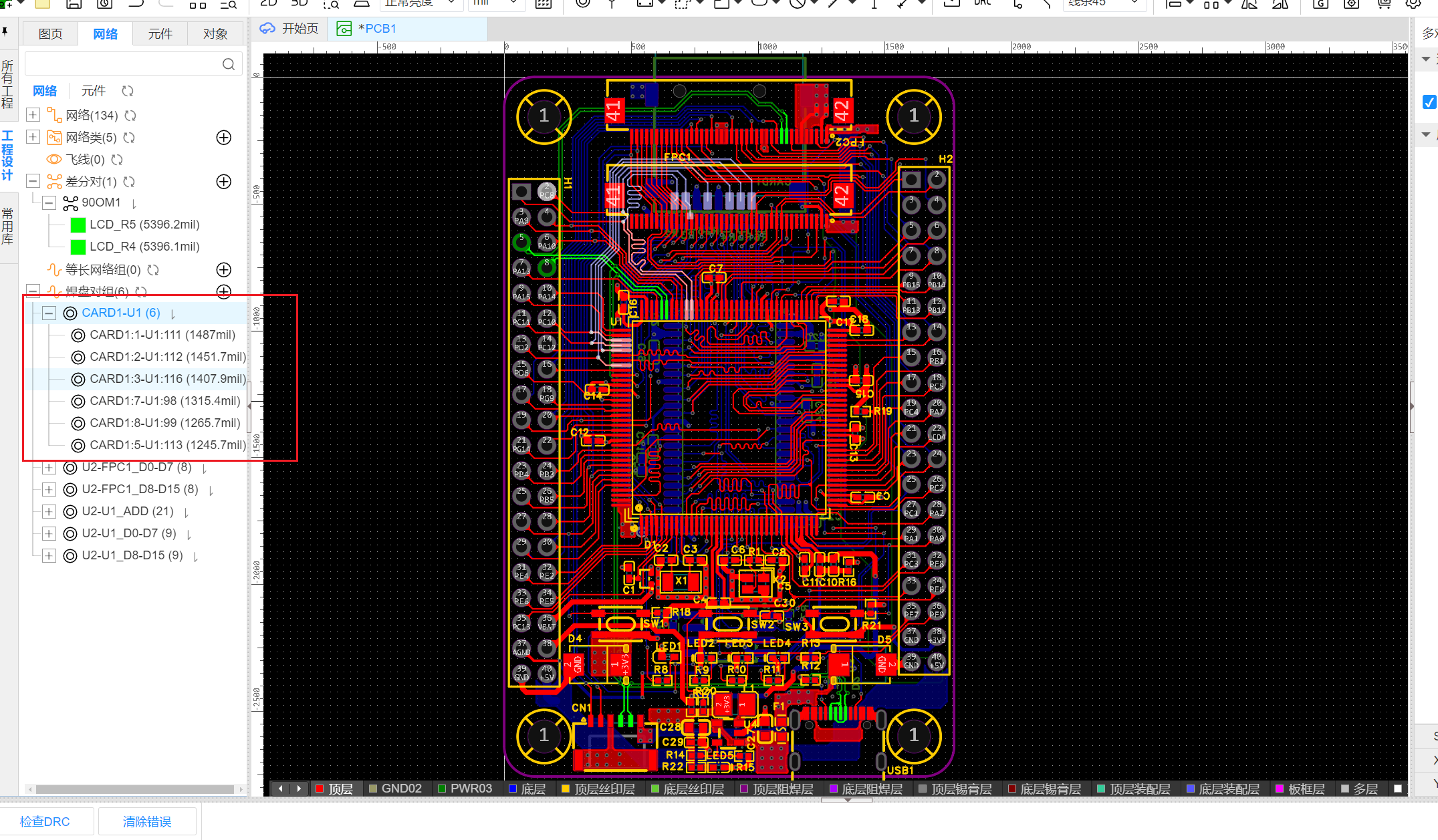

四、网络类管理及布线

1、添加网络类

注释:Ctrl+R---隐藏/显示飞线

如上图添加网络类

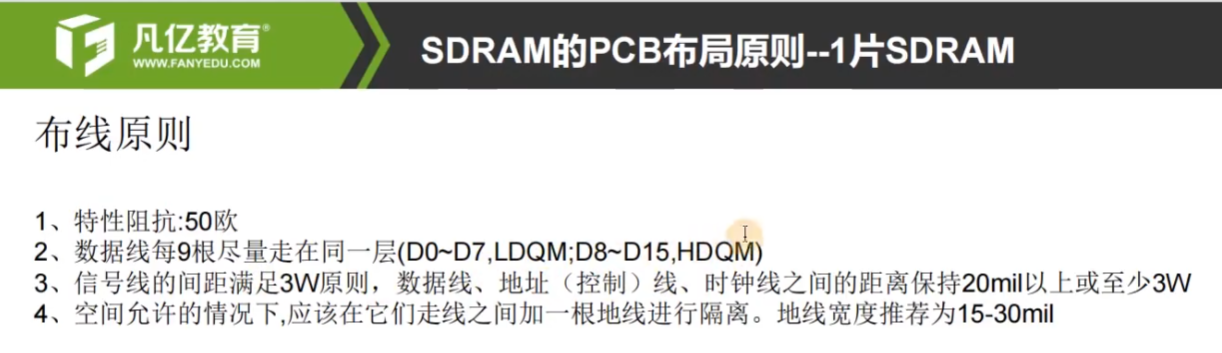

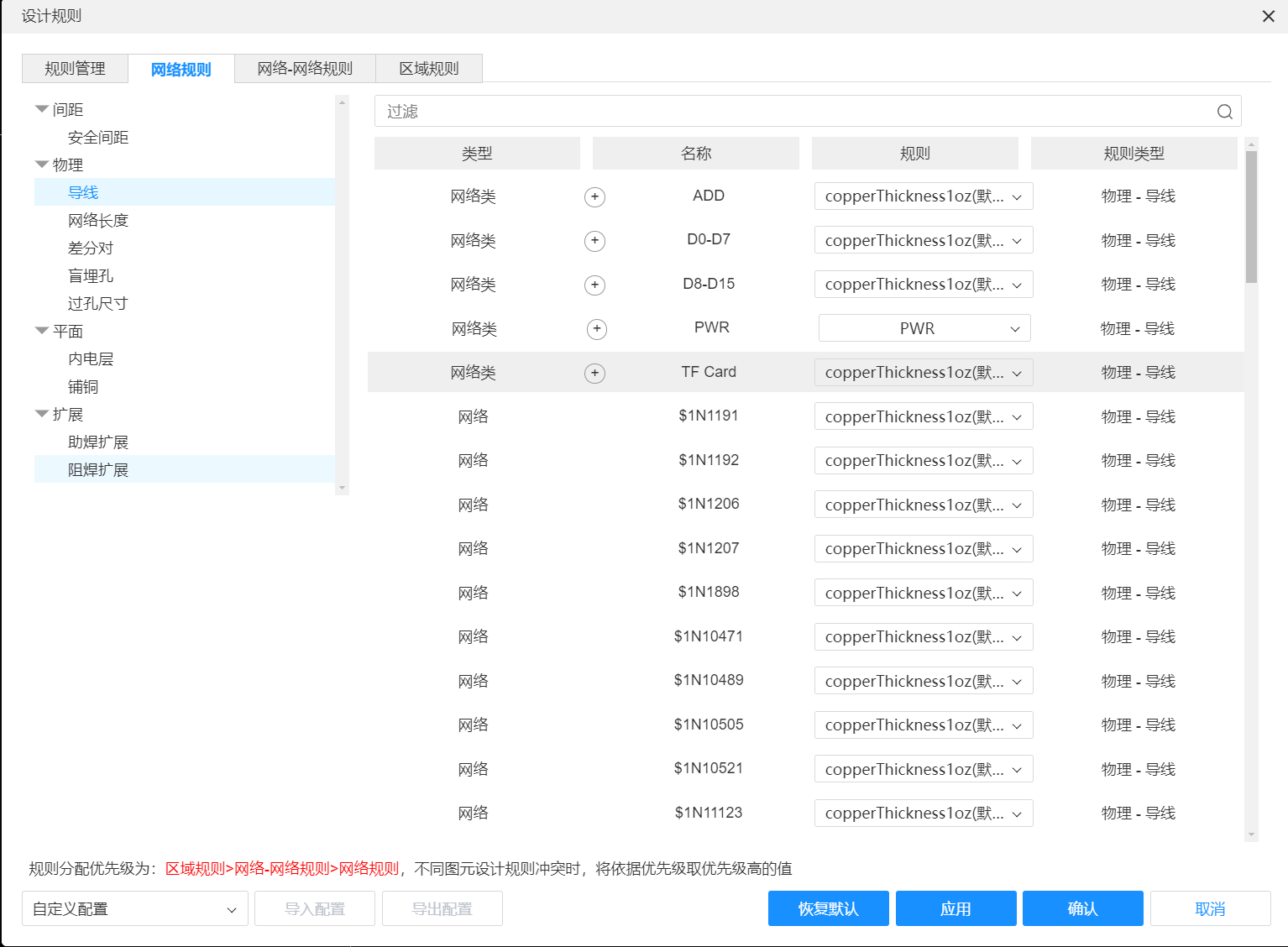

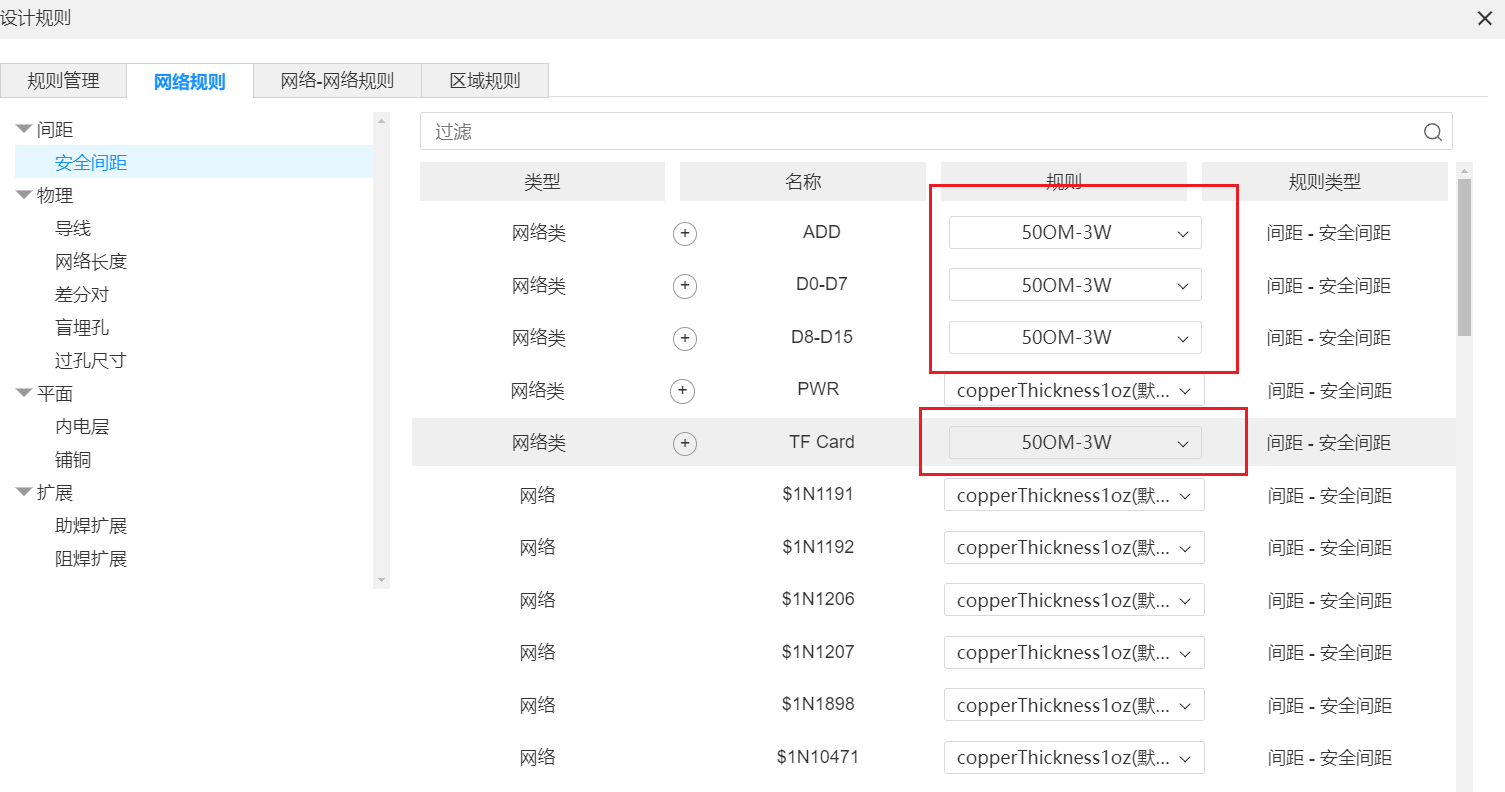

2、阻抗设计

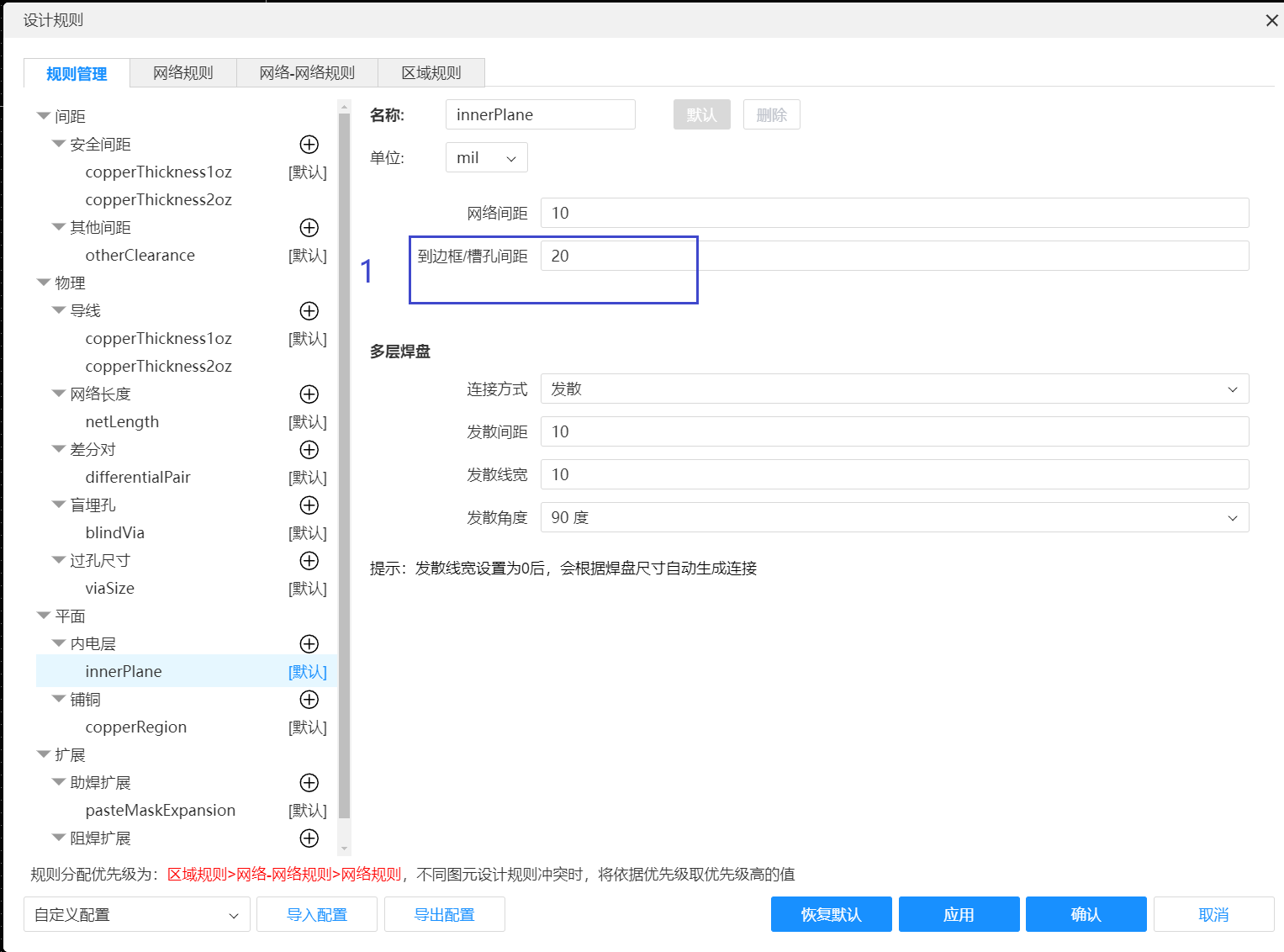

3、更改设计规则

什么叫做3W原则?

答:为了信号走线的质量,不产生串扰,我们保持信号走线与信号走线之间的间距为3倍线宽,这个间距指的是走线的中心到中心的间距,因为我们的线宽英文是width,所以这个规则我们通常就叫做3w原则。当我们的走线的中无间距不少于3倍线宽时,可以保证70%的线间电场不互相干扰,如果信号需要达到98%的线间电场不互相干扰,可以使用10W规则。

3W原则是一种设计者无须其他设计技术就可以遵守PCB布局的原则。但这种设计方法占用了很多面积,可能会使布线更加困难。使用3W原则的基本出发点是使走线间的耦合最小。这种原则可表示为:走线的距离间隔(走线中心间的距离)必须是单一走线宽度的三倍。另一种表示是:两个走线的距离间隔必须大于单一走线宽度的二倍。比如,时钟线为6mil宽,则其他走线只能在距这条走线2x6mil以外的地方布线,或者保证边到边的距离大于12mil。

4、扇孔---占位

中间可以过一根线 目的 保证地平面不被分割

回流地过孔

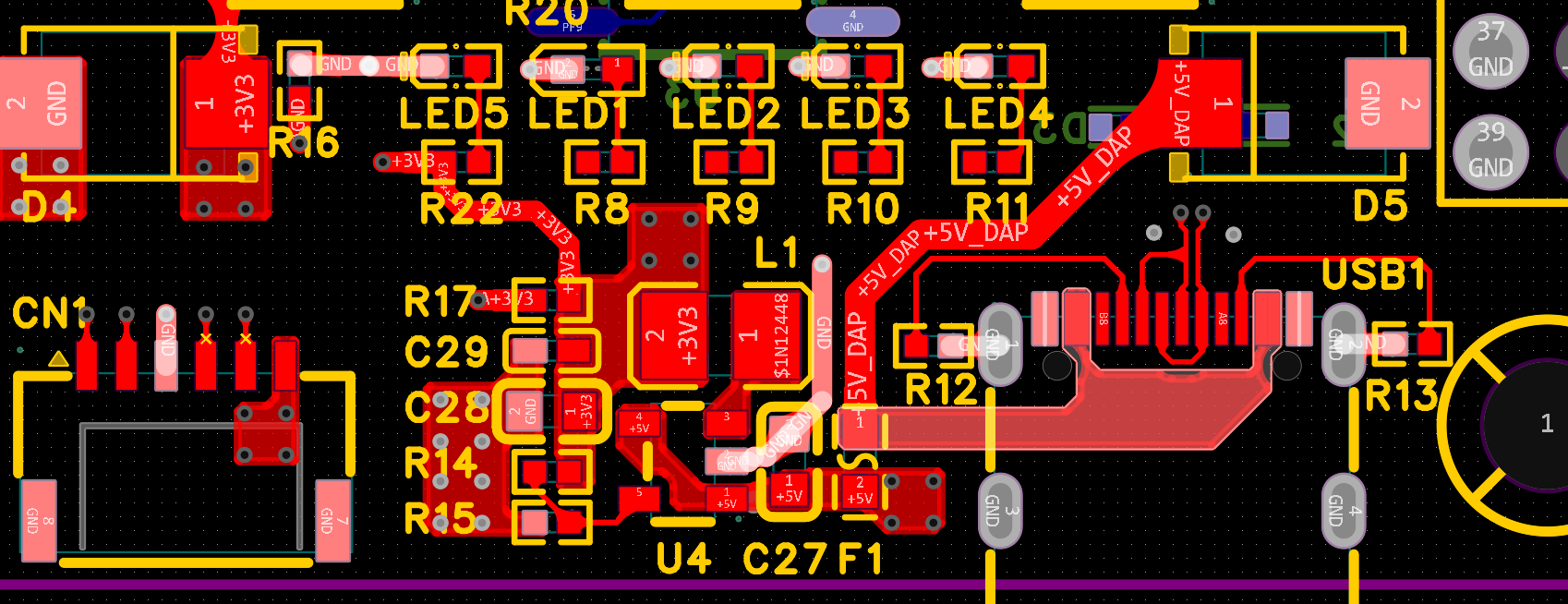

5、顶层铺铜(局部)及短线连接

铺铜对象一般为GND,+5V,+3.3V,等电源信号

6、飞线连接

一般 优先顺序 高低位数据线 地址线、电源线

注释:Ctrl+R----选中显示/隐藏飞线

Alt+T------切换顶层

AIt+B----切换底层

AIt+V----放置过孔

AIt+E----铺铜

Alt+I----更新/转换原理图到PCB

Ctrl+Z--撤回

Shift+H-----高亮选中网络

Alt+F----对称(左右)

Shift+A-----等长调节

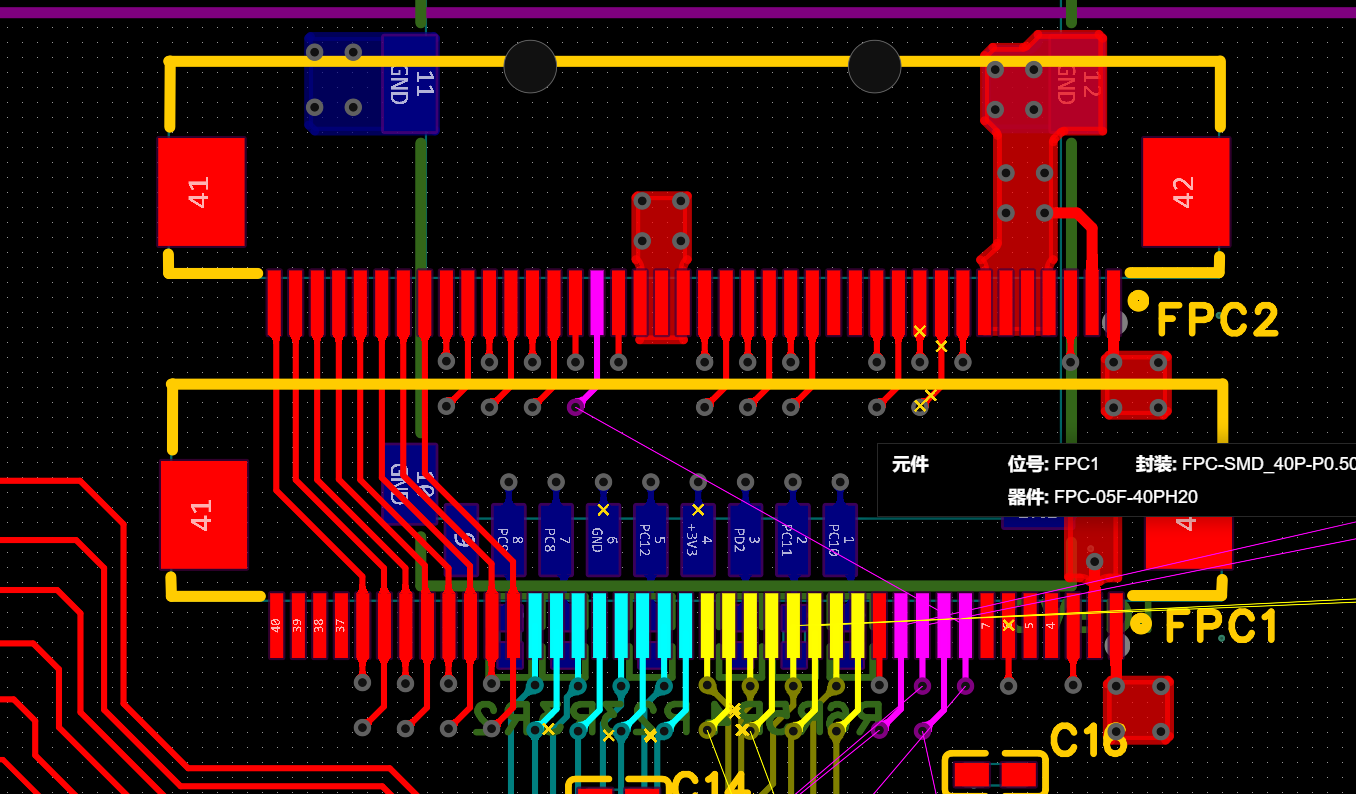

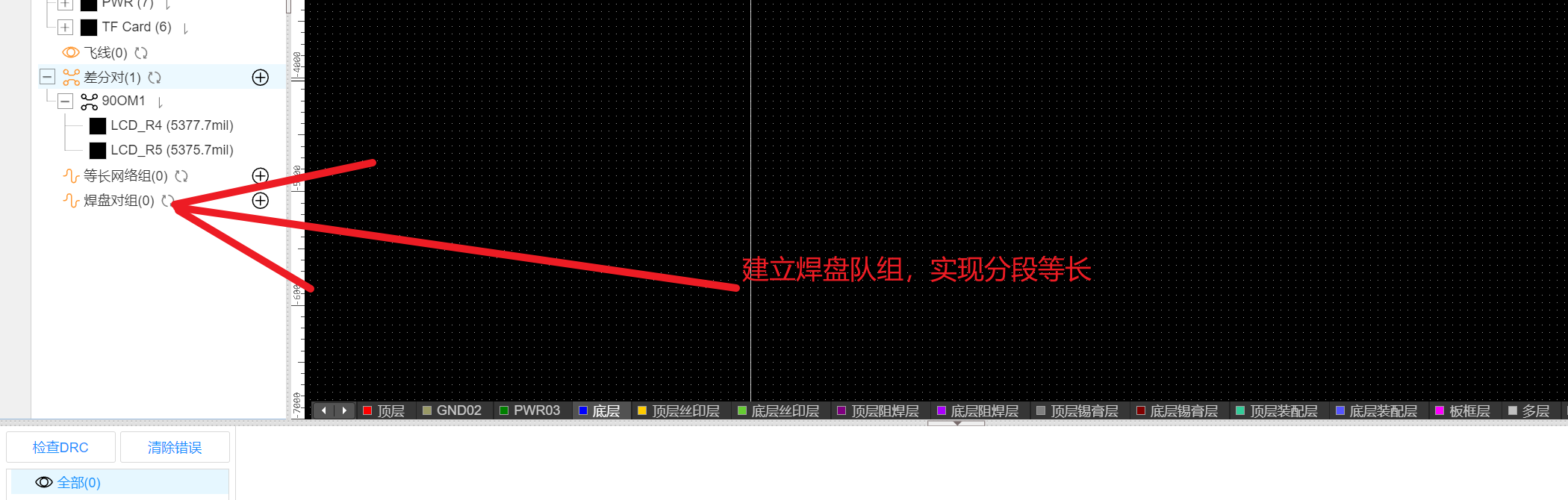

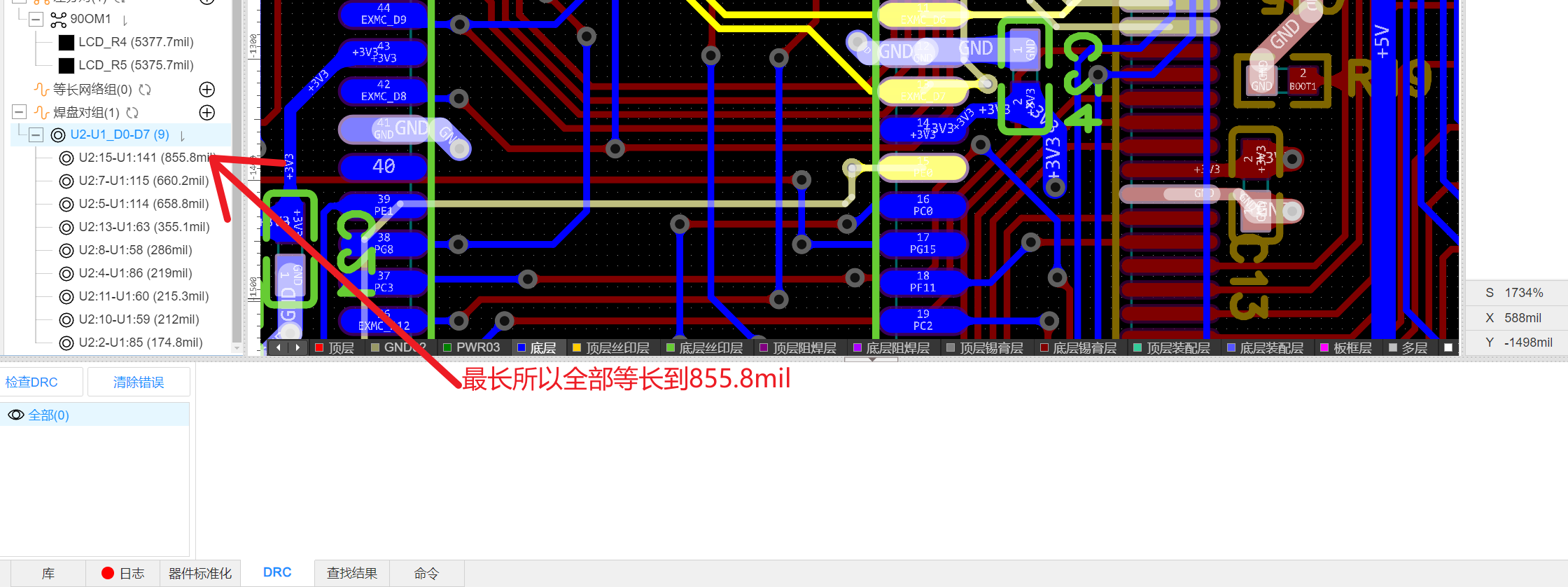

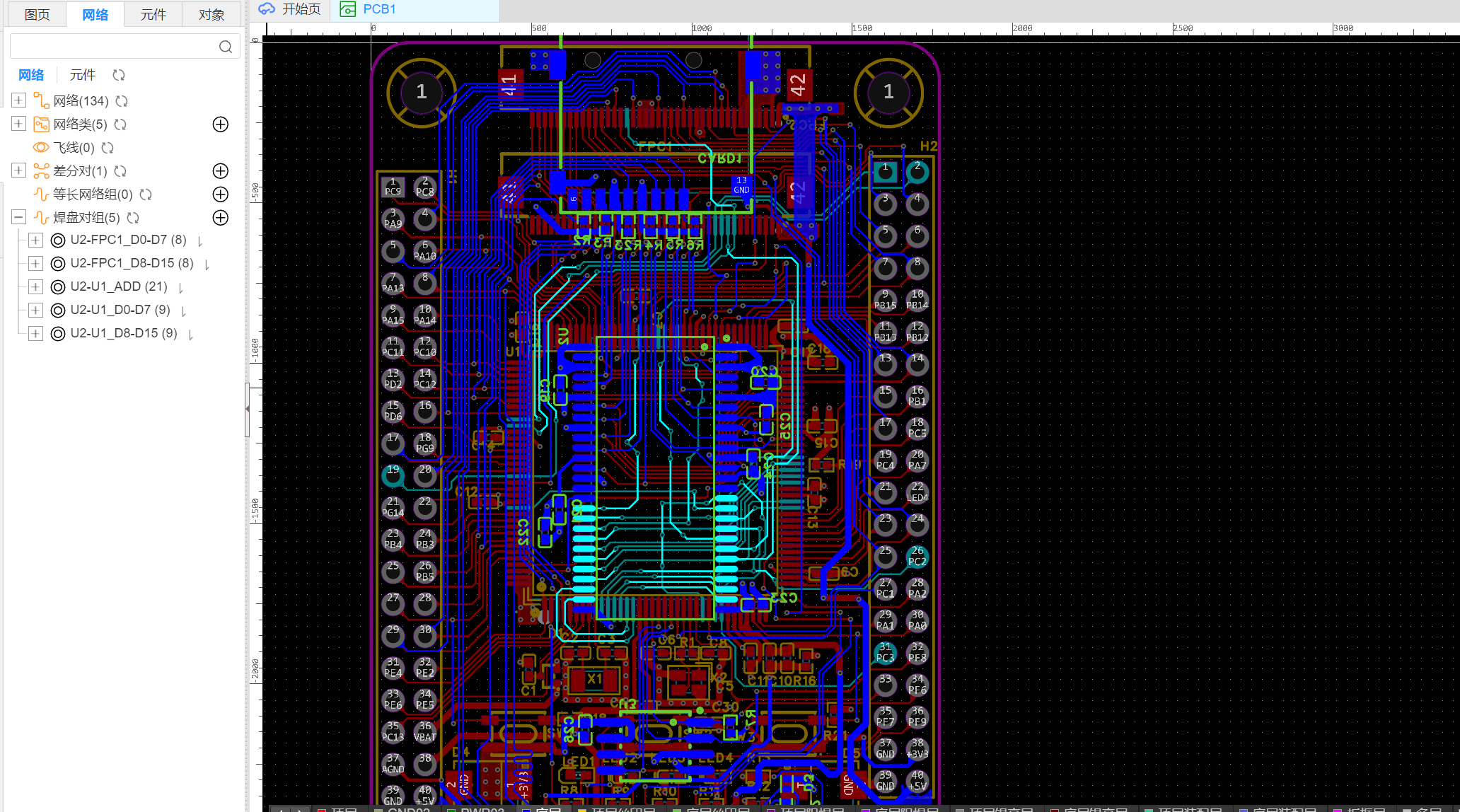

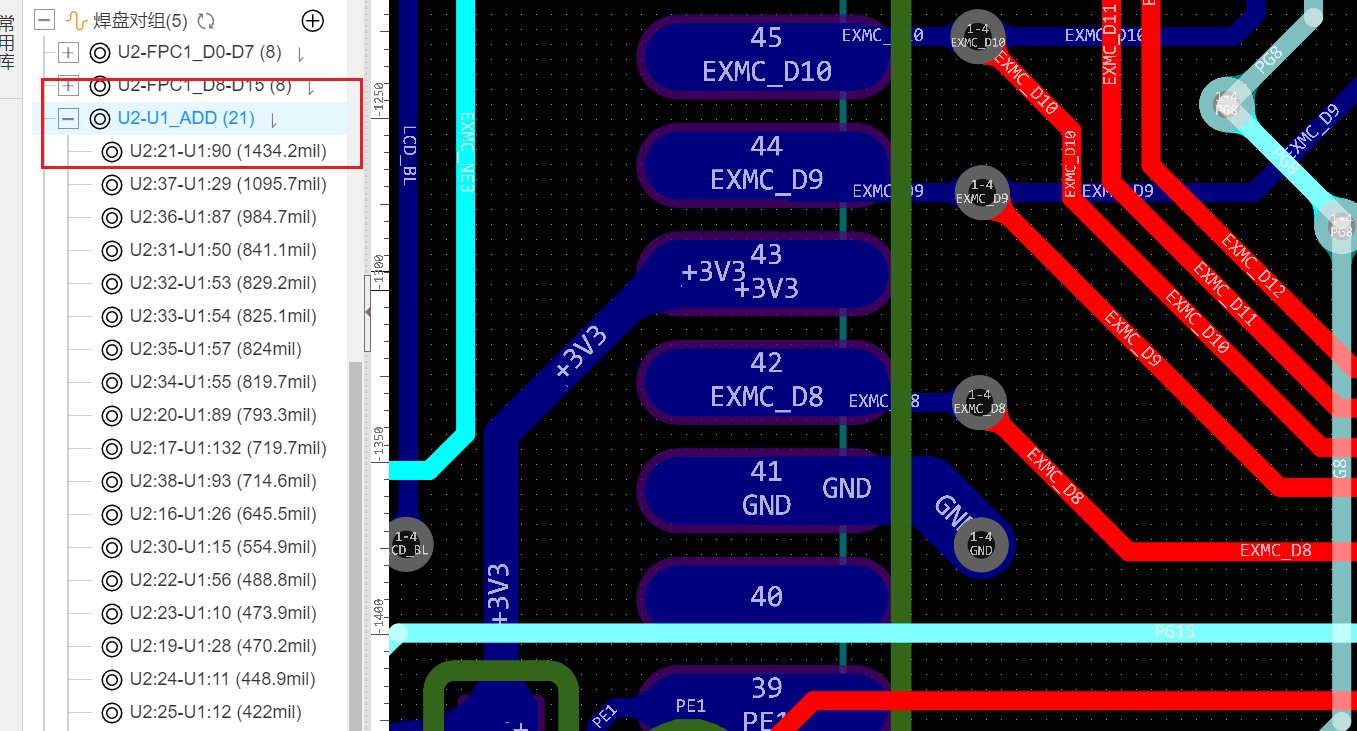

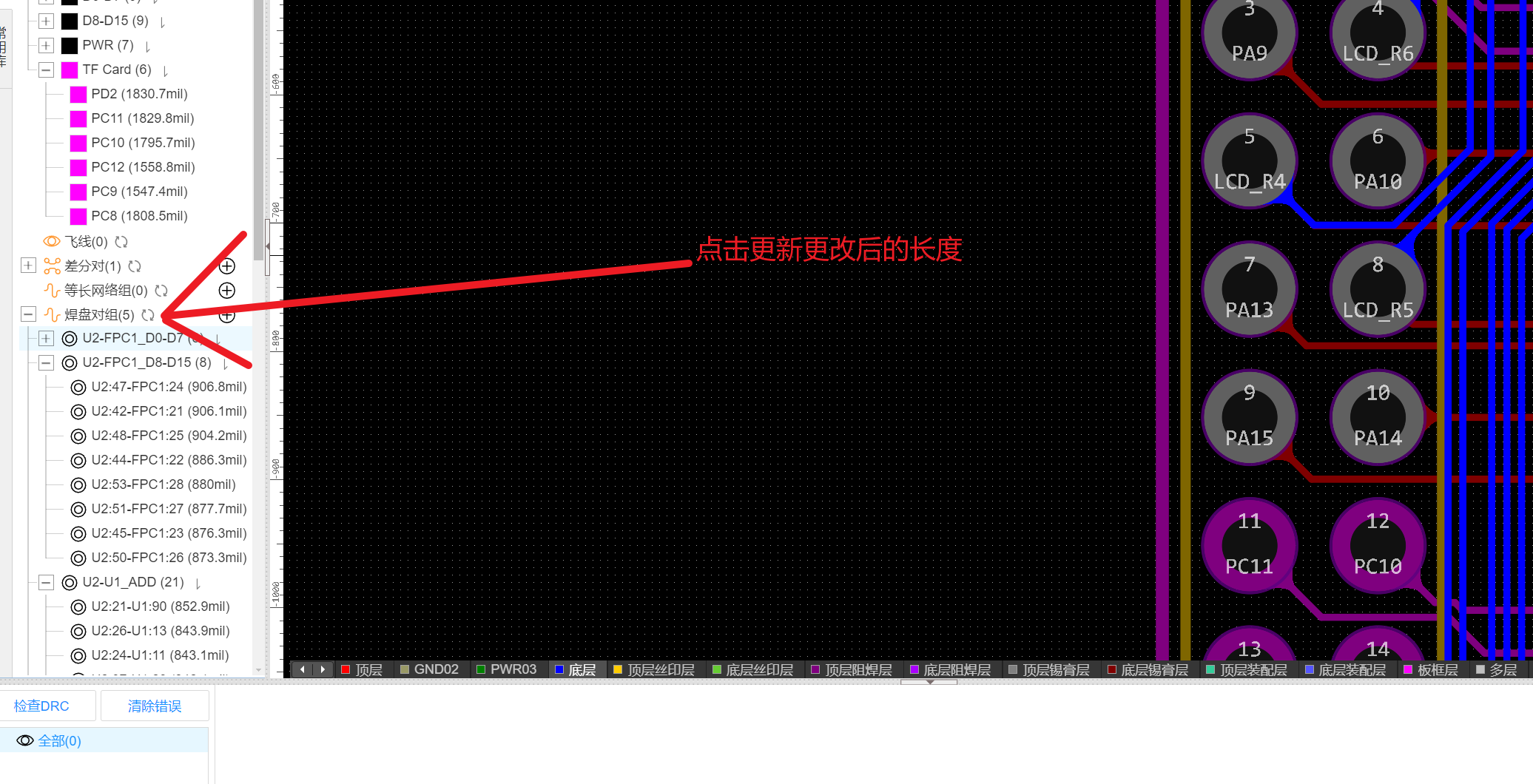

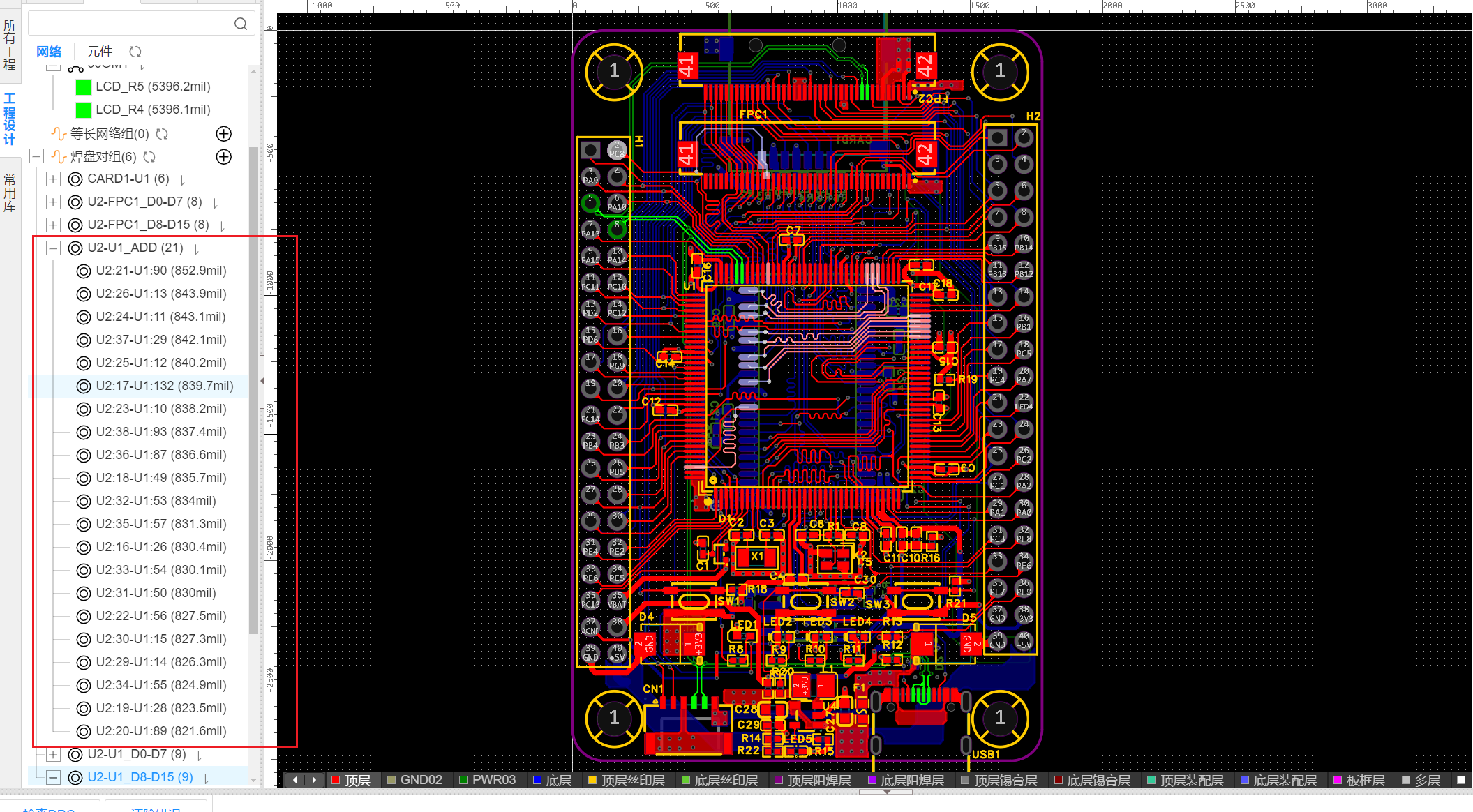

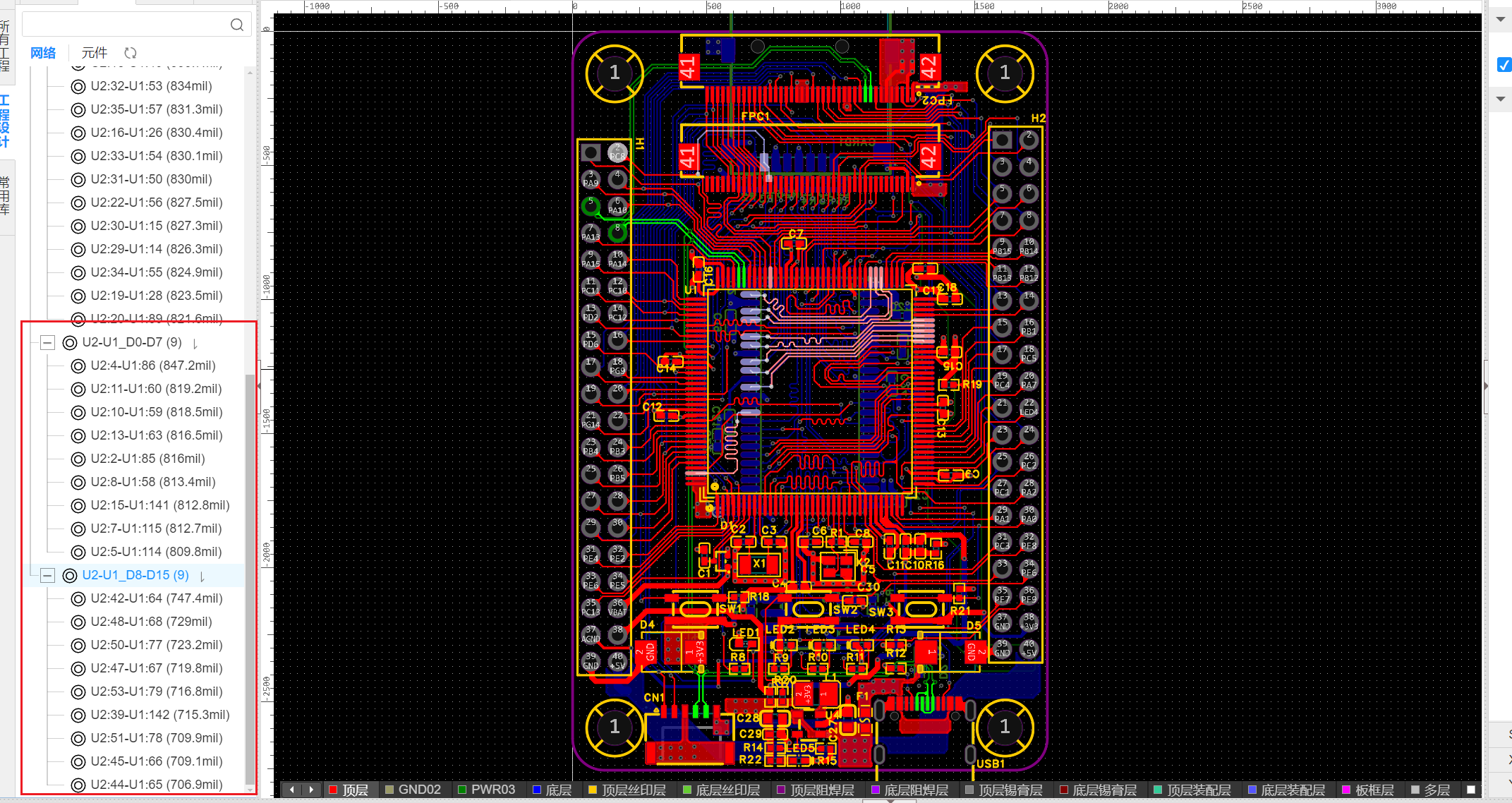

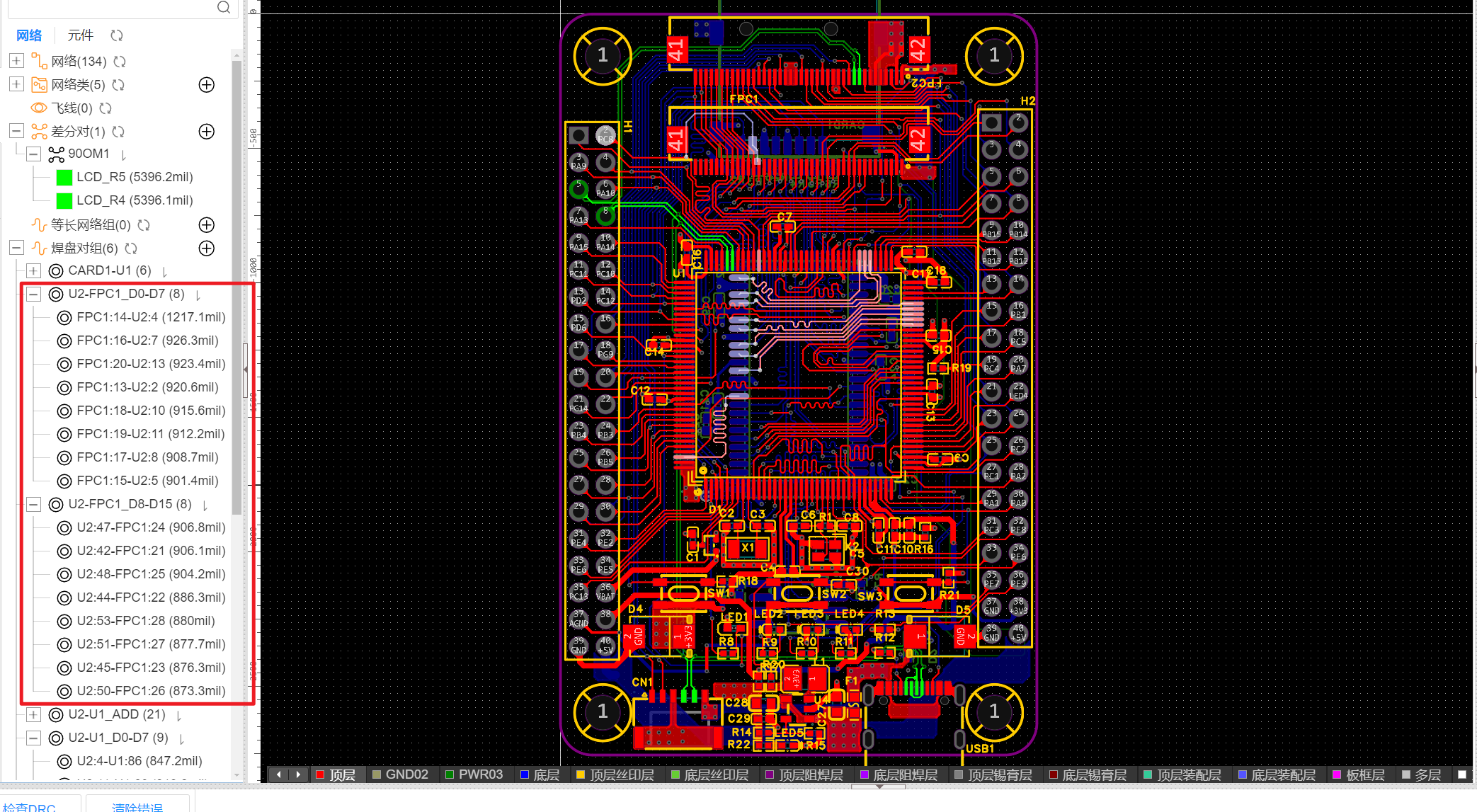

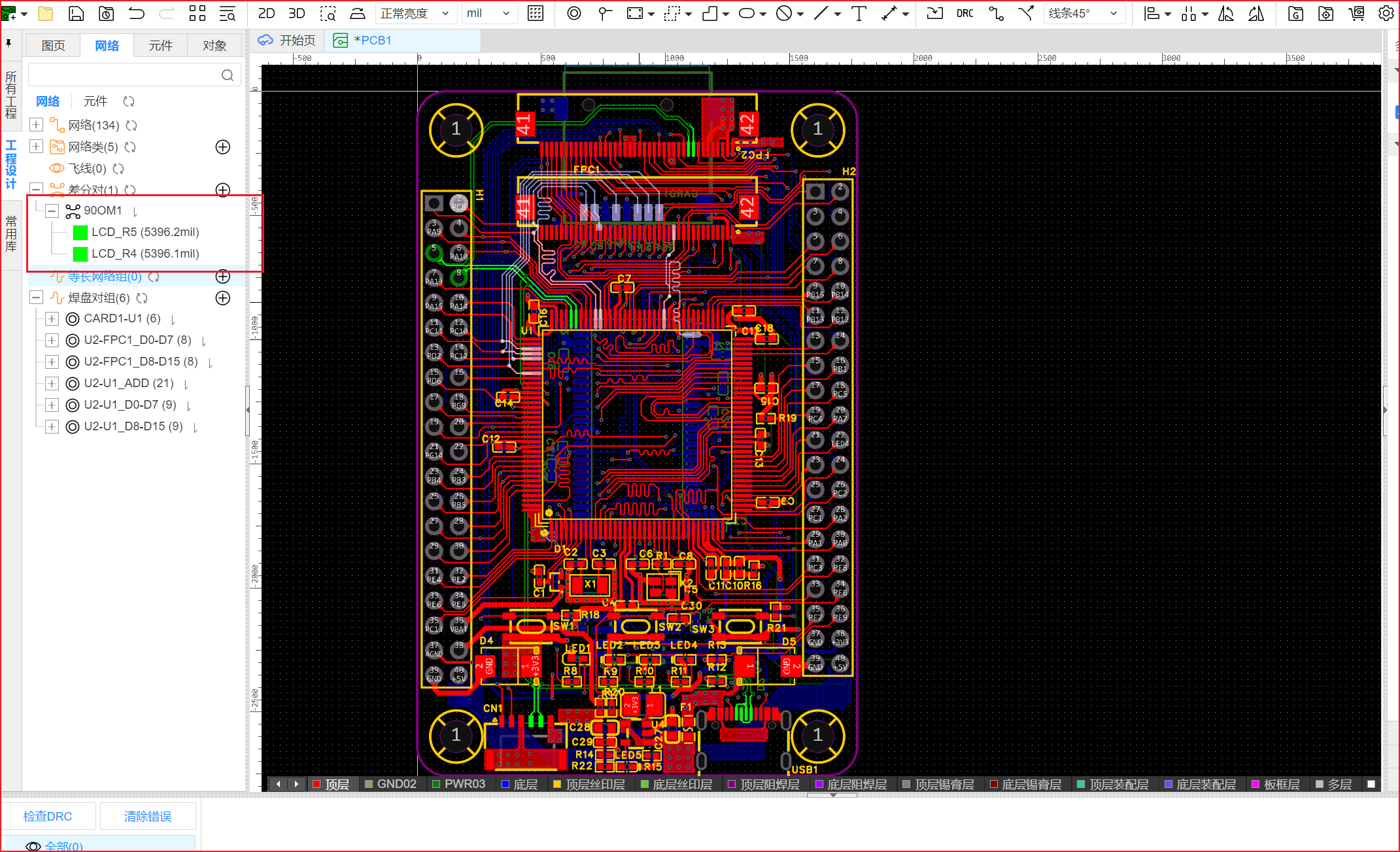

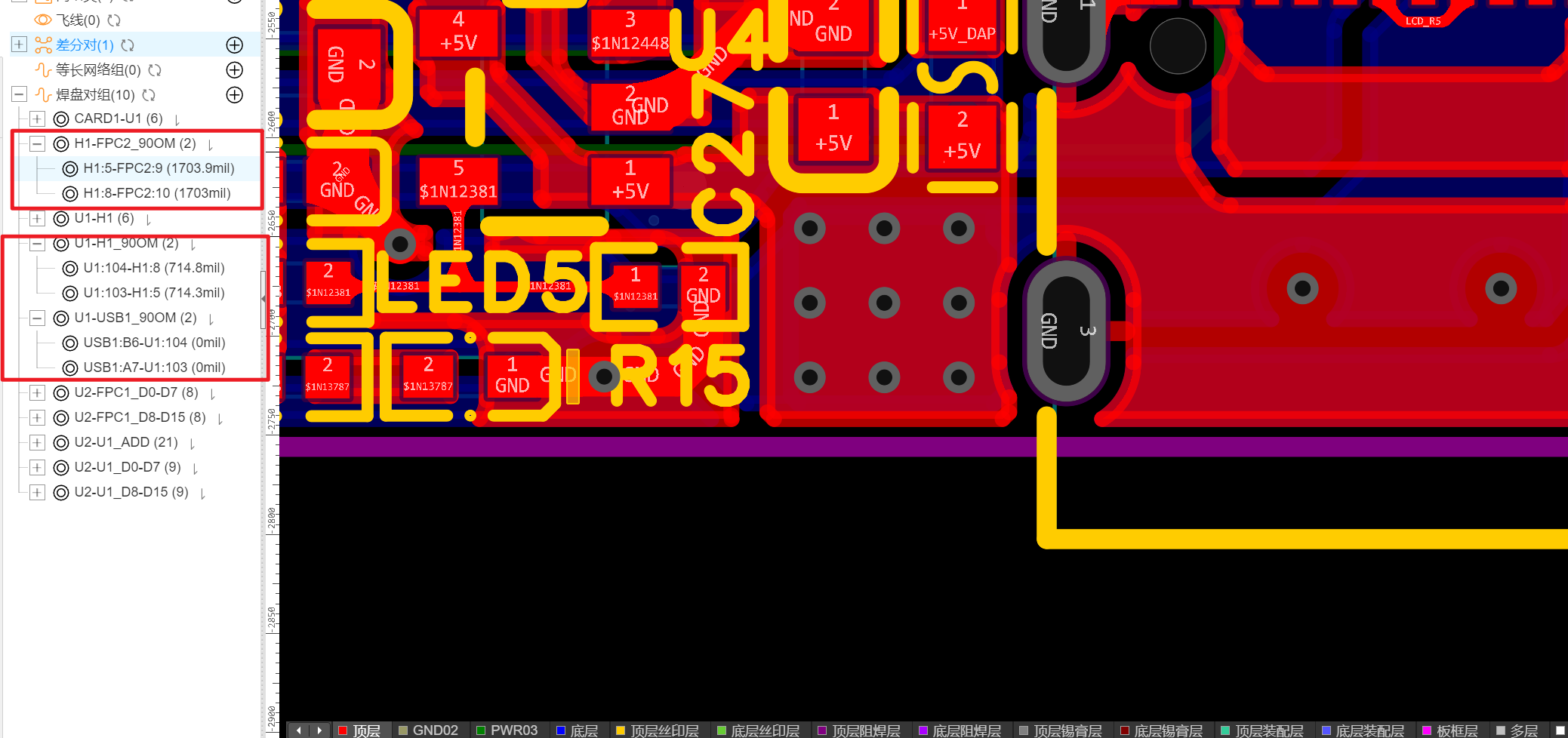

7、等长网络焊盘组的介绍与建立

器件1到器件2的距离

U2到U1的距离

添加不了重新布线,后在添加

没有连接到U2不属于地址线

SDRAM地址信号线,高八位,低八位等长处理(<50mil)

优先考虑能否缩短处理,其次处理最短的线

TF Card与差分对等长处理(TF Card误差300mil)

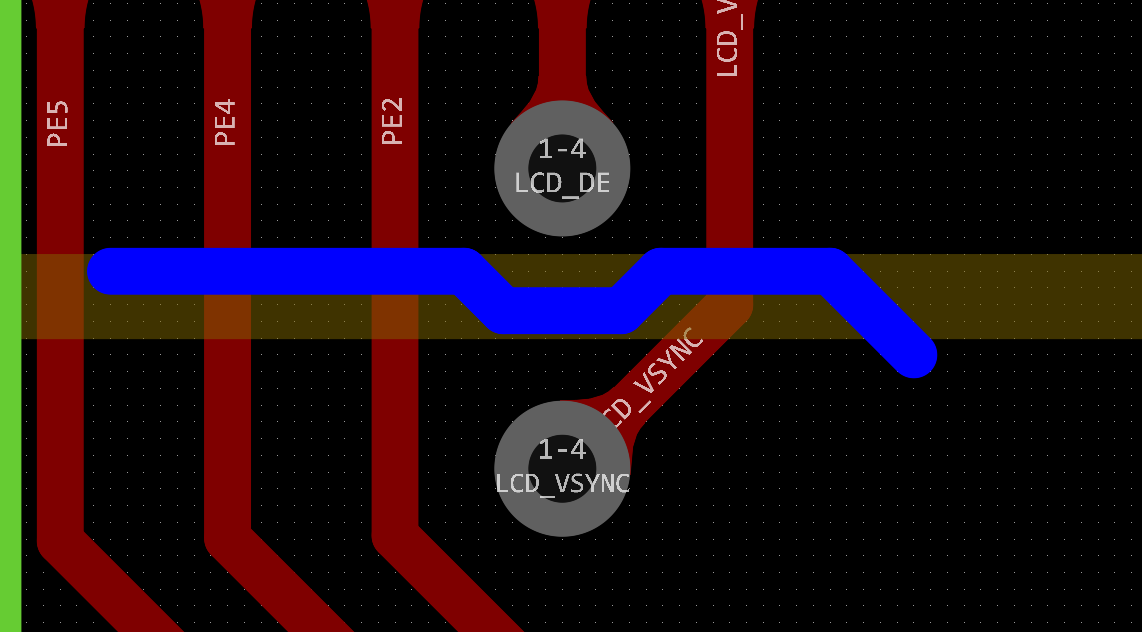

差分对要求耦合

注释:

一、核心思想:什么是差分对耦合?

简单来说,差分对耦合是指在PCB布局中,确保构成差分对的两根信号线(正端D+和负端D-)在整个走线路径中保持紧密、平行、等距且等长的一种设计实践。

你可以把它想象成一对形影不离的舞伴:

-

他们必须紧挨着对方(紧密间距)。

-

他们必须朝同一个方向移动(平行走线)。

-

他们必须保持相同的步伐和速度(等长、阻抗一致)。

耦合的终极目标是:确保任何外部干扰都能同时、同等地影响到这两根线。

二、为什么耦合如此重要?

要理解其重要性,我们需要回忆一下差分信号的工作原理和优势:

-

抗共模噪声

-

场景: 旁边有一根干扰源(比如电机驱动线),产生了噪声。

-

耦合时: 因为D+和D-紧靠在一起,噪声会同时、等量地耦合到这两根线上。接收器只关心两者之间的电压差(D+) - (D-)。由于噪声被同时加入,电压差保持不变,噪声被完美抵消。

-

不耦合时: 如果两根线分开走,噪声可能只影响其中一根,或者对两根线的影响程度不同。这个差异会被接收器误认为是有效信号,导致错误。

-

-

控制电磁辐射

-

场景: 电流流过导线会产生磁场。

-

耦合时: D+和D-上的电流大小相等、方向相反。它们产生的磁场也方向相反。由于两根线紧靠在一起,这些磁场会相互抵消,从而显著降低对外的电磁干扰(EMI)。

-

不耦合时: 两根线像两个独立的天线,各自辐射电磁波,总辐射量很大,产品可能无法通过EMC测试。

-

-

保证信号完整性

-

关键概念: 差分阻抗(Z_diff)。这是一个非常重要的特性阻抗,通常为90Ω或100Ω。它取决于:

-

线宽(W)

-

线与线之间的间距(S)

-

介质厚度(H)

-

-

耦合时: 保持S恒定,就能保证Z_diff恒定。信号在传输过程中不会遇到阻抗突变,从而避免反射、振铃等信号完整性问题。

-

不耦合时: 间距S忽大忽小,会导致Z_diff不断变化,引起信号反射,劣化信号质量。

-

三、如何实现有效的耦合?(物理布局规则)

在实际的PCB设计中,耦合是通过遵循一系列严格的布局规则来实现的:

-

紧耦合原则:

-

规则: 通常要求差分对的两线边缘间距(S) ≤ 2倍的线宽(W)。有些更严格的设计要求 S = W。

-

目的: 确保两根线足够近,让外部干扰成为“共模”干扰。

-

-

等距与平行:

-

规则: 在整个走线路径中,D+和D-之间的间距必须保持恒定,并且尽可能平行走线。

-

目的: 保证差分阻抗的连续性。

-

-

等长匹配:

-

规则: D+和D-的电气长度必须严格相等。在布线后,需要用软件测量长度差,并通过走“蛇形线”来补偿较短的哪一根。

-

容差: 高速总线(如PCIe, USB 3.0)的等长要求非常苛刻,可能要求在5mil(0.127mm)甚至更小的误差范围内。

-

目的: 确保信号的反向边沿同时到达接收端,否则差分信号会变成“非理想”信号,共模噪声抑制能力下降,眼图会闭合。

-

-

提供完整的参考平面:

-

规则: 差分对下方必须有一个完整、无割裂的参考平面(通常是GND,有时是电源)。

-

目的: 为信号提供明确的返回路径,是控制阻抗和保证信号质量的基础。

-

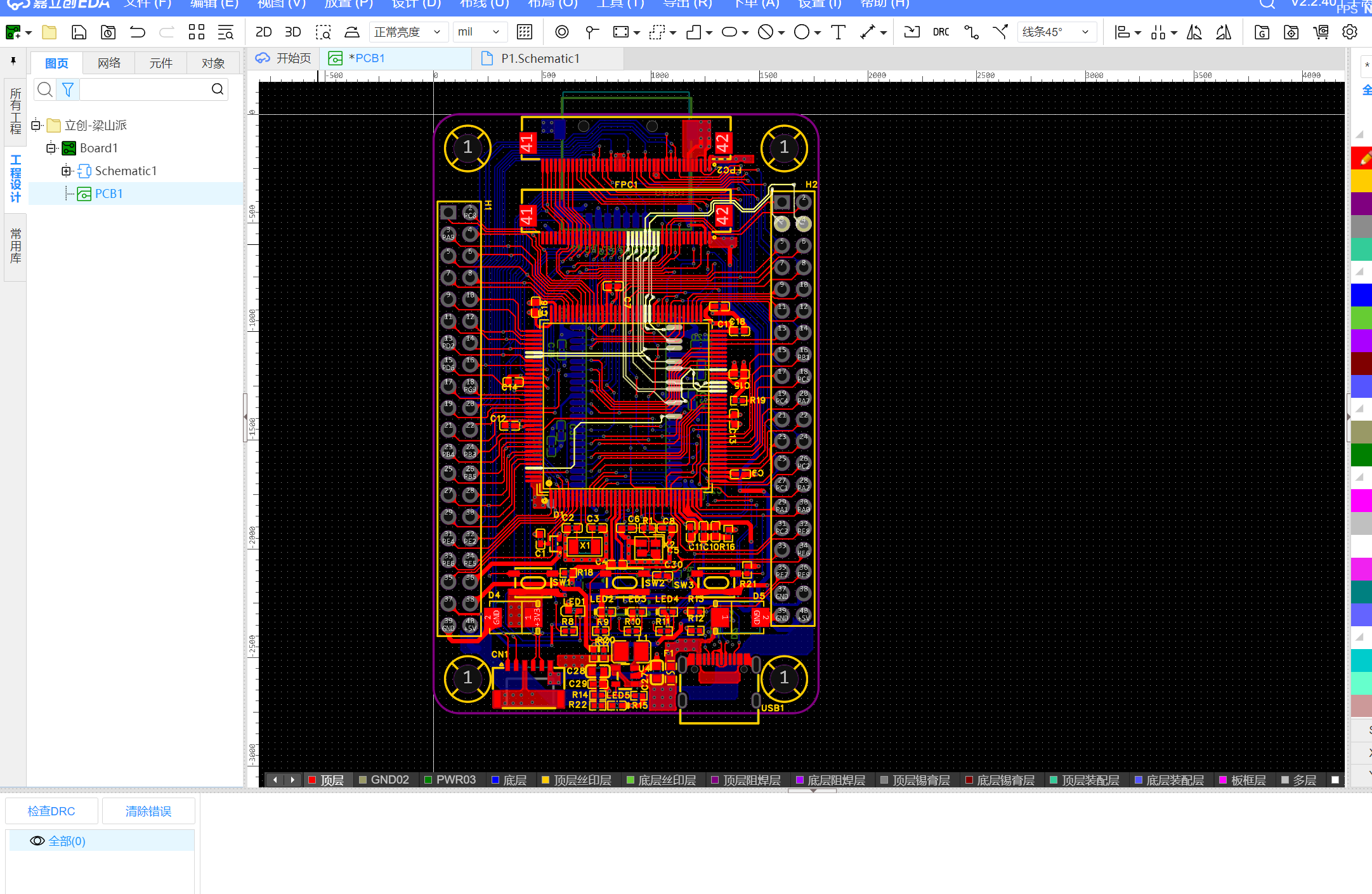

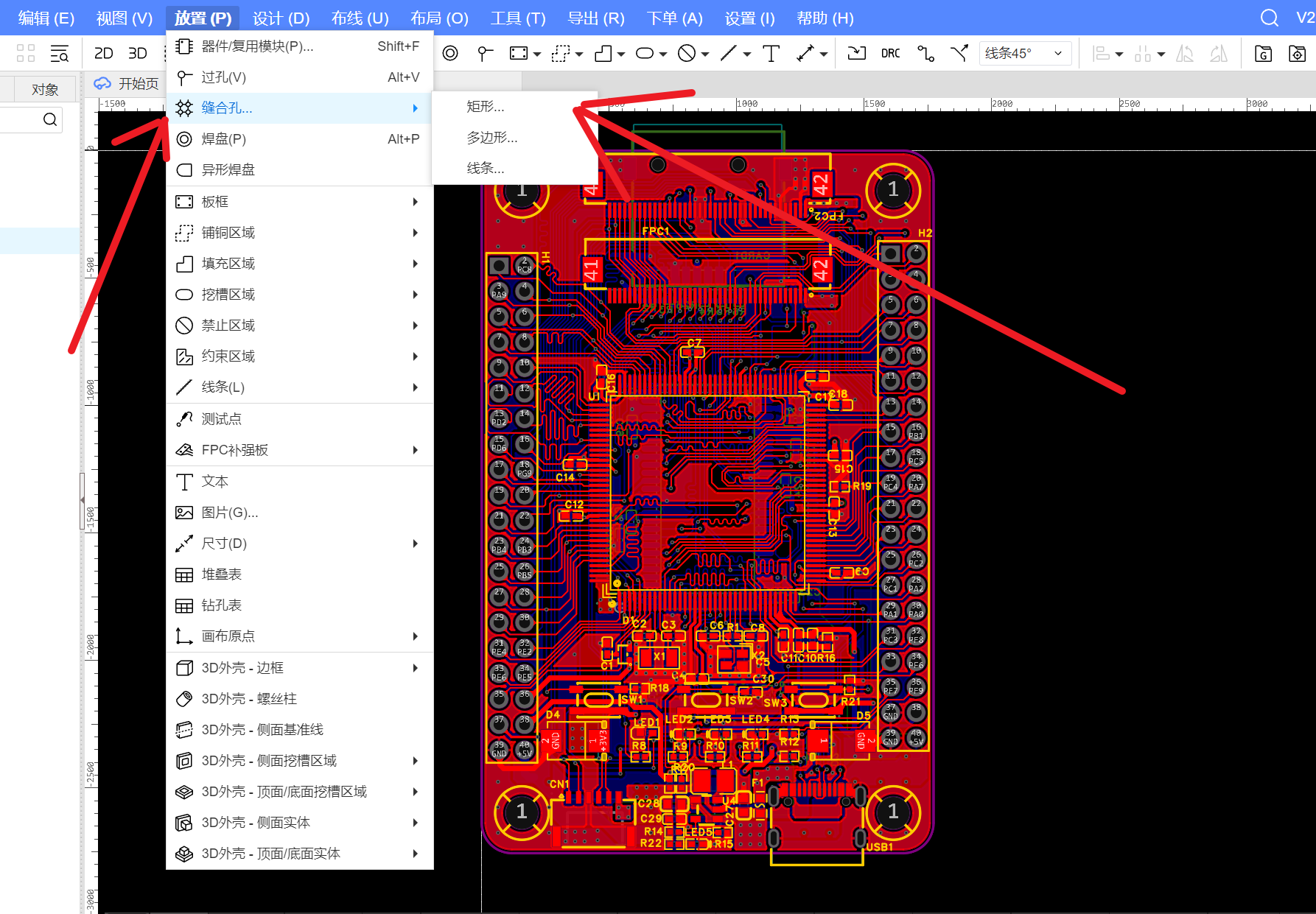

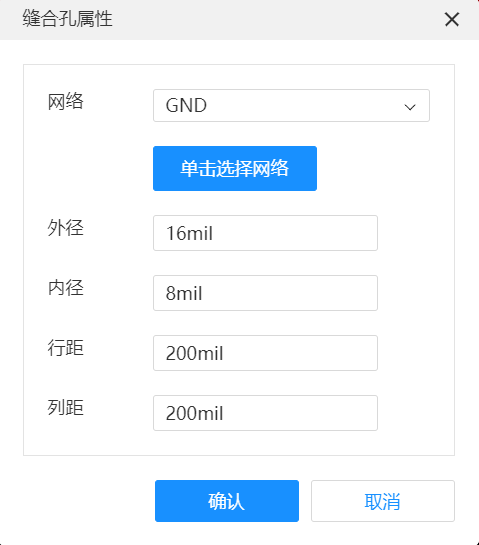

五、铺铜及添加缝合孔

1、铺铜

2、添加缝合孔(GND)

888

888

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?