简介

Appium 是一个开源的自动化测试工具,支持 Android、iOS 平台上的原生应用,支持 Java、Python、PHP 等多种语言。

Appium 封装了 Selenium,能够为用户提供所有常见的 JSON 格式的 Selenium 命令以及额外的移动设备相关的控制命令,比如:多点触控手势、屏幕朝向等。

很多人学习python,不知道从何学起。

很多人学习python,掌握了基本语法过后,不知道在哪里寻找案例上手。

很多已经做案例的人,却不知道如何去学习更加高深的知识。

那么针对这三类人,我给大家提供一个好的学习平台,免费领取视频教程,电子书籍,以及课程的源代码!??¤

QQ群:623406465

环境

本文主要环境如下:

-

Win7

-

JDK1.8

-

Appium

-

Python3.7

-

android-sdk

-

mumu 模拟器

JDK

下载地址: https://www.oracle.com/java/technologies/javase/javase-jdk8-downloads.html,也可在文末直接获取

配置环境变量:

-

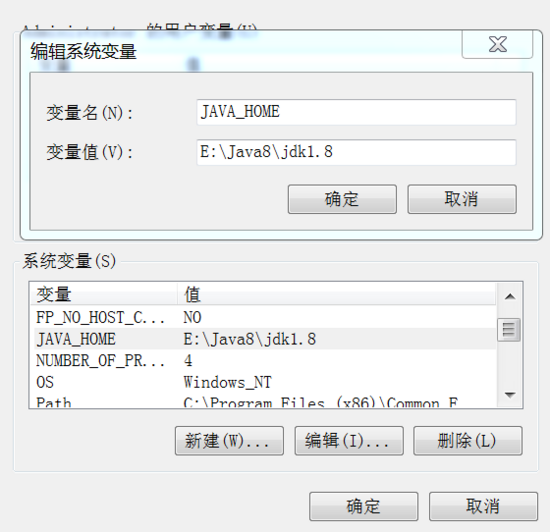

计算机(右键)->属性->高级系统设置->高级->环境变量->新建环境变量

JAVA_HOME,如图所示:

-

系统变量->找到

Path变量->编辑->在变量值的末尾添加;%JAVA_HOME%\bin;%JAVA_HOME%\jre\bin; -

新建

CLASSPATH变量,变量值为:.;%JAVA_HOME%\lib;%JAVA_HOME%\lib\tools.jar

android-sdk

下载地址: https://www.androiddevtools.cn/ ,也可在文末直接获取

配置环境变量:

-

与 JDK 配置类似,新建环境变量

ANDROID_HOME,变量值为android-sdk位置,比如:D:\android-sdk-windows -

在

Path变量值的末尾添加

本文介绍了使用Python和Appium进行Android平台上的微信自动化操作,包括环境配置(JDK, android-sdk, Appium, mumu模拟器)和实际操作(启动微信、添加好友、发送消息)。详细讲解了如何通过Appium定位和交互微信应用中的元素。"

130467471,8077481,华为面试题:求不含101的二进制数数量,"['算法', '开发语言', 'java']

本文介绍了使用Python和Appium进行Android平台上的微信自动化操作,包括环境配置(JDK, android-sdk, Appium, mumu模拟器)和实际操作(启动微信、添加好友、发送消息)。详细讲解了如何通过Appium定位和交互微信应用中的元素。"

130467471,8077481,华为面试题:求不含101的二进制数数量,"['算法', '开发语言', 'java']

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1392

1392