上讲我们介绍了SRIO的一些基础知识,例如SRIO系统架构,HELLO包格式,以及相对应的时序等。了解了这些基础知识后,我们就来学习一下怎么去使用SRIO IP。大家通过第一讲的学习可能会觉得SRIO的内容实在是太多了,但是它使用起来是非常简单的,通过本文的学习,相信大家都能够学会SRIO IP的使用,咱们接着往下看。

1.设计流程步骤

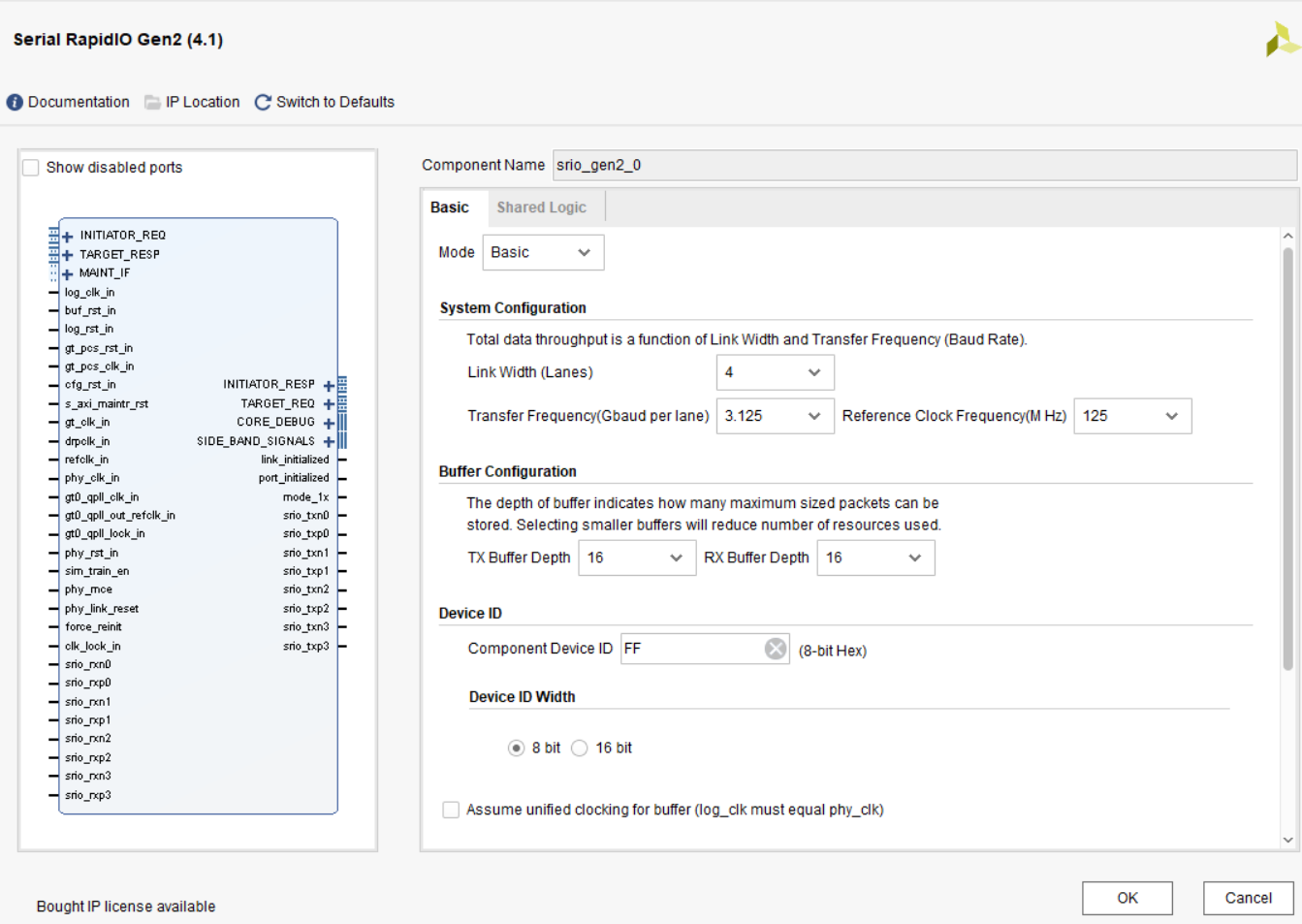

首先我们先从vivado中打开SRIO IP,如图所示:

**Mode:**可以选择Basic模式和Advanced模式,区别就是高级模式包括所有配置选项,而基本模式在单个页面上仅显示一组简化的常用选项。一般情况下,Basic模式已经能够满足我们的需求了,因此我们就以Basic模式为例,给大家介绍SRIO IP的使用。

**Link Width:**链路宽度表示每个方向生成的串行通道的数量。Serial RapidIO Gen2内核可以有一个、两个或四个通道。系统的带宽随着通道的数量而增加。在这里需要给大家强调的一点就是,通道数的增加,并不会增加SRIO传输数据的位宽。

这里要注意和Aurora进行区分。那么增加通道的数量会带来什么影响呢,没错,就是速率的影响,它会把SRIO的输出时钟log\_clk的频率提高,由于数据位宽一直都是64bit,并且数据的传输就是在log\_clk下进行的,那么,通道数增加,也就意味着数据传输的速率变快了。

**Transfer Frequency:**传输频率表示Serial RapidIO内核的每通道波特率。每个串行收发器以选定的线路速率运行。系统的带宽随着传输频率的增加而增加。那么它与log\_clk的关系是什么呢,其实可以简单理解为log\_clk=线速率\*通道数/80,除以80的原因是SRIO也是采用8/10B编码,所以64bit数据就需要16bit的开销。那如果线速率是3.125Gbps,1通道,log\_clk的时钟周期就25.6ns。

最后再补充一句,如果我们查阅官方给的手册会发现,有太多个时钟了,比如phy\_clk,gt\_clk,gt\_pcs\_clk等,但是其实我们实际上使用的就只有逻辑时钟,其他那些时钟只需要大概了解一下就行,当然以上说的这些时钟在下一讲介绍官方例程的时候,我们也会提到。

**Reference Clock Frequency:**参考时钟频率是通过专用收发器参考时钟引脚引入FPGA的时钟速率。参考时钟并不会影响我们的log\_clk,在下一讲我们也会对其他的时钟作详细解释。

**Buffer Configuration:**发送和接收缓冲区的深度可以自定义为8、16或32。此数字表示缓冲区能够存储的数据包数量。选择较小的缓冲器深度节省资源(主要是块RAM和LUT),而最大缓冲器深度产生最大吞吐量。

**Component Device ID:**组件设备ID确定基本设备ID CSR的重置值。可以类比理解为收发数据需要知道对方的ID号,自己的ID就是源ID,对方的ID就是目的ID。

**Device ID Width:** 核心的设备ID宽度应与链路伙伴的设备ID宽度匹配。否则,交易可能会因标头移位而被误解。大多数系统使用8位设备ID,但SRIO Gen2端点也通过此选项提供大型系统支持。

**Flow Control:**这些选项指示变送器使用的流量控制类型。

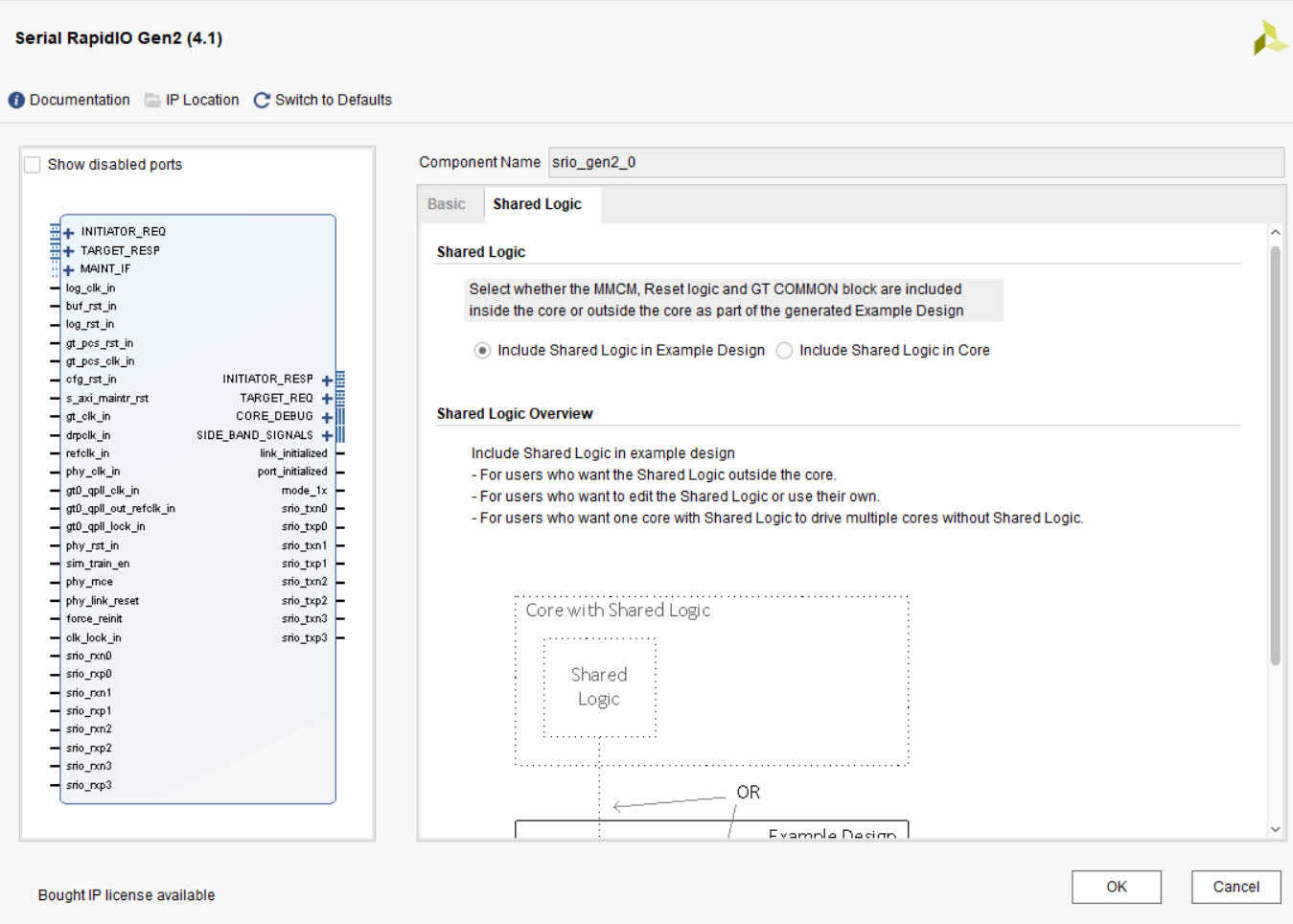

**Shared Logic:**我们直接包含在例程里面就可以了。

到这里之后我们的IP就算配置完成了,接下来就带大家一起学习一下怎么使用它进行数据的传输

2.收发测试

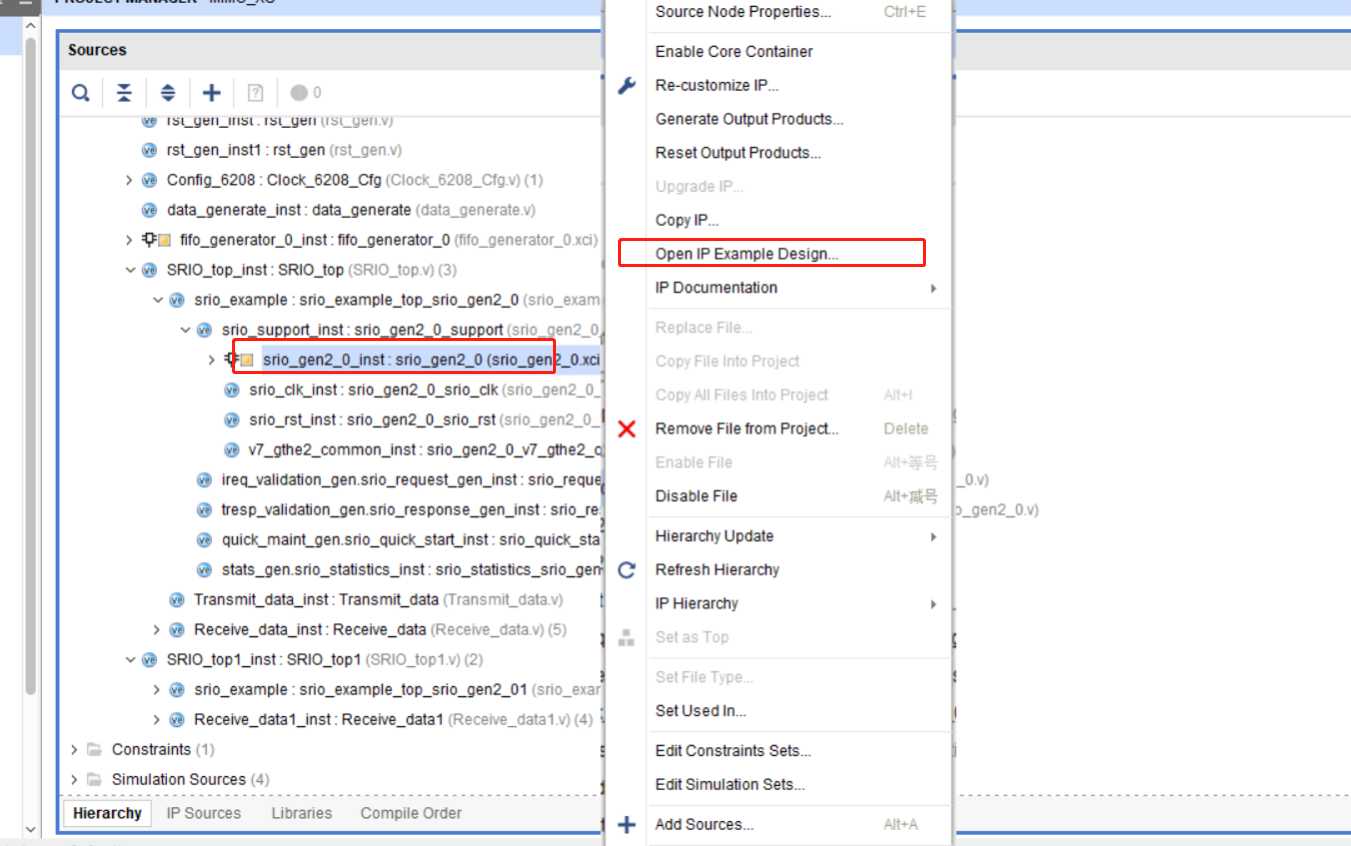

首先右键单击 SRIO IP,选择open IP Example Design

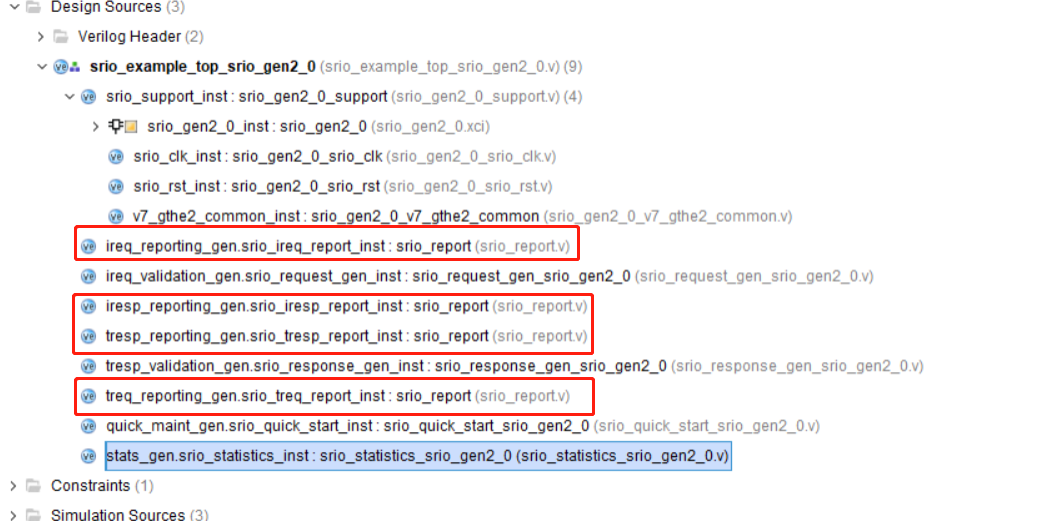

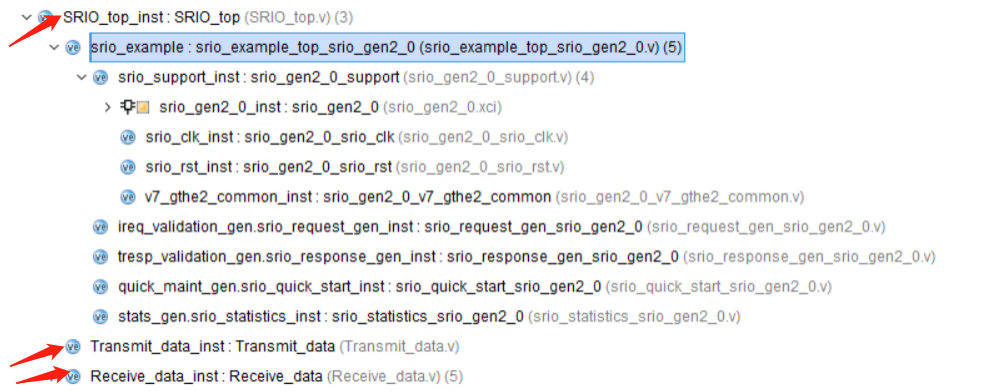

之后大家会看到有很多子文件,如下图所示:

用红色圈出来的有4个子文件,这几个文件可以直接删除,并且在Example\_top模块也删除,本节内容就用最简单的方法,教会大家怎么使用SRIO IP进行数据的收发,更为详细的解释,会在下一讲说明。

然后大家其实可以发现,这些子文件其实全都都在Example\_top模块下的。那我们要收发数据其实也很简单。首先自己定义一个发送和接收模块,其次,再定义一个顶层top模块,top模块作用就是把Example\_top、Transmit、Receive模块连接到一起。

如下图所示:

我们定义了发送模块、接收模块、顶层模块,并且把IP核的子文件和自定义的文件连接起来。接下来,给大家介绍一下对应端口的连接,首先就是srio\_example模块,也就是子文件的顶层,我们看一下它的端口信号:

`timescale 1ps/1ps

(* DowngradeIPIdentifiedWarnings = "yes" *)

module srio_example_top_srio_gen2_0 #(

parameter SIM_VERBOSE = 1, // If set, generates unsynthesizable reporting

parameter VALIDATION_FEATURES = 1, // If set, uses internal instruction sequences for hw and sim test

parameter QUICK_STARTUP = 1, // If set, quick-launch configuration access is contained here

parameter STATISTICS_GATHERING = 1, // If set, I/O can be rerouted to the maint port [0,1]

parameter C_LINK_WIDTH = 4

)

// port declarations ----------------

(

// Clocks and Resets

input sys_clkp, // MMCM reference clock

input sys_clkn, // MMCM reference clock

input sys_rst, // Global reset signal

// high-speed IO

input srio_rxn0, // Serial Receive Data

input srio_rxp0, // Serial Receive Data

input srio_rxn1, // Serial Receive Data

input srio_rxp1, // Serial Receive Data

input srio_rxn2, // Serial Receive Data

input srio_rxp2, // Serial Receive Data

input srio_rxn3, // Serial Receive Data

input srio_rxp3, // Serial Receive Data

output srio_txn0, // Serial Transmit Data

output srio_txp0, // Serial Transmit Data

output srio_txn1, // Serial Transmit Data

output srio_txp1, // Serial Transmit Data

output srio_txn2, // Serial Transmit Data

output srio_txp2, // Serial Transmit Data

output srio_txn3, // Serial Transmit Data

output srio_txp3, // Serial Transmit Data

input sim_train_en, // Set this only when simulating to reduce the size of counters

output [7:0] led0

);

**1.** Parameter定义的5个参数咱们是不用管的,在IP核配置完成之后,这里的参数就会定下来,其实这也就是官方例程的魅力所在,基本上都是参数化来写的程序。

**2.** 接下来,又定义了4个通道的接收,4通道的发送,当然这里是因为我的IP配置的是4通道,并且高速数据的传输大都采用差分信号线。

**3.** 然后就到了 input sim\_train\_en, output \[7:0\] led0;这两个信号在实际使用的时候用不到,我们直接在对应地方删除就好,或者就是wire一下,不要放到端口信号那里。

4.我们需要再加几个信号,就能完成端口的例化了,当然也非常简单,我们要自己收发数据,就需要自己产生发送、接收有效信号等。总共需要加14个端口信号,6个是发送数据相关的,6个是接收信号相关的,还有两个是链路初始化相关的,SRIO进行通信,首先就需要把链路建立起来以后,才能做一些数据的收发,如下所示:

`timescale 1ps/1ps

(* DowngradeIPIdentifiedWarnings = "yes" *)

module srio_example_top_srio_gen2_0 #(

parameter SIM_VERBOSE = 0, // If set, generates unsynthesizable reporting

parameter VALIDATION_FEATURES = 1, // If set, uses internal instruction sequences for hw and sim test

parameter QUICK_STARTUP = 1, // If set, quick-launch configuration access is contained here

parameter STATISTICS_GATHERING = 1, // If set, I/O can be rerouted to the maint port [0,1]

parameter C_LINK_WIDTH = 4

)

// port declarations ----------------

(

// Clocks and Resets

input sys_clkp, // MMCM reference clock

input sys_clkn, // MMCM reference clock

input sys_rst, // Global reset signal

output log_clk,

// high-speed IO

input srio_rxn0, // Serial Receive Data

input srio_rxp0, // Serial Receive Data

input srio_rxn1, // Serial Receive Data

input srio_rxp1, // Serial Receive Data

input srio_rxn2, // Serial Receive Data

input srio_rxp2, // Serial Receive Data

input srio_rxn3, // Serial Receive Data

input srio_rxp3, // Serial Receive Data

output srio_txn0, // Serial Transmit Data

output srio_txp0, // Serial Transmit Data

output srio_txn1, // Serial Transmit Data

output srio_txp1, // Serial Transmit Data

output srio_txn2, // Serial Transmit Data

output srio_txp2, // Serial Transmit Data

output srio_txn3, // Serial Transmit Data

output srio_txp3, // Serial Transmit Data

/*********************************************/

input val_ireq_tvalid,

output val_ireq_tready,

input val_ireq_tlast ,

input [63:0] val_ireq_tdata , //待发送给DSP的数据

input [7:0] val_ireq_tkeep ,

input [31:0] val_ireq_tuser ,

output val_treq_tvalid,

input val_treq_tready,

output val_treq_tlast,

output [63:0] val_treq_tdata, //从DSP接收来的数据

output [7:0] val_treq_tkeep,

output [31:0] val_treq_tuser,

output port_initialized,

output link_initialized

/*********************************************/

);

可以看到,以上程序也给了一些注释,本程序是为了FPGA与DSP进行数据交互的而设计的,如果两块FPGA之间进行数据的传输同样可以采用SRIO。

对于FPGA给DSP发送的数据来讲,那信号名称就是ireq,总共6个信号,是从 srio\_request\_gen\_srio\_gen2\_0模块引出来的,简单来说就是把srio\_request\_gen\_srio\_gen2\_0模块的这6个信号,连接到咱们自己产生的发送模块里面。当然这6个信号是符合AXI协议的,简而言之,就是vld和rdy信号握手,此时数据有效。

类似的,对于FPGA来说,DSP给FPGA发送的数据就是treq,总共6个信号,连接到咱们自己产生的接收模块里面。同样也符合AXI协议,这6个信号是从 srio\_response\_gen\_srio\_gen2\_0模块引出来的。其实大家应该也发现了,request就是请求,对应数据发送,response是应答,对应数据接收。

最后,对于port\_initialized表示端口已初始化。此信号反映物理层配置中端口n错误和状态CSR中端口未初始化位的值。而link\_initialized表示链接已初始化。具体地,已经发送了至少15个状态控制符号,并且已经接收了8个无差错的状态控制符号。这两个信号是从support模块引出来的,实际上我们使用的时候,会把这两个信号相与,作为初始化成功的信号。

以上就是对Example\_top模块的端口说明,接下来给出顶层的例化部分程序,发送和接收部分是根据自己的逻辑,用状态机实现的,程序比较长,就不在这里给出了。顶层的例化部分程序如下:

//********************************************SRIO*******************************************

(*mark_debug = "true"*)wire ireq_tvalid;

(*mark_debug = "true"*)wire ireq_tready;

(*mark_debug = "true"*)wire ireq_tlast;

(*mark_debug = "true"*)wire [63:0] ireq_tdata;

(*mark_debug = "true"*)wire [7:0] ireq_tkeep;

(*mark_debug = "true"*)wire [31:0] ireq_tuser;

(*mark_debug = "true"*)wire treq_tvalid;

(*mark_debug = "true"*)wire treq_tready;

(*mark_debug = "true"*)wire treq_tlast;

(*mark_debug = "true"*)wire [63:0] treq_tdata;

(*mark_debug = "true"*)wire [7:0] treq_tkeep;

(*mark_debug = "true"*)wire [31:0] treq_tuser;

wire port_initialized;

wire link_initialized;

srio_example_top_srio_gen2_0 #(

.SIM_VERBOSE (0), // If set, generates unsynthesizable reporting

.VALIDATION_FEATURES (1), // If set, uses internal instruction sequences for hw and sim test

.QUICK_STARTUP (1), // If set, quick-launch configuration access is contained here

.STATISTICS_GATHERING (1), // If set, I/O can be rerouted to the maint port [0,1]

.C_LINK_WIDTH (4)

)

srio_example(

//Clocks and Resets

.sys_clkp (srio_clkp ),

.sys_clkn (srio_clkn ),

.sys_rst (rst ),

.log_clk (log_clk_out ),

//high-speed IO

.srio_rxn0 (srio_rxn0 ),

.srio_rxp0 (srio_rxp0 ),

.srio_rxn1 (srio_rxn1 ),

.srio_rxp1 (srio_rxp1 ),

.srio_rxn2 (srio_rxn2 ),

.srio_rxp2 (srio_rxp2 ),

.srio_rxn3 (srio_rxn3 ),

.srio_rxp3 (srio_rxp3 ),

.srio_txn0 (srio_txn0 ),

.srio_txp0 (srio_txp0 ),

.srio_txn1 (srio_txn1 ),

.srio_txp1 (srio_txp1 ),

.srio_txn2 (srio_txn2 ),

.srio_txp2 (srio_txp2 ),

.srio_txn3 (srio_txn3 ),

.srio_txp3 (srio_txp3 ),

//User_interface

.val_ireq_tvalid (ireq_tvalid ),

.val_ireq_tready (ireq_tready ),

.val_ireq_tlast (ireq_tlast ),

.val_ireq_tdata (ireq_tdata ), //ĺé?çťDSPçć°ć?

.val_ireq_tkeep (ireq_tkeep ),

.val_ireq_tuser (ireq_tuser ),

.val_treq_tvalid (treq_tvalid ),

.val_treq_tready (treq_tready ),

.val_treq_tlast (treq_tlast ),

.val_treq_tdata (treq_tdata ), //äťDSPćĽćśćĽçć°ćŽ

.val_treq_tkeep (treq_tkeep ),

.val_treq_tuser (treq_tuser ),

.port_initialized (port_initialized ),

.link_initialized (link_initialized )

);

//******************************************SRIOĺć°*****************************************

wire SRIO_initialized;

assign SRIO_initialized = port_initialized & link_initialized;

Transmit_data Transmit_data_inst(

.log_clk (log_clk_out ),

.rst (rst ),

.trans_begin (1'b1 ),

.SRIO_initialized (SRIO_initialized ),

.time_delay_error_3r (time_delay_error_3r ),

.phase_delay_error_3r (phase_delay_error_3r ),

.velocity_error_3r (velocity_error_3r ),

.angle_error_3r (angle_error_3r ),

.yuanCPI_num_3r (yuanCPI_num_3r ),

.zhongCPI_num_3r (zhongCPI_num_3r ),

.jinCPI_num_3r (jinCPI_num_3r ),

.yuanCPI_PRT_num_3r (yuanCPI_PRT_num_3r ),

.zhongCPI_PRT_num_3r (zhongCPI_PRT_num_3r ),

.jinCPI_PRT_num_3r (jinCPI_PRT_num_3r ),

.yuan_event_num_before_fifo_rst (yuan_event_num_before_fifo_rst),

.yuan_event_num_all_cpi (yuan_event_num_all_cpi),

.zhong_event_num_before_fifo_rst (zhong_event_num_before_fifo_rst),

.zhong_event_num_all_cpi (zhong_event_num_all_cpi),

.jin_event_num_before_fifo_rst (jin_event_num_before_fifo_rst),

.jin_event_num_all_cpi (jin_event_num_all_cpi),

.ref_unit_num_3r (ref_unit_num_3r ),

.protect_unit_num_3r (protect_unit_num_3r ),

.detect_factor_3r (detect_factor_3r ),

.distance_win_num_3r (distance_win_num_3r ),

.doppler_win_num_3r (doppler_win_num_3r ),

.master_sla_dyt_3r (master_sla_dyt_3r ),

//ä¸ĺ¤é¨FIFOćĽĺŁ

.pakage_data_in (pakage_data_in ),

.package_fifo_pfull (package_fifo_pfull ),

.rd_package_fifo (rd_package_fifo ),

.event_num_before_db (event_num_before_db ),

.ireq_tvalid (ireq_tvalid ),

.ireq_tready (ireq_tready ),

.ireq_tlast (ireq_tlast ),

.ireq_tdata (ireq_tdata ),

.ireq_tkeep (ireq_tkeep ),

.ireq_tuser (ireq_tuser )

);

//******************************************SRIOćść°*****************************************

Receive_data Receive_data_inst(

.log_clk (log_clk_out ),

.read_clk (log_clk_out ),

.rst (rst ),

// .restart (restart_2r ),

.treq_tvalid (treq_tvalid ),

.treq_tready (treq_tready ),

.treq_tlast (treq_tlast ),

.treq_tdata (treq_tdata ),

.treq_tkeep (treq_tkeep ),

.treq_tuser (treq_tuser ),

.srio_rxdata_out (srio_rxdata_out ),

.jiaodu_data (jiaodu_data ),

.jiaodu_vld (jiaodu_vld ),

.srio_rxdata_valid (srio_rxdata_valid )

);

这样一来,我们就把自己的顶层,发送模块,接收模块,以及Example\_top模块连接到一起了,然后根据自己需要传输的数据来编写发送和接收模块的代码即可,当然,如果还是有一些问题也欢迎讨论,大家一起交流学习。

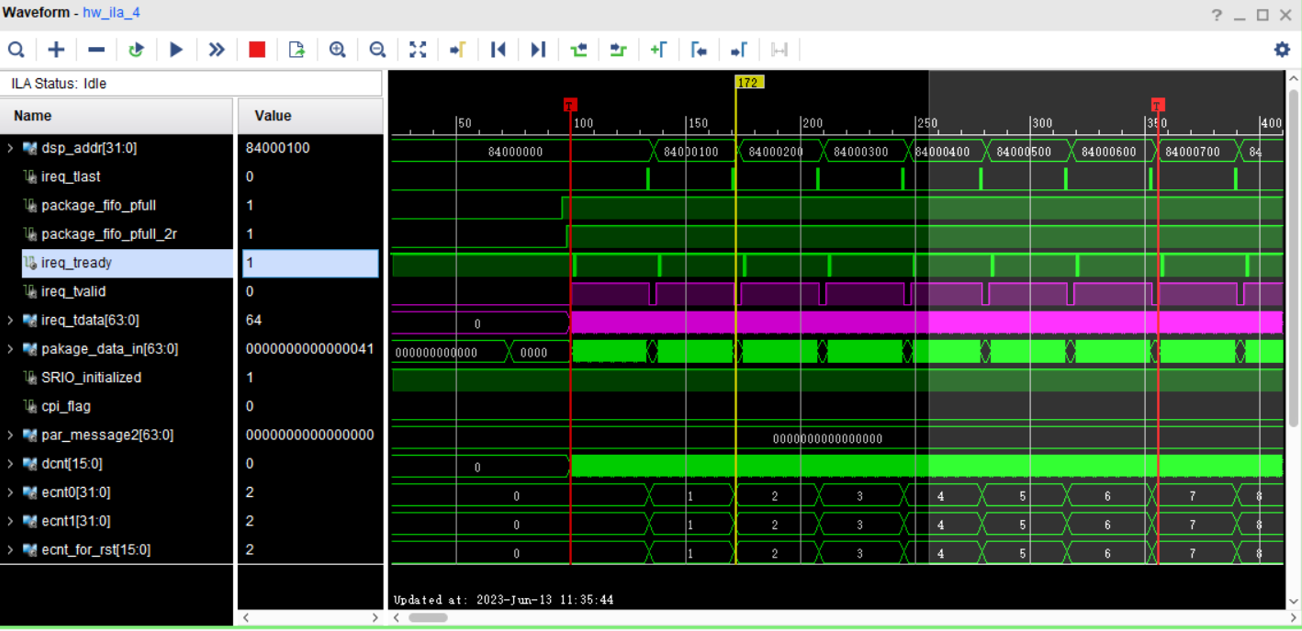

**上板验证:**SRIO IP配置的是4x,3.125Gbps,通过之前的介绍,我们知道log\_clk\_out的时钟周期是6.4ns,在这里也可以和大家分享一个小技巧,如果大家不确定自己算的时钟频率是否正确,那可以直接打开官方的例程,直接Run simulation即可,只是需要等待时间长一点,这样就能看到当前配置下的时钟频率具体是多少了。

本次程序采用的是递增数来进行测试,从一块FPGA的光口,发到另外一块FPGA的光口,一包数据是256字节,正好是一包最大的数据传输量,对应32个64bit。总共发了500包,由于ila深度不够,我这里只给出开头部分的截图,下面给出测试结果:

SRIO数据发送

SRIO数据接收

这两年,IT行业面临经济周期波动与AI产业结构调整的双重压力,确实有很多运维与网络工程师因企业缩编或技术迭代而暂时失业。

很多人都在提运维网工失业后就只能去跑滴滴送外卖了,但我想分享的是,对于运维人员来说,即便失业以后仍然有很多副业可以尝试。

网工/运维/测试副业方向

运维网工,千万不要再错过这些副业机会!

第一个是知识付费类副业:输出经验打造个人IP

在线教育平台讲师

操作路径:在慕课网、极客时间等平台开设《CCNA实战》《Linux运维从入门到精通》等课程,或与培训机构合作录制专题课。

收益模式:课程销售分成、企业内训。

技术博客与公众号运营

操作路径:撰写网络协议解析、故障排查案例、设备评测等深度文章,通过公众号广告、付费专栏及企业合作变现。

收益关键:每周更新2-3篇原创,结合SEO优化与社群运营。

第二个是技术类副业:深耕专业领域变现

企业网络设备配置与优化服务

操作路径:为中小型企业提供路由器、交换机、防火墙等设备的配置调试、性能优化及故障排查服务。可通过本地IT服务公司合作或自建线上接单平台获客。

收益模式:按项目收费或签订年度维护合同。

远程IT基础设施代维

操作路径:通过承接服务器监控、日志分析、备份恢复等远程代维任务。适合熟悉Zabbix、ELK等技术栈的工程师。

收益模式:按工时计费或包月服务。

网络安全顾问与渗透测试

操作路径:利用OWASP Top 10漏洞分析、Nmap/BurpSuite等工具,为企业提供漏洞扫描、渗透测试及安全加固方案。需考取CISP等认证提升资质。

收益模式:单次渗透测试报告收费;长期安全顾问年费。

比如不久前跟我一起聊天的一个粉丝,他自己之前是大四实习的时候做的运维,发现运维7*24小时待命受不了,就准备转网安,学了差不多2个月,然后开始挖漏洞,光是补天的漏洞奖励也有个四五千,他说自己每个月的房租和饭钱就够了。

为什么我会推荐你网安是运维和网工测试人员的绝佳副业&转型方向?

1.你的经验是巨大优势: 你比任何人都懂系统、网络和架构。漏洞挖掘、内网渗透、应急响应,这些核心安全能力本质上是“攻击视角下的运维”。你的运维背景不是从零开始,而是降维打击。

2.越老越吃香,规避年龄危机: 安全行业极度依赖经验。你的排查思路、风险意识和对复杂系统的理解能力,会随着项目积累而愈发珍贵,真正做到“姜还是老的辣”。

3.职业选择极其灵活: 你可以加入企业成为安全专家,可以兼职“挖洞“获取丰厚奖金,甚至可以成为自由顾问。这种多样性为你提供了前所未有的抗风险能力。

4.市场需求爆发,前景广阔: 在国家级政策的推动下,从一线城市到二三线地区,安全人才缺口正在急剧扩大。现在布局,正是抢占未来先机的黄金时刻。

网工运维测试转行学习网络安全路线

(一)第一阶段:网络安全筑基

1. 阶段目标

你已经有运维经验了,所以操作系统、网络协议这些你不是零基础。但要学安全,得重新过一遍——只不过这次我们是带着“安全视角”去学。

2. 学习内容

**操作系统强化:**你需要重点学习 Windows、Linux 操作系统安全配置,对比运维工作中常规配置与安全配置的差异,深化系统安全认知(比如说日志审计配置,为应急响应日志分析打基础)。

**网络协议深化:**结合过往网络协议应用经验,聚焦 TCP/IP 协议簇中的安全漏洞及防护机制,如 ARP 欺骗、TCP 三次握手漏洞等(为 SRC 漏扫中协议层漏洞识别铺垫)。

**Web 与数据库基础:**补充 Web 架构、HTTP 协议及 MySQL、SQL Server 等数据库安全相关知识,了解 Web 应用与数据库在网安中的作用。

**编程语言入门:**学习 Python 基础语法,掌握简单脚本编写,为后续 SRC 漏扫自动化脚本开发及应急响应工具使用打基础。

**工具实战:**集中训练抓包工具(Wireshark)、渗透测试工具(Nmap)、漏洞扫描工具(Nessus 基础版)的使用,结合模拟场景练习工具应用(掌握基础扫描逻辑,为 SRC 漏扫工具进阶做准备)。

(二)第二阶段:漏洞挖掘与 SRC 漏扫实战

1. 阶段目标

这阶段是真正开始“动手”了。信息收集、漏洞分析、工具联动,一样不能少。

熟练运用漏洞挖掘及 SRC 漏扫工具,具备独立挖掘常见漏洞及 SRC 平台漏扫实战能力,尝试通过 SRC 挖洞搞钱,不管是低危漏洞还是高危漏洞,先挖到一个。

2. 学习内容

信息收集实战:结合运维中对网络拓扑、设备信息的了解,强化基本信息收集、网络空间搜索引擎(Shodan、ZoomEye)、域名及端口信息收集技巧,针对企业级网络场景开展信息收集练习(为 SRC 漏扫目标筛选提供支撑)。

漏洞原理与分析:深入学习 SQL 注入、CSRF、文件上传等常见漏洞的原理、危害及利用方法,结合运维工作中遇到的类似问题进行关联分析(明确 SRC 漏扫重点漏洞类型)。

工具进阶与 SRC 漏扫应用:

-

系统学习 SQLMap、BurpSuite、AWVS 等工具的高级功能,开展工具联用实战训练;

-

专项学习 SRC 漏扫流程:包括 SRC 平台规则解读(如漏洞提交规范、奖励机制)、漏扫目标范围界定、漏扫策略制定(全量扫描 vs 定向扫描)、漏扫结果验证与复现;

-

实战训练:使用 AWVS+BurpSuite 组合开展 SRC 平台目标漏扫,练习 “扫描 - 验证 - 漏洞报告撰写 - 平台提交” 全流程。

SRC 实战演练:选择合适的 SRC 平台(如补天、CNVD)进行漏洞挖掘与漏扫实战,积累实战经验,尝试获取挖洞收益。

恭喜你,如果学到这里,你基本可以下班搞搞副业创收了,并且具备渗透测试工程师必备的「渗透技巧」、「溯源能力」,让你在黑客盛行的年代别背锅,工作实现升职加薪的同时也能开创副业创收!

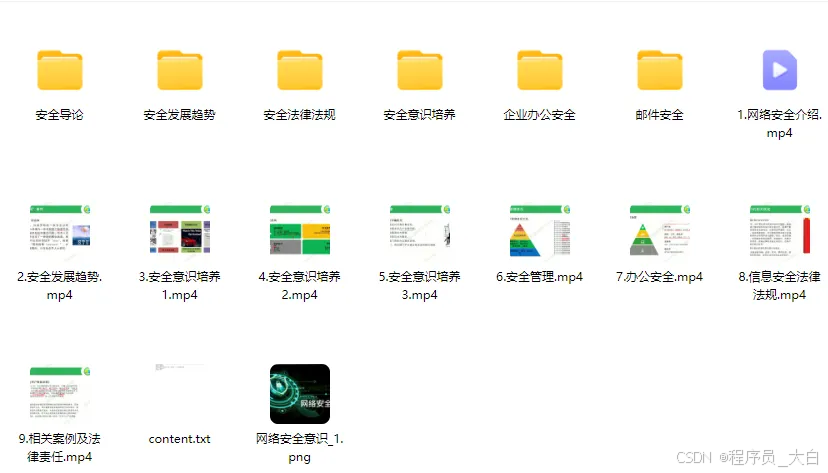

如果你想要入坑黑客&网络安全,笔者给大家准备了一份:全网最全的网络安全资料包需要保存下方图片,微信扫码即可前往获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

优快云大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

(三)第三阶段:渗透测试技能学习

1. 阶段目标

全面掌握渗透测试理论与实战技能,能够独立完成渗透测试项目,编写规范的渗透测试报告,具备渗透测试工程师岗位能力,为护网红蓝对抗及应急响应提供技术支撑。

2. 学习内容

渗透测试核心理论:系统学习渗透测试流程、方法论及法律法规知识,明确渗透测试边界与规范(与红蓝对抗攻击边界要求一致)。

实战技能训练:开展漏洞扫描、漏洞利用、电商系统渗透测试、内网渗透、权限提升(Windows、Linux)、代码审计等实战训练,结合运维中熟悉的系统环境设计测试场景(强化红蓝对抗攻击端技术能力)。

工具开发实践:基于 Python 编程基础,学习渗透测试工具开发技巧,开发简单的自动化测试脚本(可拓展用于 SRC 漏扫自动化及应急响应辅助工具)。

报告编写指导:学习渗透测试报告的结构与编写规范,完成多个不同场景的渗透测试报告撰写练习(与 SRC 漏洞报告、应急响应报告撰写逻辑互通)。

(四)第四阶段:企业级安全攻防(含红蓝对抗)、应急响应

1. 阶段目标

掌握企业级安全攻防、护网红蓝对抗及应急响应核心技能,考取网安行业相关证书。

2. 学习内容

护网红蓝对抗专项:

-

红蓝对抗基础:学习护网行动背景、红蓝对抗规则(攻击范围、禁止行为)、红蓝双方角色职责(红队:模拟攻击;蓝队:防御检测与应急处置);

-

红队实战技能:强化内网渗透、横向移动、权限维持、免杀攻击等高级技巧,模拟护网中常见攻击场景;

-

蓝队实战技能:学习安全设备(防火墙、IDS/IPS、WAF)联动防御配置、安全监控平台(SOC)使用、攻击行为研判与溯源方法;

-

模拟护网演练:参与团队式红蓝对抗演练,完整体验 “攻击 - 检测 - 防御 - 处置” 全流程。

应急响应专项: -

应急响应流程:学习应急响应 6 步流程(准备 - 检测 - 遏制 - 根除 - 恢复 - 总结),掌握各环节核心任务;

-

实战技能:开展操作系统入侵响应(如病毒木马清除、异常进程终止)、数据泄露应急处置、漏洞应急修补等实战训练;

-

工具应用:学习应急响应工具(如 Autoruns、Process Monitor、病毒分析工具)的使用,提升处置效率;

-

案例复盘:分析真实网络安全事件应急响应案例(如勒索病毒事件),总结处置经验。

其他企业级攻防技能:学习社工与钓鱼、CTF 夺旗赛解析等内容,结合运维中企业安全防护需求深化理解。

证书备考:针对网安行业相关证书考试内容(含红蓝对抗、应急响应考点)进行专项复习,参加模拟考试,查漏补缺。

运维网工测试转行网络攻防知识库分享

网络安全这行,不是会几个工具就能搞定的。你得有体系,懂原理,能实战。尤其是从运维转过来的,别浪费你原来的经验——你比纯新人强多了。

但也要沉得住气,别学了两天Web安全就觉得自己是黑客了。内网、域渗透、代码审计、应急响应,要学的还多着呢。

如果你真的想转,按这个路子一步步走,没问题。如果你只是好奇,我劝你再想想——这行要持续学习,挺累的,但也是真有意思。

关于如何学习网络安全,笔者也给大家整理好了全套网络安全知识库,需要的可以扫码获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

优快云大礼包:《黑客&网络安全入门&进阶学习资源包》免费分享

1、网络安全意识

2、Linux操作系统

3、WEB架构基础与HTTP协议

4、Web渗透测试

5、渗透测试案例分享

6、渗透测试实战技巧

7、攻防对战实战

8、CTF之MISC实战讲解

关于如何学习网络安全,笔者也给大家整理好了全套网络安全知识库,需要的可以扫码获取!

因篇幅有限,仅展示部分资料,需要点击下方链接即可前往获取

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?