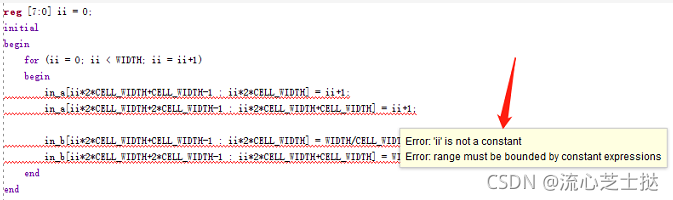

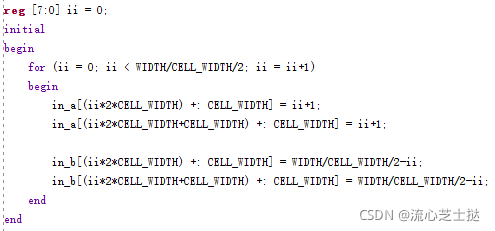

ii是变量,取部分位时,冒号前后不能都出现变量,否则会报错 range must be bounded by constant expresssions

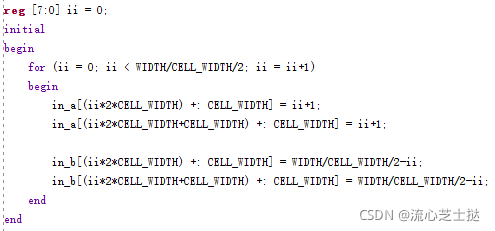

上述代码应改成

即,不能写成 [n+7:n],应写成 [n +: 8],表示从第n位开始,往上取8位。

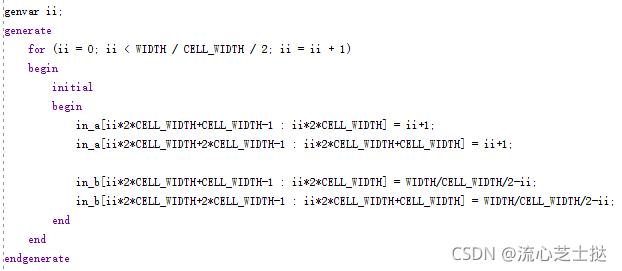

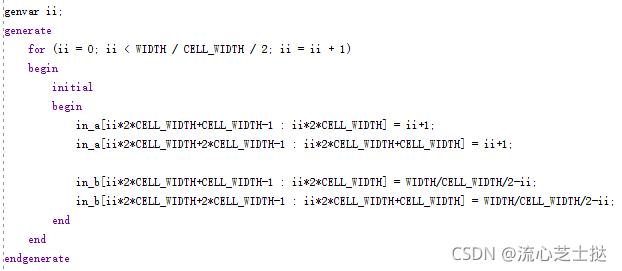

如果是在generate-for中取位,可以使用由genvar声明的循环变量进行取位,冒号前后都有循环变量也可以。

本文详细解析了Verilog语言中对于变量取位的正确用法。指出当使用变量进行位选取时,选取范围必须由常量表达式界定,并给出了正确的示例。同时介绍了在generate-for循环中如何合法地利用循环变量进行位操作。

本文详细解析了Verilog语言中对于变量取位的正确用法。指出当使用变量进行位选取时,选取范围必须由常量表达式界定,并给出了正确的示例。同时介绍了在generate-for循环中如何合法地利用循环变量进行位操作。

ii是变量,取部分位时,冒号前后不能都出现变量,否则会报错 range must be bounded by constant expresssions

上述代码应改成

即,不能写成 [n+7:n],应写成 [n +: 8],表示从第n位开始,往上取8位。

如果是在generate-for中取位,可以使用由genvar声明的循环变量进行取位,冒号前后都有循环变量也可以。

3万+

3万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?