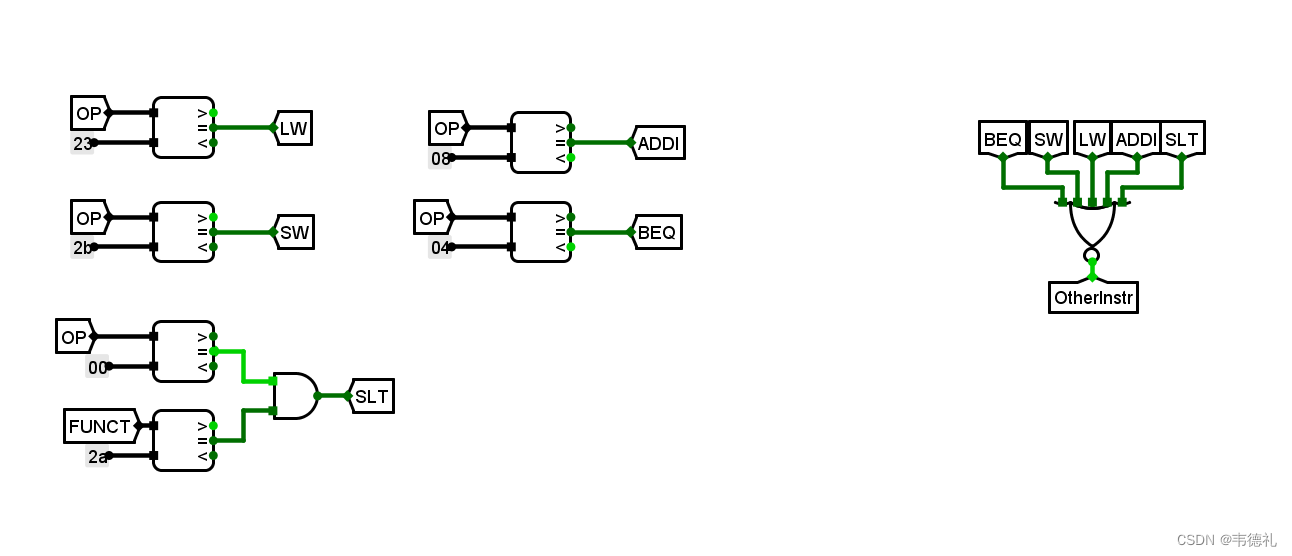

第1关 MIPS指令译码器设计

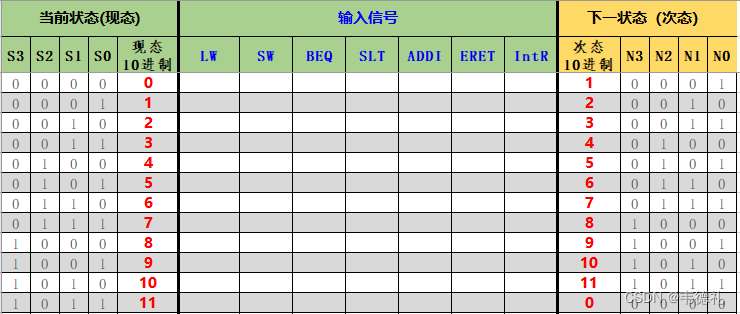

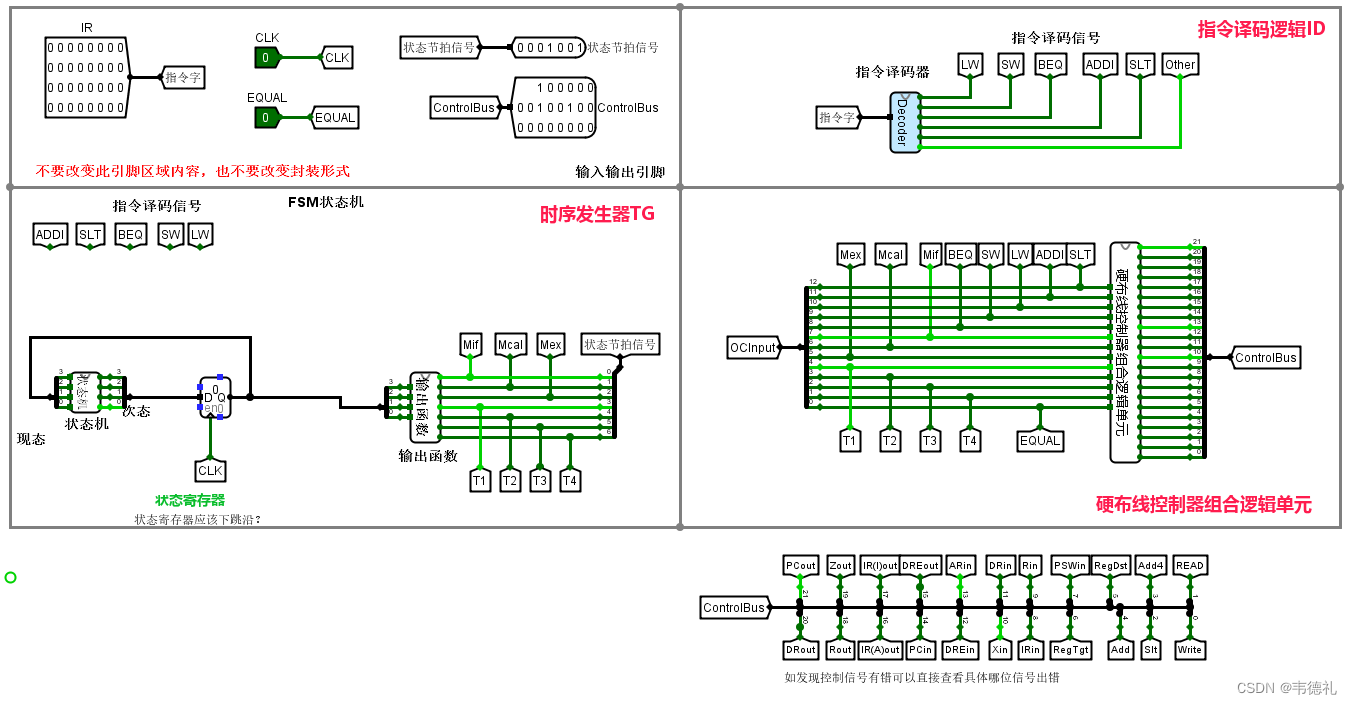

第2关 定长指令周期---时序发生器FSM设计

按状态图填写相应的excel表,自动生成次态逻辑表达式后,即可在logisim中自动生成该电路。

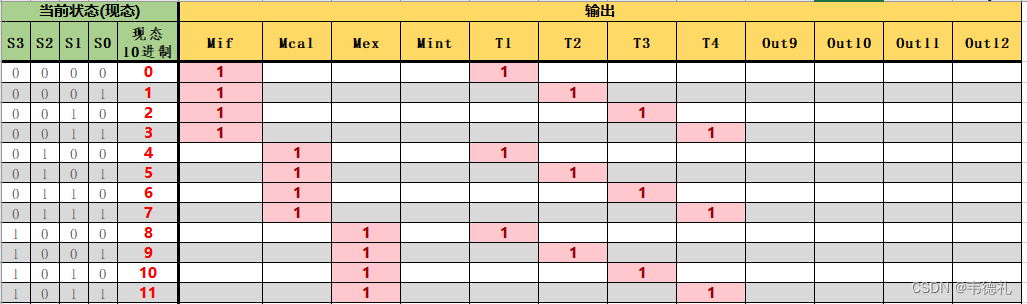

第3关 定长指令周期---时序发生器输出函数设计

根据时序输出要求,填写excel表,自动生成各输出信号的逻辑表达式,在logisim中自动生成电路即可。

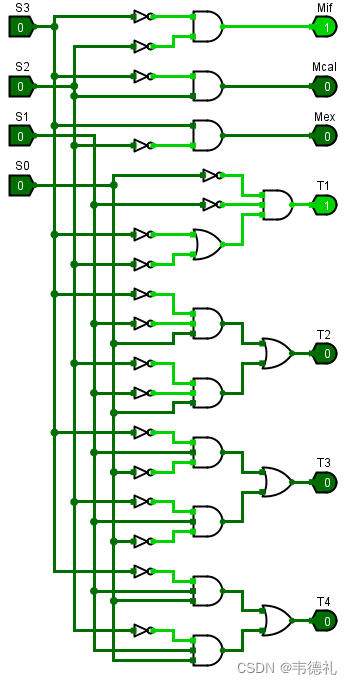

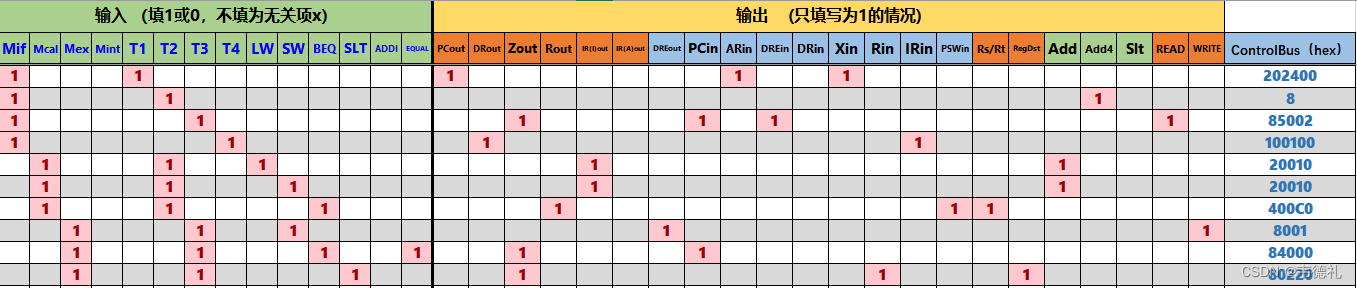

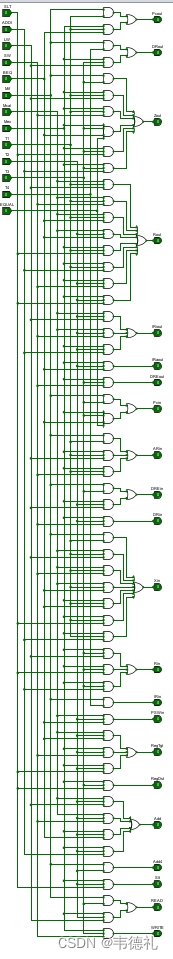

第4关 硬布线控制器组合逻辑单元

可以列出所有微操作信号的产生条件,填写下面的excel表格,自动生成逻辑表达式,然后再Logisim中自动生成电路。

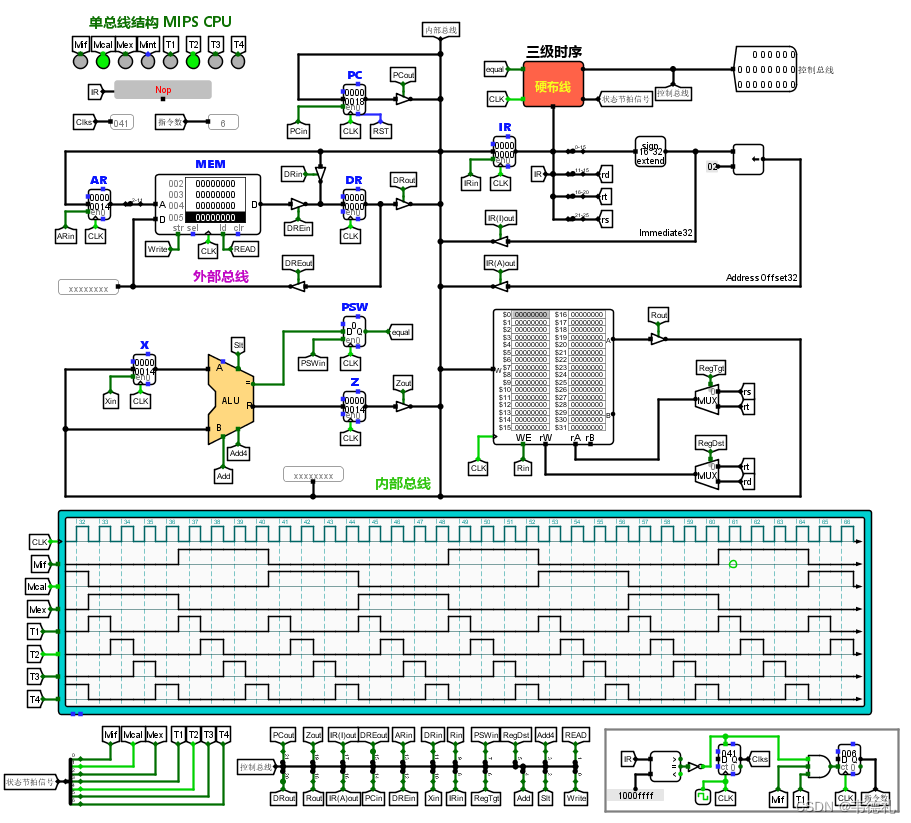

第5关 定长指令周期---硬布线控制器设计

第6关 定长指令周期---单总线CPU设计

头歌测试&CIRC文件

下载链接:单总线CPU设计(定长指令周期3级时序)(HUST)1~6关满分通关

下载链接:单总线CPU设计(定长指令周期3级时序)(HUST)1~6关满分通关

欢迎大家留言评论~

学习交流q2267261634

3547

3547