数字 IC 笔试面试必考点(5)同步复位以及异步复位

版权所有,新芯设计,转载文章,请注来源

引言

本文主要是提供了 ASIC 设计中关于复位技术相关的概念和设计。

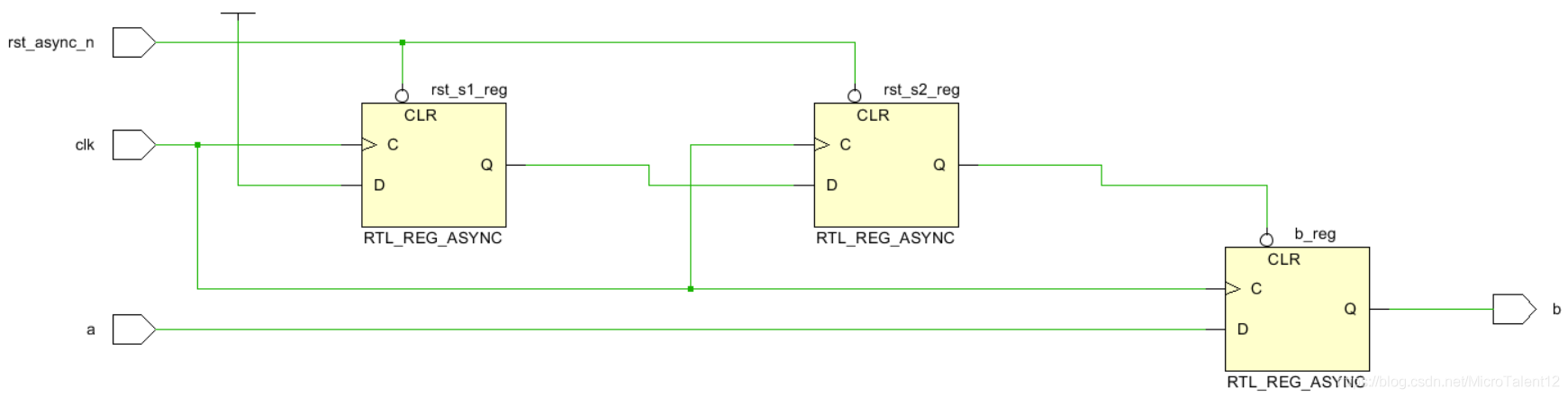

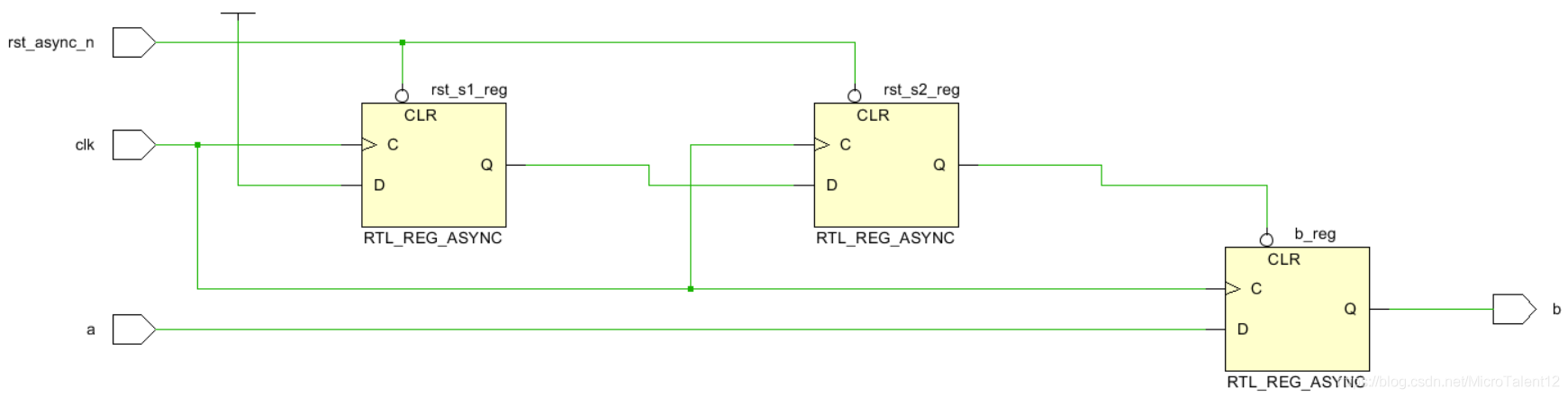

🌏 一、同步复位 Sync

当时钟上升沿检测到复位信号时,执行复位操作(有效的时钟沿是前提)。

always @( posedge clk )begin

if(!rst_n)

b <= 0;

else

b <= a;

end

✅

版权所有,新芯设计,转载文章,请注来源

本文主要是提供了 ASIC 设计中关于复位技术相关的概念和设计。

当时钟上升沿检测到复位信号时,执行复位操作(有效的时钟沿是前提)。

always @( posedge clk )begin

if(!rst_n)

b <= 0;

else

b <= a;

end

✅

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?