门电路是数字电路中最基本的逻辑单元。它可以使输出信号与输入信号之间产生一定的逻辑关系。在数字电路中,信号大都是用电位(电平)高低两种状态表示,利用门电路的逻辑关系可以实现对信号的转换。

最基本的门电路有与门电路,或门电路,非门电路等。

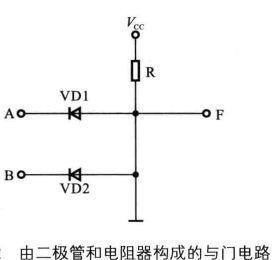

一、与门电路

概念:与门电路是指只有在一件事情的所有条件都具备时,事情才会发生。

由二极管和电阻器构成的与门电路见下图

图中A,B为两个输入变量,F为输出变量,当A,B均为高电平,F为高电平,A,B只要有一个为低电平,F就为低电平。

与门电路的真值表见下图。

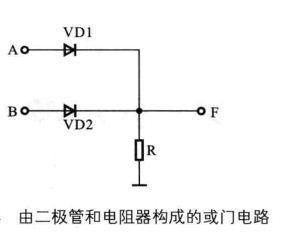

二、或门电路

或门电路是指只要有一个或一个以上条件满足时,事情就会发生。

同与门电路一样,最简单的或门电路也是由二极管和电阻器构成的。见下图

图中A,B为两个输入变量,F为输出变量。当A,B均为低电平,F才为低电平,A,B只要有一个为高电平,或两个都为高电平,F为高电平。

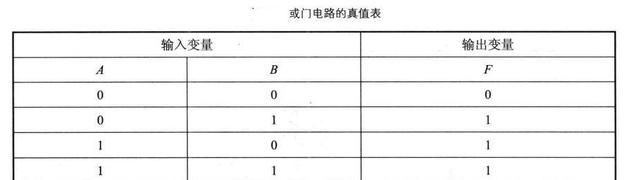

或门电路真值表见下图

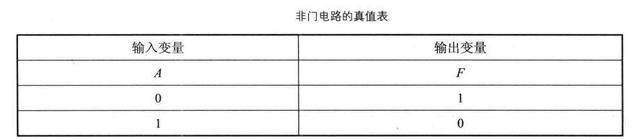

三、非门电路

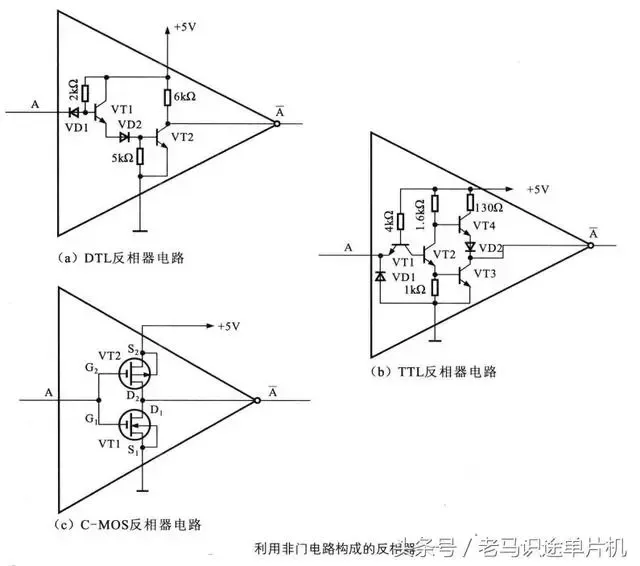

非门电路又叫“否”运算,也称求“反”运算,因此非门电路又称为反相器。

最基本的非门电路是利用晶体三极管的开关特性构成的。可以实现非逻辑关系。

由晶体三极管和外围元件组成的非门电路如下。

上图中,A为输入变量,Y为输出变量,利用晶体三极管的反相放大特性,当A为低电平,三极管截止,输出端Y为高电平。当输入高电平,三极管处于饱和区,输出端Y为低电平。

非门电路的真值表见下图。

非门电路构成的反相器主要有三种,有DTL型,TTL型和C-MOS等。DTL是Diode Transistor Logic(二极管晶体逻辑)的简称;TTL是Transistor Transistor Logic(晶体管晶体管逻辑)的简称。这两种逻辑电路的区别是DTL电路采用二极管做为输入电路,TTL采用三极管作为输入电路,C-MOS是Complementary Metal OxidE Semiconductor的缩写,这种电路主要采用C-MOS场效应管组成的逻辑电路。

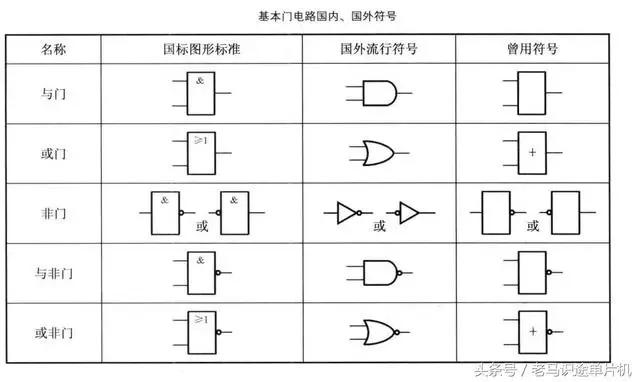

门电路符号中,国家标准与国外标准的区别见下图:

与非门和或非门分别是由与门+非门;或门+非门组合而成,在数字电路中也很常见。

四、门电路应用实例

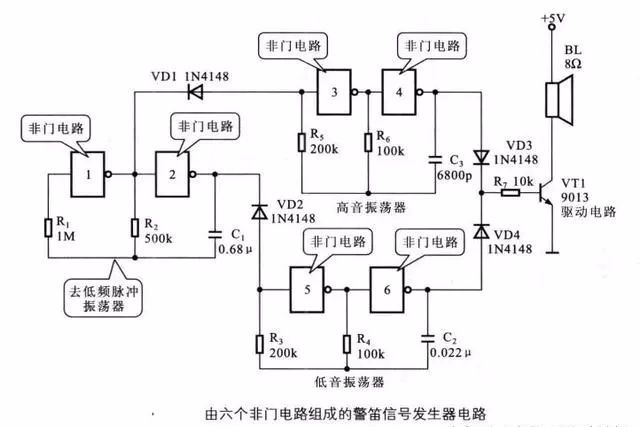

4.1 警笛信号发生器电路

警笛信号发生器电路一般用于报警电路中,通过高音和低音的交换发声,起到警示作用。

由六个非门电路组成的警笛信号发生器电路如下图:

非门1、2组成超低频脉冲振荡器,非门3、4组成高音振荡器,非门5、6组成低音振荡器。超低频脉冲振荡器的输出通过二极管VD1,VD2控制高、低音振荡器轮流发声,振荡信号分别经VD3,VD4由半导体三极管VT1放大后推动扬声器发声。

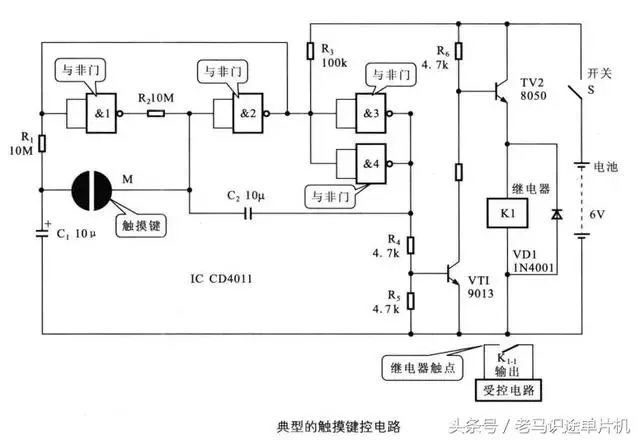

4.2 触摸键控电路

触摸键控电路是一种利用人手触摸金属触摸键,从而起到控制电路通断的作用。

见下图:

该电路主要由触摸金属板M,与非门电路1-4,继电器K,电池等部分构成。

触摸金属板用于输入指令,4个与非门电路用于将输入的指令识别和处理,继电器为指令输出控制端负载。

当手触摸金属板时,C1上的充电电荷将通过人体电阻加到与非门2的输入端,使其成为高电平,最后使与非门3、4输出高电平,VT1,VT2导通,继电器吸和,控制负载工作。

由于与非门1和与非门2之间通过电阻R2相连,所以由C1提供给与非门2输入端的高电平将保持下去,即使手离开金属板,电路仍会保持这一状态,直到金属板再次被触摸为止。

继电器吸合时,与非门1的输入端为低电平,C1通过R1及与非门1放电到0V左右。

当金属板再次受到触摸,C1上的0V电压经人体电阻加到与非门2的输入端,使电路又恢复到原来状态,即VT1,VT2截止,继电器断开。

本文介绍了门电路的基本原理,包括与门、或门、非门的工作方式及其真值表,并提供了警笛信号发生器和触摸键控电路的应用实例。

本文介绍了门电路的基本原理,包括与门、或门、非门的工作方式及其真值表,并提供了警笛信号发生器和触摸键控电路的应用实例。

9282

9282