🌸学习目标🌸

本章我们将从软件工程师的角度去了解计算机是如何工作的,通过对计算机核心工作机制的学习,有利于理解我们平时编程时的一些行为,动作的历史渊源。

在学习 CPU(中央处理器)之前,我们先来简单的了解一下💻计算机💻的发展历史。

让我们一起出发吧!!!😀😀😀

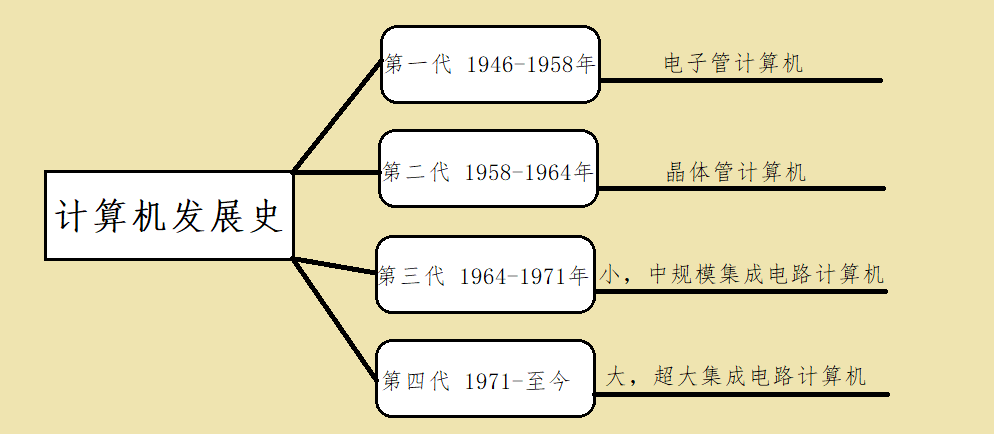

一. 计算机发展史

计算机(computer)俗称电脑,是现代一种用于高速计算的电子计算机器,可以进行数值计算,又可以进行逻辑计算,还具有存储记忆功能。是能够按照程序运行,自动、高速处理海量数据的现代化智能电子设备。计算机的发展大体经历了从一般计算工具到机械计算机到目前的电子计算机的发展历程。

冯诺依曼体系(Von Neumann Architecture)

约翰·冯·诺依曼(John von Neumann,1903年12月28日-1957年2月8日),美籍匈牙利数学家,计算机科学家,物理学家,是20世纪最重要的数学家之一。冯·诺依曼是罗兰大学数学博士,是现代计算机,博弈论,核武器和生化武器等领域内的科学全才之一,被后人称为“现代计算机之父”、“博弈论之父”。

现代的计算机, 大多遵守 冯诺依曼体系结构。

- CPU,即中央处理器,是一台计算机的运算核心和控制核心。其功能主要是解释计算机指令以及处理计算机软件中的数据。CPU由运算器、控制器、寄存器、高速缓存及实现它们之间联系的数据、控制及状态的总线构成

- 存储器,分为外存和内存, 用于存储数据(使用二进制方式存储)

- 输入设备,用户给计算机发号施令的设备

- 输出设备,计算机个用户汇报结果的设备

二. CPU 的基本工作过程

CPU = ALU ➕ CU

ALU 算术逻辑单元(Arithmetic&logical Unit):是中央处理器(CPU)的执行单元,是所有中央处理器的核心组成部分,由"And Gate"(与门) 和"Or Gate"(或门)构成的算术逻辑单元,主要功能是进行二位元的算术运算,如加减乘(不包括整数除法)。基本上,在所有现代CPU体系结构中,二进制都以补码的形式来表示。

CU 控制单元(Control Unit):负责程序的流程管理。控制单元是整个 CPU 的指挥控制中心,由指令寄存器IR(Instruction Register)、指令译码器ID(Instruction Decoder)和操作控制器OC(Operation Controller)三个部件组成,对协调整个电脑有序工作极为重要。

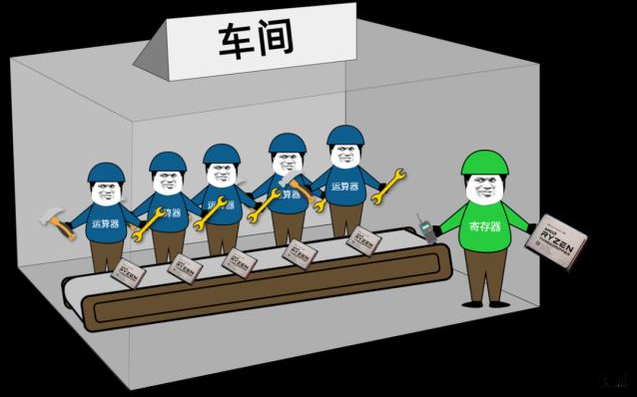

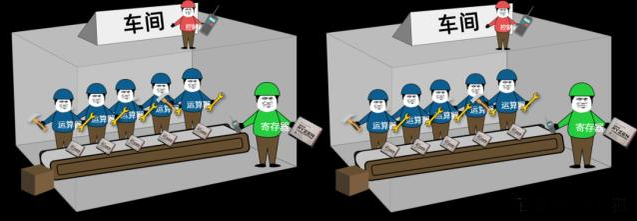

我们用一个例子来说明一下:假设 CPU 是一个工厂,一个核心就是工厂的一个车间

那么运算器 就是工厂里的普工,只负责生产(运算)

而 寄存器 呢,就是一个工具人,有时需要传递信息(数据),有时需要搬运物资(数据)。

控制器则是车间主管,管理调剂所有普工和工具人,压榨他们的劳动价值。

直到有一天,工厂发现一个车间(核心)效率不够,就只能增加车间(核心)来提高整个工厂效率。

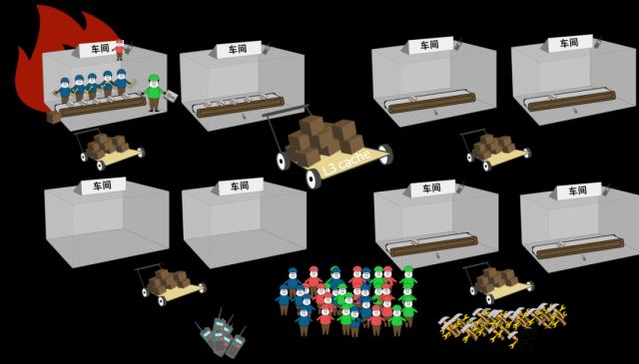

但是,渐渐的,又有新问题出现,工具人虽然效率高,但是数量不多,而随着越来越多的原材料(数据)涌入,工具人搬不过来。这时工厂就整了一个小板车(cache),专门用来运输、寄存工具人搬不过来的数据,而且各工厂可以共享其中一部分(intel 的 L3 cache)。

随着车间数量(核心数目)增加到八,工厂发现有些时候出货量挺高的(全车间都开工),但有些时候只有一两个个车间开工,其它车间都在围观(调度问题)。

而且整个工厂一起开工,用电量和发热量也急剧上升,但是各车间的效率(频率)就是上不去,此外,还要担心电力供给、散热、物资(数据)运输等各类问题。

终于,在投入了大研发后,工厂的厂房布局设计(架构)有了大改进。

各部门之间的交通更便利了;并且,工厂也重新招聘短小精悍的工人(提升制程工艺),将以前那种牛高马大,光吃不干的大块头全部淘汰了。至此,同样大的车间,能融入更多的工人干活了,而且短小精悍的工人,吃的饭还少(功耗低)。

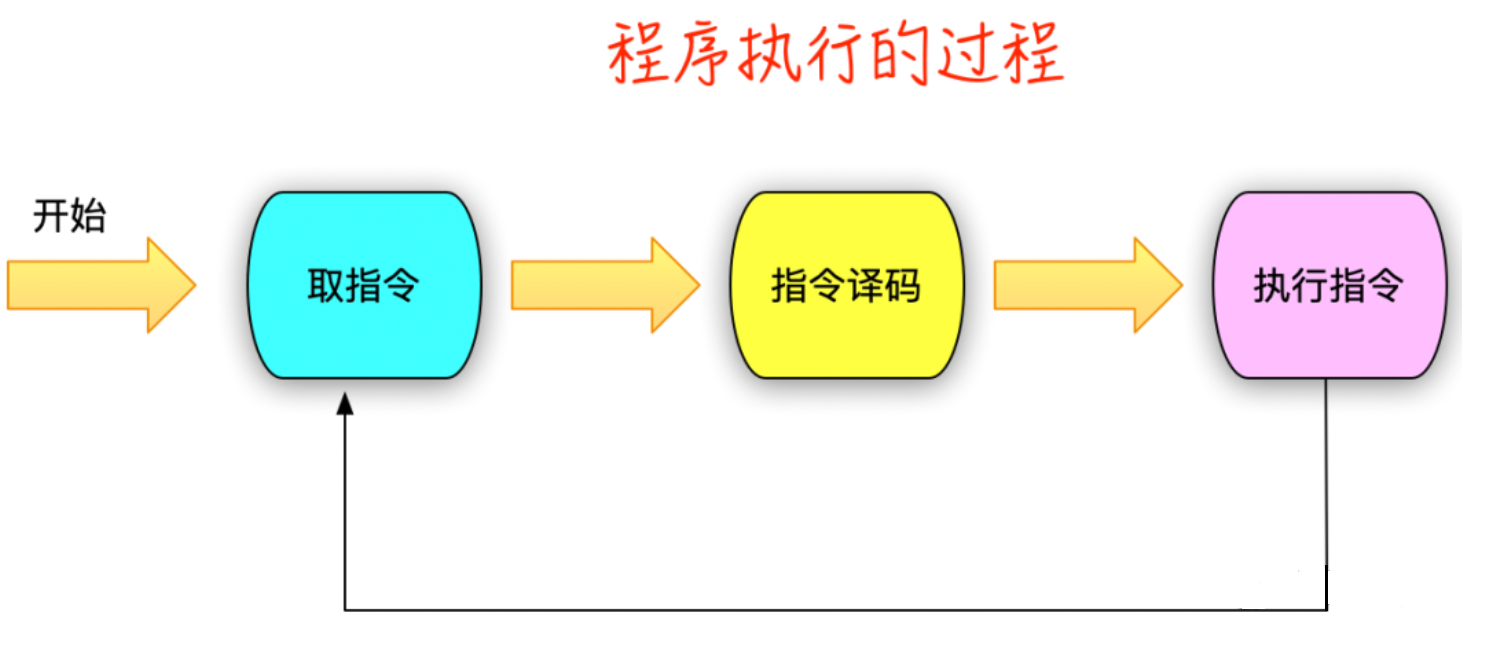

CPU的工作过程

CPU的基本工作是执行存储的指令序列,即程序。程序的执行过程实际上是不断地取出指令、分析指令、执行指令的过程。

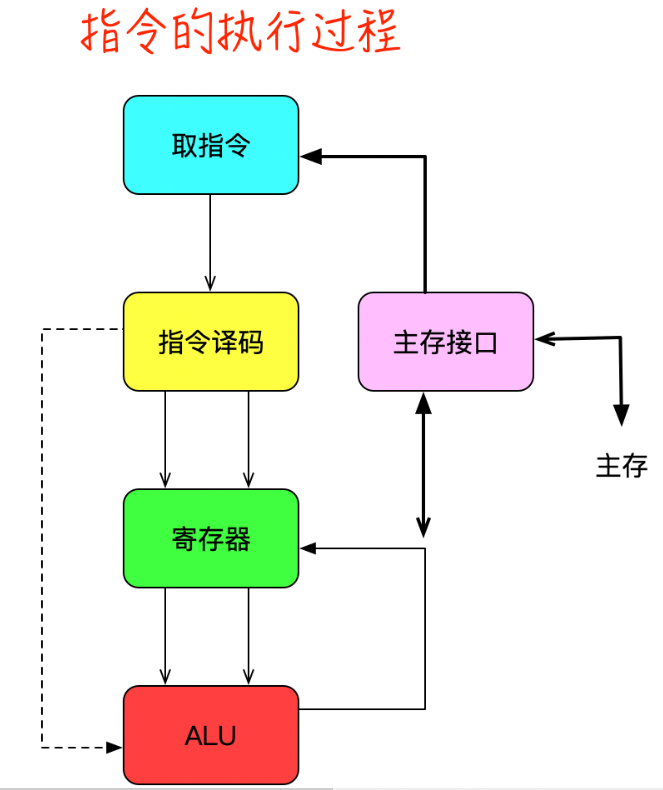

CPU指令的执行流程

一、取指令阶段

取指令(Instruction Fetch,IF)阶段是将一条指令从主存中取到指令寄存器的过程。程序计数器PC中的数值,用来指示当前指令在主存中的位置。当一条指令被取出后,PC中的数值将根据指令字长度而自动递增。

二、指令译码阶段

取出指令后,计算机立即进入指令译码(Instruction Decode,ID)阶段。在指令译码阶段,指令译码器按照预定的指令格式,对取回的指令进行拆分和解释,识别区分出不同的指令类别以及各种获取操作数的方法。

三、执行指令阶段

在取指令和指令译码阶段之后,接着进入执行指令(Execute,EX)阶段。此阶段的任务是完成指令所规定的各种操作,具体实现指令的功能。为此,CPU的不同部分被连接起来,以执行所需的操作。

四、访存取数阶段

根据指令需要,有可能要访问主存,读取操作数,这样就进入了访存取数(Memory,MEM)阶段。此阶段的任务是:根据指令地址码,得到操作数在主存中的地址,并从主存中读取该操作数用于运算。

五、结果写回阶段

作为最后一个阶段,结果写回(Write Back,WB)阶段把执行指令阶段的运行结果数据“写回”到某种存储形式。结果数据经常被写到CPU的内部寄存器中,以便被后续的指令快速地存取;

在有些情况下,结果数据也可被写入相对较慢、但较廉价且容量较大的主存。许多指令还会改变程序状态字寄存器中标志位的状态,这些标志位标识着不同的操作结果,可被用来影响程序的动作。

在指令执行完毕、结果数据写回之后,若无意外事件(如结果溢出等)发生,计算机就接着从程序计数器PC中取得下一条指令地址,开始新一轮的循环,下一个指令周期将顺序取出下一条指令。

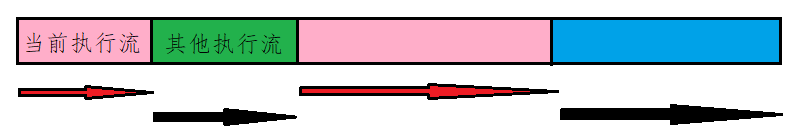

CPU 的中断模式(Interrupt Mode)

在正常情况下,CPU 可以顺序执行,也可以分支执行。但总归是按照既定顺序去执行。

但现实中,很多时候,需要暂时中断 CPU 的当前执行流,先让 CPU 去做点其他的工作,再回头来继续原来的执行流。

CPU 硬件中提供了一种机制(中断)让 CPU 停下:

- 保存当前的 PC 的值到内存的某个位置

- 修改 PC 的值,让执行其他执行流

- 其他执行流执行结束之后,通过将刚才保存的 PC 值恢复到 PC 寄存器

- 继续原来的执行流

本文介绍了计算机的发展历程,重点讲解了冯诺依曼体系结构及其在现代计算机中的应用。CPU作为计算机的核心,由运算器和控制单元组成,负责指令的执行。文章详细阐述了CPU的基本工作过程,包括取指令、指令译码、执行指令、访存取数和结果写回五个阶段,并提及了中断模式。通过生动的比喻,帮助读者理解CPU如何处理数据和控制程序流程。

本文介绍了计算机的发展历程,重点讲解了冯诺依曼体系结构及其在现代计算机中的应用。CPU作为计算机的核心,由运算器和控制单元组成,负责指令的执行。文章详细阐述了CPU的基本工作过程,包括取指令、指令译码、执行指令、访存取数和结果写回五个阶段,并提及了中断模式。通过生动的比喻,帮助读者理解CPU如何处理数据和控制程序流程。

702

702