Linux102系列会详细讲解Linux0.11版本中的102个文件,本文讲解linux0.11的第45个文件

【Linux102】45-kernel/blk_drv/ramdisk.c的文件源码。

1. ramdisk.c的主要作用

这是内存虚拟盘驱动程序,由 Theodore Ts’o 编制。

其含义为:

若在 linux/Makefile 文件中指定了 RAMDISK,则表示在引导启动盘上从第 256 磁盘块开始处会存放着根文件系统映像文件。

在初始化时系统会在内存中划出一部分供虚拟盘操作使用,其大小由 RAMDISK 指定(千字节)。在进行正常的根文件系统加载之前,系统会执行 rd_load() 函数,试图从磁盘的第 257 块中读取根文件系统超级块。若成功,就把该根文件映像文件读到内存虚拟盘中,并把根文件系统设备标志 ROOT_DEV 设置为虚拟盘设备(0x0101),否则退出 rd_load()·,系统继续从 别的设备上执行根文件加载操作。

2.源码用到的文件

| 文件名 | 作用 |

|---|---|

| 😉【Linux102】20-include/linux/kernel.h | 本程序主要定义了内核中最常用的一些基础函数声明,是内核运行最基本保障,比如malloc、printk、free、tyy_write、panic等函数声明,这些函数具体的实现则分布在各个.c文件中。 |

| 😉【Linux102】21-include/asm/segment.h | 本程序定义了一系列用于在 Linux 内核中访问用户空间内存的内联函数,主要通过内嵌汇编操作段寄存器fs来实现内核与用户空间的数据交互。 |

| 😉【Linux102】24-include/linux/fs.h | 这个文件(fs.h)是操作系统内核中文件系统模块的核心头文件,它的主要作用是定义文件系统实现所需的数据结构、常量、宏和函数接口,为整个文件系统的运作提供基础框架。 |

| 😉【Linux102】36-include/asm/system.h | 该文件中定义了设置或修改描述符/中断门等的嵌入式汇编宏。其中,函数 move_to_user_mode() 用于内核在初始化结束时 “切换”到初始进程(任务0)。所使用的方法是模拟中断调用返回过程,即利用指令iret运行初始任务0。 |

| 😉【Linux102】42-include/linux/config.h | config.h 是一个配置文件,用于设置键盘布局和硬盘参数(备用)。设计目的:提供可配置的选项,适配不同的硬件环境。 |

| 😉【Linux102】40-kernel/blk_drv/blk.h | 这是有关硬盘块设备参数的头文件,因为只用于块设备,所以与块设备代码放在同一个地方。其中主要定义了请求等待队列中项的数据结构request,用宏语句定义了电梯搜索算法,并对内核目前支持的虚拟盘、硬盘和软盘三种块设备,根据它们各自的主设备号分别设定了常数值。 |

| 😉【Linux102】47-include/string.h | 声明了一系列标准的字符串操作函数和内存块操作函数。 |

| 😉【Linux102】46-include/asm/memory.h | 基本功能: memcpy用于将一段连续内存(源地址src)中的n个字节,复制到另一段连续内存(目标地址dest)中,返回目标地址dest。 使用场景: 适用于需要高效复制内存数据的场景,例如数据缓冲区拷贝、结构体复制、内存块迁移等。但需注意:源地址和目标地址不能重叠(·重叠内存需用memmove)。 |

3.源码版

/*

* linux/kernel/blk_drv/ramdisk.c

*

* Written by Theodore Ts'o, 12/2/91

*/

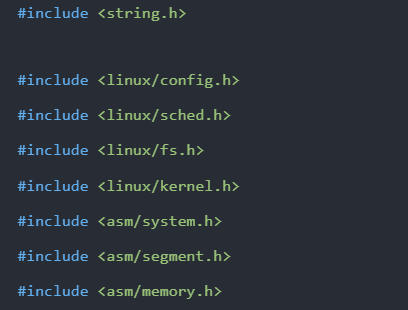

#include <string.h>

#include <linux/config.h>

#include <linux/sched.h>

#include <linux/fs.h>

#include <linux/kernel.h>

#include <asm/system.h>

#include <asm/segment.h>

#include <asm/memory.h>

#define MAJOR_NR 1

#include "blk.h"

char *rd_start;

int rd_length = 0;

void do_rd_request(void)

{

int len;

char *addr;

INIT_REQUEST;

addr = rd_start + (CURRENT->sector << 9);

len = CURRENT->nr_sectors << 9;

if ((MINOR(CURRENT->dev) != 1) || (addr + len > rd_start + rd_length))

{

end_request(0);

goto repeat;

}

if (CURRENT->cmd == WRITE)

{

(void)memcpy(addr,

CURRENT->buffer,

len);

}

else if (CURRENT->cmd == READ)

{

(void)memcpy(CURRENT->buffer,

addr,

len);

}

else

panic("unknown ramdisk-command");

end_request(1);

goto repeat;

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

637

637

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?