以太网交换芯片及PHY处理相关

以太网交换芯片

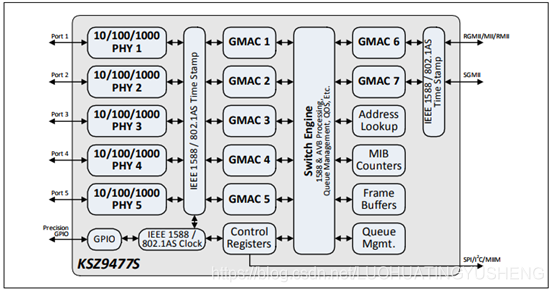

下图为Microchip公司的一款产品,即就是Ethernet Switch。

请参考:https://www.microchip.com/wwwproducts/en/ksz9477

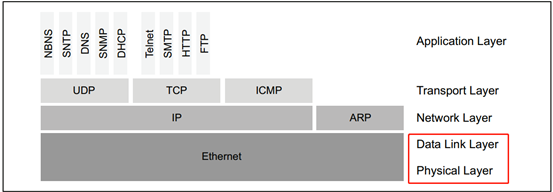

该芯片主要工作于计算机网络模型中的第二层中,通常都会包含以下几种功能模块。

以太网简易结构:

ACL:访问控制列表(Access Control List,ACL) 是路由器和交换机接口的指令列表,用来控制端口进出的数据包。ACL适用于所有的被路由协议,如IP、IPX、AppleTalk等。

信息点间通信和内外网络的通信都是企业网络中必不可少的业务需求,为了保证内网的安全性,需要通过安全策略来保障非授权用户只能访问特定的网络资源,从而达到对访问进行控制的目的。简而言之,ACL可以过滤网络中的流量,是控制访问的一种网络技术手段。

配置ACL后,可以限制网络流量,允许特定设备访问,指定转发特定端口数据包等。如可以配置ACL,禁止局域网内的设备访问外部公共网络,或者只能使用FTP服务。ACL既可以在路由器上配置,也可以在具有ACL功能的业务软件上进行配置。

ACL是物联网中保障系统安全性的重要技术,在设备硬件层安全基础上,通过对在软件层面对设备间通信进行访问控制,使用可编程方法指定访问规则,防止非法设备破坏系统安全,非法获取系统数据。

Queue Mgmt:队列管理。TCP/IP拥寒控制主要包括两个方面,一是发送端的拥塞控制,称为源端拥塞控制,二是中间节点的拥塞控制,称为队列管理。

中间节点有2类和拥塞控制相关的队列算法:队列调度算法和队列管理算法。前者决定下一个要发送哪个包,主要用来管理各流之间带宽的分配;后者主要是在网络发生拥塞时通过丢包来管理队列长度。目前的队列管理机制可以分为2大类:被动式队列管理POM(Passive 0ueue Management)和主动式队列管理AQM(Active Queue Management)。

Frame buffer:

封装包的缓冲原因见下面的连接,比较专业。

1.https://wenku.baidu.com/view/a152bd915ebfc77da26925c52cc58bd630869342.html

2.http://blog.sina.com.cn/s/blog_61bd83dc0100t8e7.html

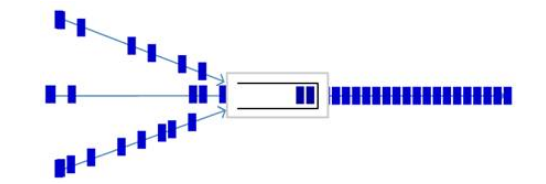

帧缓存的作用是先把离散的帧进行缓存,再按照设备的能力尽力转发,解决流量“峰值”和流量“谷值”导致的带宽利用率不平衡问题。即平滑帧传输突发流量,最大限度使出口带宽保持100%的利用,解决由于突发流量导致的“丢包”现象的必需具备的手段。如下图所示,把流量突发超过带宽的部分缓存起来等待后续时隙去转发,从而实现0丢包率。

帧缓冲简易原理:

Address Table:路由器的主要工作就是为经过路由器的每个数据包寻找一条最佳的传输路径,并将该数据有效地传送到目的站点。由此可见,选择最佳路径的策略即路由算法是路由器的关键所在。为了完成这项工作,在路由器中保存着各种传输路径的相关数据——路由表(Routing Table),供路由选择时使用,表中包含的信息决定了数据转发的策略。打个比方,路由表就像我们平时使用的地图一样,标识着各种路线,路由表中保存着子网的标志信息、网上路由器的个数和下一个路由器的名字等内容。路由表可以是由系统管理员固定设置好的,也可以由系统动态修改,可以由路由器自动调整,也可以由主机控制。

MIB:管理信息库(MIB,Management Information Base)是TCP/IP网络管理协议标准框架的内容之一,MIB定义了受管设备必须保存的数据项、允许对每个数据项进行的操作及其含义,即管理系统可访问的受管设备的控制和状态信息等数据变量都保存在MIB中。

Switch Core:交换控制内核。内核控制一般描述的很少,都是各家在吹自己技术多先进,采用什么控制算法,怎样怎样,其实统一价格下产品都是差不多的。

Switch Port:即就是网络端口,具体看配置及功能,我见过两个端口的、5个端口的,也见过七个端口的;另一般低端的仅支持10兆和百兆,稍微高端一点的支持10兆、百兆和千兆,另有企业级的甚至达到10G端口,这个取决于客户需求。

管理接口:MDI,媒体独立接口,即就是完成对物理层PHY部分的控制,监控或者寄存器的修改,一般是MAC完成对PHY的检测,即就是第二层监控第一层。

MII等接口:MAC端完成数据的在此处理,例如可以连接其他的控制器完成别的功能。例如利用别的控制器完成wifi功能。

该接口在使用时需要注意CLK的方向。

电源:一般采用的是3.3V供电;另需要内部核压以及接口电源供电。有些器件做的比较好,就是将LDO集成到内部,也就是自己产生核压以及接口电压。

Flash接口:如果是路由的话固件一般比较小,所以外挂SPI Flash或者EEProm就可以了,无需Nand 等大存储器件,内部用来储存芯片启动时的一些配置信息。

指示灯:因为实际上我们需要通过指示灯来判断哪个端口已经在正常连接使用了。

除此之外我们实际在开发时需要注意上电初始化的一些配置,比如管理接口的上下拉可以配置访问地址;RMII端口一些上下拉可以配置成RMII、MII等;专用引脚上下拉可以起到硬件识别软件的作用,如启动模式,是在Flash、ROM中启动,这个需要看实际的配置;另有一些芯片做测试使用时的引脚,例如正常启动还是进入测试模式。

PHY设计需注意:

原理图设计:

1.XMII时钟预留RC,用来形成RC滤波器,以防出现EMC问题时无法调整;

2.Data/控制脚留串阻,靠近源端放置,用来阻抗匹配,防置信号完整性问题;

3.网络变压器的中心各个抽头预留两个电容位,有些设计建议单独抽头的网变被使用;

4.PHY的供电预留磁珠/电阻位置,抑制干扰防止通过电源向其它模块辐射或减小纹波或传导干扰;

5.PHY控制的LED灯信号预留RC(靠近IC放),有利于EMC也有利于静电防护;

6.注意PHY的一些外部配置,尽量预留包含所有情况的配置,否则可能出现丢包等问题。

layout设计:

XMII指的是MII接口的变换类型。

1.XMII走线走内层,内层屏蔽更好,可以解决辐射问题。当然走外层带屏蔽也可以,且要注意尽量走线等长处理;

2.芯片端XMII接口连接处确保有完整参考平面,因为总线速率较高,容易出现问题,阻抗尽可能一致;

3.在PHY 芯片预留屏蔽罩,因为有些芯片做的不好,EMC问题常难以通过其他途径解决;

4.网口走线的阻抗控制与包地完整性;

5.注意晶体走线,拉开与关键信号之间的间距。

6.注意网口地和系统地之间的安全间距。

软件调试方法:

1.修改程序对应寄存器的驱动强度,来降低驱动电流;

2.系统端的MII接口可以展频处理,将频谱能量分散开;

3.内置时钟的可以验证使用外置时钟,软件关闭内置时钟。

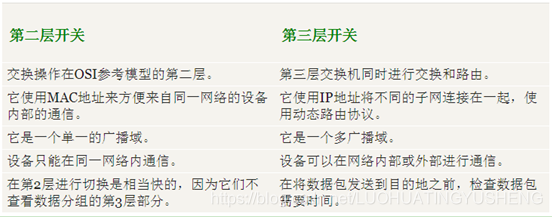

以上讲到的是属于第二层的交换,现在我们科普下第二层和第三层交换的区别。

请参考:http://www.differencebetween.net/technology/difference-between-layer-2-switch-and-layer-3-switch/

什么是第二层交换机?

第二层交换机基本上只进行交换,这意味着它们使用设备的MAC地址将数据包从源端口重定向到目标端口。它通过维护MAC地址表来实现这一点,以记住哪些端口分配了哪些MAC地址。MAC地址在OSI参考模型的第2层内工作。MAC地址简单地区分一个设备和另一个设备,每个设备被分配一个唯一的MAC地址。它利用基于硬件的交换技术来管理局域网(LAN)中的流量。当切换发生在第二层时,这个过程会更快,因为它所做的就是对物理层的MAC地址进行排序。简单地说,第二层交换机充当多个设备之间的桥梁。

什么是第三层交换机?

第三层交换机与第二层交换机正好相反。第二层交换机无法在第三层路由数据包。与第二层交换机不同,第三层使用IP地址进行路由。这是一个专门的硬件设备,用于路由数据包。第三层交换机具有较快的交换能力和较高的端口密度。它们是对传统路由器的重大升级,以提供更好的性能,使用第三层交换机的主要优点是,它们可以在不进行额外网络跳的情况下路由数据包,从而使其比路由器更快。然而,它们缺乏路由器的一些附加功能。第三层交换机在大型企业中普遍使用。简单地说,第三层交换机只不过是一个高速路由器,但没有广域网连接.

两者差异比对图:

上面说的RMII在Ethernet Switch端一般是PHY层处理,PHY层数据一般是交给MAC端处理,完成数据再交换的功能,所以我们要实现射频WiFi等功能还需要外接一个路由主芯片完成WiFi功能;当然也可以将这两个做到一起,前面说了,取决于价格等多方面考虑。

PHY处理相关

以太网PHY相关即就是物理层传输相关。

对于XMII部分时钟:

XMII表示可选择的MII模式,例如千兆和百兆是不一样的。

MAC与PHY相连接时,MAC芯片首先要先送时钟信号给PHY,然后PHY根据收到的时钟信号同步输出相同频率的时钟信号给MAC,以完成自适应。

在网口连接速率为1Gbps时,WIFI芯片到PHY芯片和PHY芯片到WIFI芯片的CLK均为125Mhz,连接速率为100Mbps时,CLK为25MHz。不插网线开机时,两边均有2.5MHz的方波输出(注意当连接为10MHz时,时钟为2.5MHz)。

外部扩展EEPROM:

连接外部EEPROM用于实现没有任何更高级别的系统;管理实体,用于驱动MDIO接口上的控制和配置信息。

此外,仅使用软引脚绑定接口无法完全配置PHY芯片功能,更多功能需要外部软件配置。

在这些应用中,外部EEPROM提供了一种廉价而有效的解决方案,用于存储启动期间PHY芯片需要加载的所有配置信息。

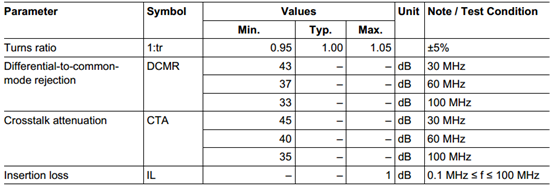

使用网络变压器要求:

以上包括的参数为匝数比、共模抑制比、串扰和插入损耗,当然还需要考虑反射损耗。

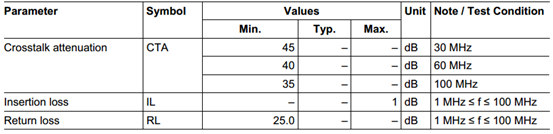

RJ45 PLUG:

以上参数包括串扰、插入损耗和反射损耗。

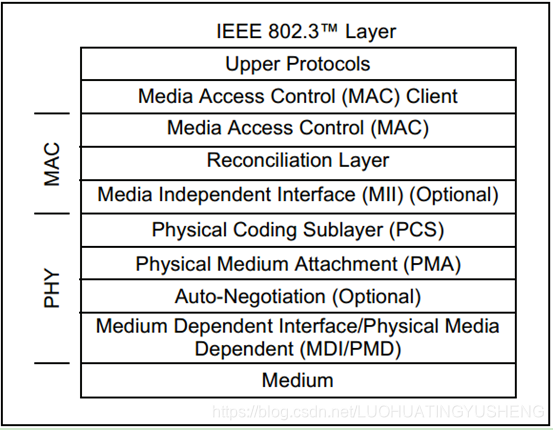

物理层传输和媒体接入控制(PHY&MAC):

媒体接入控制:协议控制层。

协调层:将物理状态(载波丢失,冲突等)映射到MAC层。

媒体独立接口(MII)(可选):为PHY提供n位发送/接收接口。

物理编码子层(PCS):输出符号流的编码,复用和同步(4B / 5B编码等)。

物理媒体附件(PMA):信号发送器/接收器(符号流的串行化/反序列化,时钟恢复等)。

自动协商(可选):协商两台主机支持的最高模式。

介质相关接口/物理介质相关(MDI / PMD):RJ45等

介质:UTP,光纤等

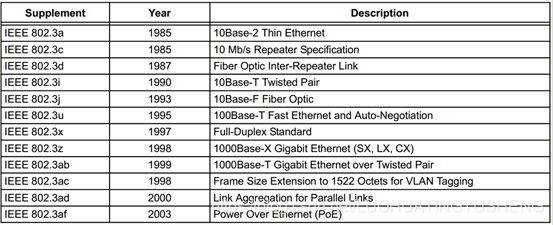

IEEE 802.3规范

针对数据传输所规范的标准协议,包含十兆、百兆、千兆和光纤传输等。

2019.6.13于深圳

本文深入探讨以太网交换芯片及其PHY处理,讲解ACL、队列管理、帧缓存等核心功能,对比第二层与第三层交换机,介绍PHY设计注意事项及软件调试方法。

本文深入探讨以太网交换芯片及其PHY处理,讲解ACL、队列管理、帧缓存等核心功能,对比第二层与第三层交换机,介绍PHY设计注意事项及软件调试方法。

412

412

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?