作为一个很菜很菜的小白,瑾以此文纪念我搞懂了的一个问题,让我很开心。

学校里的实验课会用到ISE软件,但是课上的实验也仅仅教了如何使用代码完成功能,或者如果做一个IP核,或者如果单纯用原理图实现。在大三的课设,需要做一个很简单的小项目,为了较为简单的实现(只用原理图需要超级超级多的门电路),在一个仿真项目里需要综合运用IP核、原理图、代码。

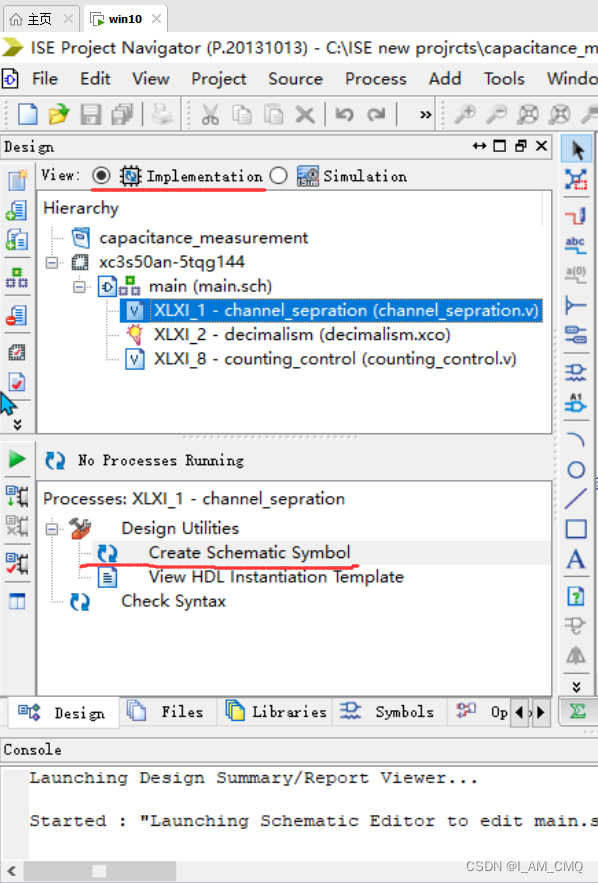

见上图。

我的步骤是,先新建一个原理图(Schmatic)的文件,接着就是new source(如何新建工程比较简单,此不赘述)。需要注意的点我用红笔标出来了。

new source IP核,成功后,在原理图的布置里面自然会出现该IP核,但是new source Verilog,写完代码后,需要点击“Create Schematic Symbol”,才能在原理图的布置中找到我们所写代码生成的原理图。

博主作为小白,分享搞懂问题的喜悦。学校实验课用ISE软件,仅教代码、IP核或原理图实现功能。大三课设需综合运用IP核、原理图和代码完成小项目,还介绍了新建原理图文件、添加IP核和Verilog代码的步骤及注意点。

博主作为小白,分享搞懂问题的喜悦。学校实验课用ISE软件,仅教代码、IP核或原理图实现功能。大三课设需综合运用IP核、原理图和代码完成小项目,还介绍了新建原理图文件、添加IP核和Verilog代码的步骤及注意点。

930

930

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?