干了十几年芯片测试,从最早的8寸晶圆厂到现在搞先进封装测试,被问最多的问题就是:“CP和FT到底该怎么分配测试项?” 这问题看似基础,实则每个项目都在动态调整。今天结合几个实际项目案例,聊聊我的经验,也欢迎同行一起讨论。

一、基础认知:别把“工序差异”理解成“目的差异”

新人容易陷入一个误区:认为CP只管“死活”,FT才测“性能”。实际上,两者的核心差异在于测试对象的状态不同,而非测试目的有本质区别。

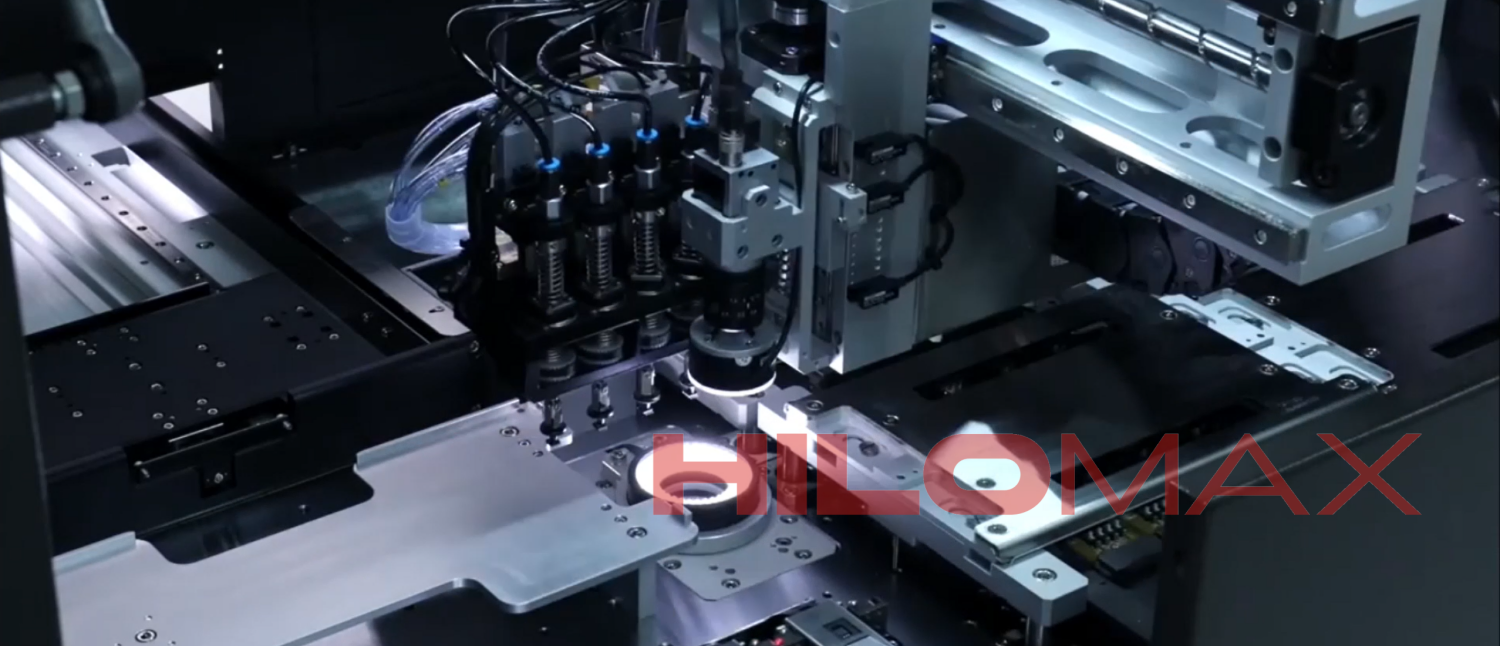

CP阶段,芯片还是晶圆上的裸晶(Die)。我们用探针卡直接接触焊盘,优势是能直接测量晶体管级参数(如漏电流),劣势是高频信号完整性差、测试温度范围有限。所以CP策略的关键是:用最短时间、最低成本,筛选出明显不良的Die,避免后续封装浪费。 我们团队内部有句话:“CP花的每一分钟,都在替封装省钱。”

FT阶段,芯片已完成封装。此时测试的是“成品”,必须模拟真实应用场景。优势是可进行全速、全温度范围测试,劣势是无法再直接探测芯片内部节点。FT策略的核心是:确保交付的每颗芯片,在规格书定义的所有条件下都能稳定工作。

简单来说:CP是“经济性筛选”,FT是“品质保证”。

二、策略演进:三个实际案例看边界如何移动

这些年,CP和FT的边界一直在变。分享三个项目案例:

案例1:消费级MCU(40nm工艺)

这是最传统的模式。CP只测基本参数(开路/短路、IDDQ、低频功能),耗时<2秒;FT覆盖全部功能、速度和温度测试,耗时约6秒。策略很清晰:封装成本低,CP不必做太细。

案例2:手机AP芯片(5nm工艺)

情况变了。封装用上Fan-out,成本占比飙升。我们调整策略:在CP加入高速SerDes的初步链路训练测试,将部分性能Binning提前。虽然CP时间增加到4秒,但筛掉了一部分“封装后也过不了FT”的Die,总体成本反而下降。这里的关键是:用CP时间换封装成本,划算。

案例3:AI Chiplet(异构集成)

这是当前最前沿的挑战。芯片由多个Chiplet(计算芯粒、HBM等)通过硅中介层集成。最大转变是:CP测试重心从“筛坏Die”转向“为系统集成提供已知合格芯粒(KGD)”。我们对每个Chiplet在CP阶段进行近乎FT级别的测试,因为封装后基本无法单独重测某个芯粒。CP时间大幅增加,但这是确保最终系统良率的唯一途径。

三、实战心得:四个关键决策因素

根据这些经验,我们团队现在评估CP/FT策略时,主要看四个维度:

1.封装成本占比

这是最直接的杠杆。封装成本超过芯片制造成本20%时,就必须考虑在CP加测试项。公式不复杂:对比“增加CP测试时间成本”和“为不良Die支付封装成本”,取最小值。

2.故障覆盖率分析

不是所有缺陷都适合在CP测。我们会对早期失效芯片做FA(失效分析),如果发现某类缺陷(如某些封装应力导致的时序问题)在CP阶段无法有效检出,就果断把它放到FT。“能测准”比“测得早”更重要。

3.测试接口的物理限制

这是硬约束。比如DDR5接口全速测试,探针卡方案目前还很难实现,这类测试只能放在FT。每次工艺升级,我们都会重新评估探针技术的能力边界。

4.数据流与溯源需求

对于车规、工控等高可靠性芯片,需要完整的测试数据追溯。我们会让CP和FT测试项有一定重叠,通过数据对比分析,定位缺陷是晶圆制程引入还是封装过程引入。这虽增加了总测试时间,但提升了质量管控能力。

四、给新人的两条建议

1.不要盲目追求“CP全覆盖”

见过一些团队为了追求“高级感”,把所有测试都往CP塞,结果测试时间爆炸,探针卡损耗剧增,总成本反而更高。一定要算经济账。

2.尽早让测试工程师参与芯片设计

特别是DFT(可测性设计)环节。如果设计时就考虑了如何在CP阶段访问关键电路,后期测试策略会灵活得多。我们最近一个项目,因为早期协同,在CP实现了通过IEEE 1500接口测试芯粒间互连,省掉了大量FT开发时间。

最后抛个颇有争论的问题:

对于一颗采用3D堆叠的存储计算一体芯片,底部逻辑芯片的CP测试,应该做到多彻底?是应该尽可能测全(保证上层存储堆叠的基底可靠),还是适度测试(接受部分风险以控制CP成本,靠FT来把关)?

256

256

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?