5.1 CPU的功能和结构

一、 CPU 的功能

1. 控制器的功能

取指令

分析指令

执行指令,发出各种操作命令

控制程序输入及结果的输出

总线管理

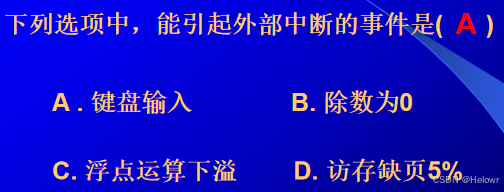

处理异常情况和特殊请求

2. 运算器的功能

实现算术运算和逻辑运算

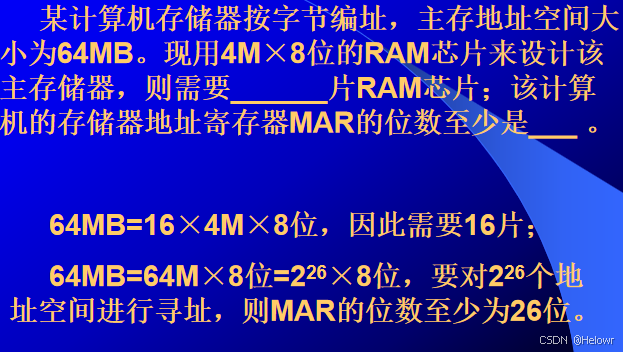

二、 CPU 的寄存器

1. 用户可见寄存器

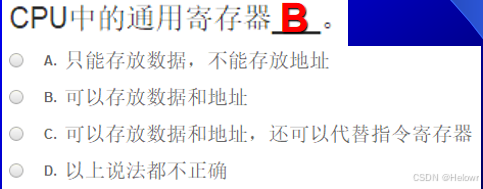

(1) 通用寄存器

存放操作数 可作 某些寻址方式所需的 专用寄存器

(2) 数据寄存器

存放操作数(满足各种数据类型)

两个寄存器拼接存放双倍字长数据

(3) 地址寄存器

存放地址,其位数应满足最大的地址范围

用于特殊的寻址方式 段基值 栈指针

(4) 条件码寄存器

存放条件码,可作程序分支的依据

如 正、负、零、溢出、进位等

2. 控制和状态寄存器

(1) 控制寄存器

控制 CPU 操作

其中 MAR、MDR、IR 用户不可见

PC 用户可见

(2) 状态寄存器

存放条件码

PSW 寄存器 存放程序状态字

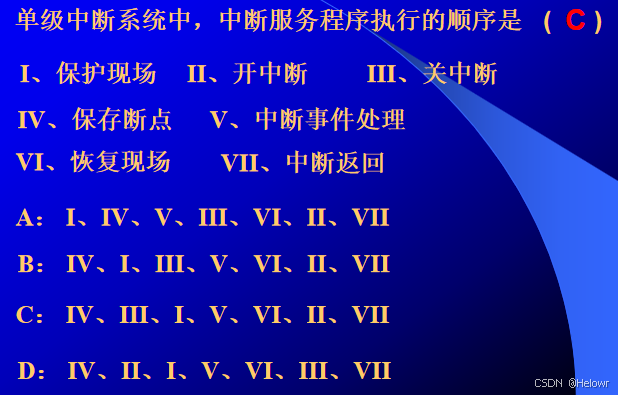

通常在中断时,保存现行程序中断现场和断点用的就是PSW寄存器,便于中断的返回;PSW寄存器的位数一般比较长,有几百甚至上千位。

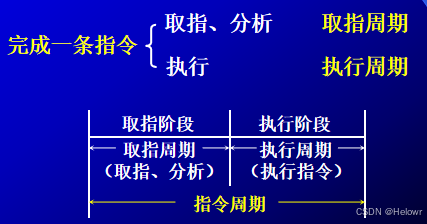

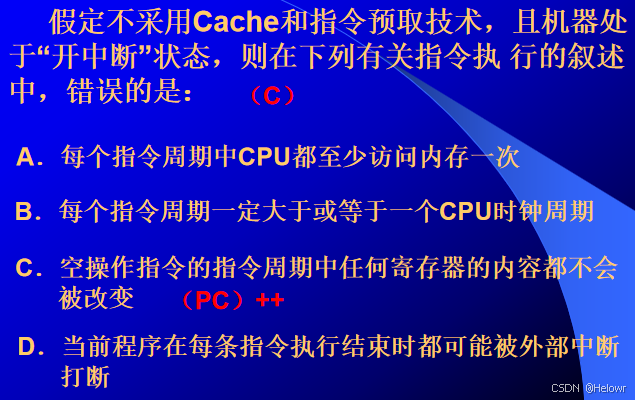

5.2 指令周期

取出并执行一条指令所需的全部时间

指令周期:取指指令、分析指令到执行完该指令所需的全部时间。

通常把一条指令周期划分为若干个机器周期,每个机器周期完成一个基本操作。

主存的工作周期(存取周期)为基础来规定CPU周期,比如,可以用CPU读取一个指令字的最短时间来规定CPU周期

不同的指令,可能包含不同数目的机器周期。

一个机器周期中,包含若干个T周期(节拍脉冲或T脉冲,处理操作的最基本单位),也叫时钟周期。

5.3 指令流水

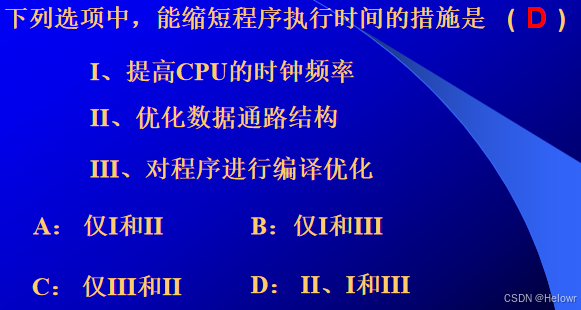

一、如何提高机器速度

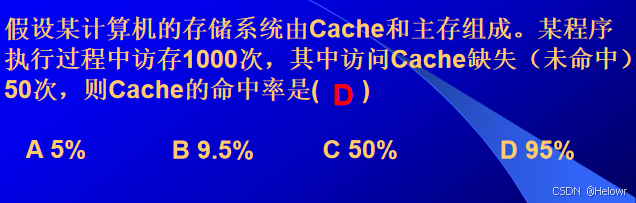

1. 提高访存速度

高速芯片 Cache 多存储体并行

2. 提高 I/O 和主机之间的传送速度

中断 DMA 通道 I/O 处理机 多总线

3. 提高运算器速度

高速芯片 改进算法 快速进位链

提高整机处理能力

高速器件 改进系统结构 ,开发系统的并行性

二、系统的并行性

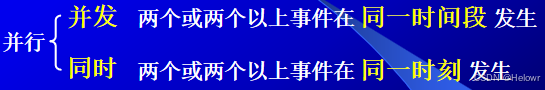

1. 并行的概念

2. 并行性的等级

过程级(程序、进程) 粗粒度 软件实现

指令级(指令之间) (指令内部) 细粒度 硬件实现

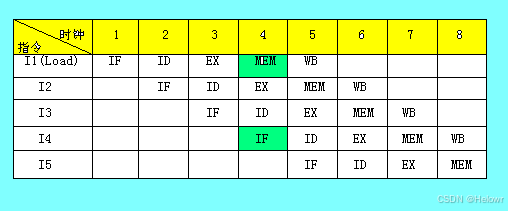

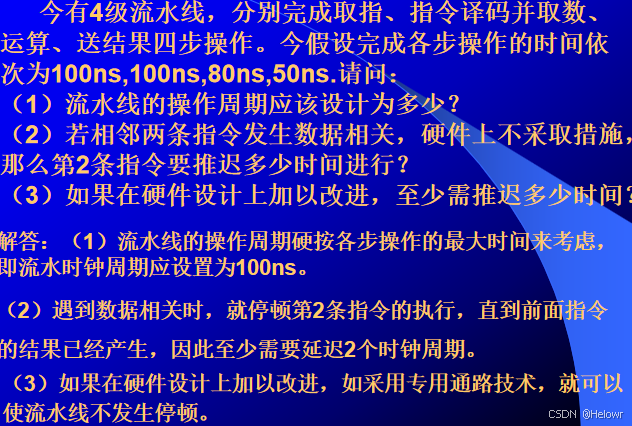

影响指令流水效率加倍的因素

(1) 执行时间 > 取指时间

(2) 条件转移指令 对指令流水的影响

必须等 上条 指令执行结束,才能确定 下条 指令的地址, 造成时间损失

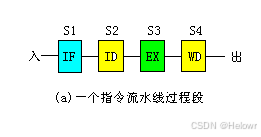

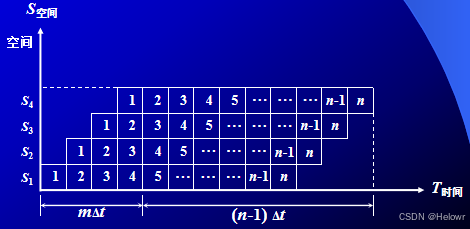

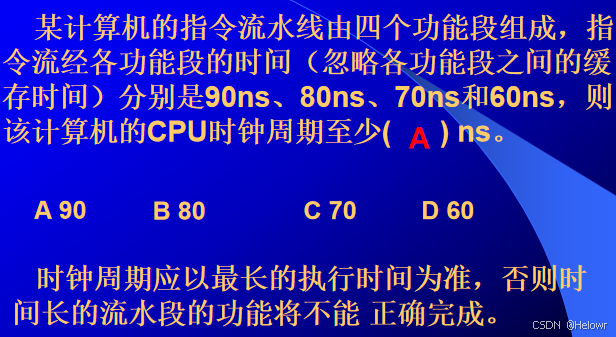

流水线CPU时空图

指令流水线中的主要问题

瓶颈问题(流水线中有速度慢的段)

再分成几个段

用资源重复的方法也可以解决

资源相关:多条指令进入流水线后在同一时钟周期内争用同一功能部件。

解决办法:

后边指令拖一拍再推进;

增设一个功能部件

三、影响指令流水线性能的因素

1. 结构相关

不同指令争用同一功能部件产生资源冲突

解决办法

停顿

指令存储器和数据存储器分开

2. 数据相关

不同指令因重叠操作,可能改变操作数的 读/写 访问顺序

解决办法

后推法

3. 控制相关

由转移指令引起

四、流水线性能

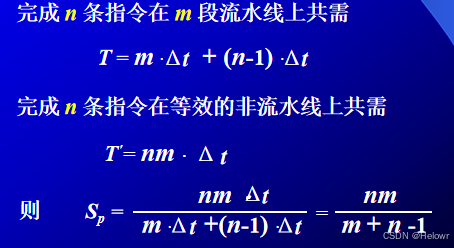

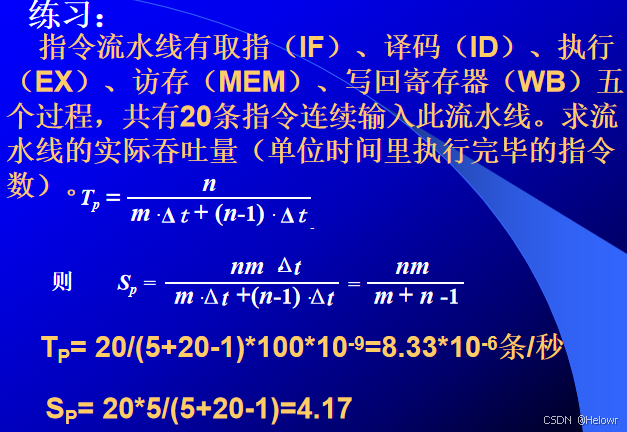

1. 吞吐率

单位时间内 流水线所完成指令 或 输出结果 的 数量

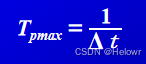

最大吞吐率

流水线满负荷运转时的吞吐率

设一个m 段的流水线,各段时间为 Δ

实际吞吐率

在一段时间之内,流水线真正完成的指令数 除以完成这些指令花费的时间。

2. 加速比 Sp

m 段的 流水线的速度 与等功能的 非流水线的速度 之比

设流水线各段时间为 Δt

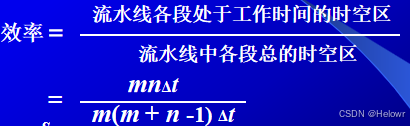

3. 效率

流水线中各功能段的 利用率

由于流水线有 建立时间 和 排空时间 因此各功能段的 设备不可能 一直 处于 工作 状态

1900

1900

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?