关注、星标公众号,精彩内容每日送达

来源:网络素材作者:Ivy Guo,AMD工程师;文章来源:AMD开发者社区

SEM IP是一个非常‘安静’的IP。

构建的时候,它的逻辑就是独立于用户系统设计的,并用区域约束做了一定的分割。对于它唯一的时钟信号,我们也是建议越独立越好。最好用单独的晶振从一个GPIO引入。如果资源有限需要和用户逻辑共享时钟,也是推荐使用MMCM/PLL的一个单独输出口,并且针对系统主要逻辑的toggle做一个90度的相移。

另外由于SEU事件及其稀少,对某一片特定的芯片来说,可能数年才能发生一起SEU事件,所以IP工作状态可谓异常‘安静’:初始化结束后,就一直处于Observation状态下,后台持续扫描检测,没有‘意外’就不会有任何动作产生。

基于上述两个原因,会有很多客户问:我的设计里面添加了SEM IP,如何知道IP已经开始正常工作,还是有什么意外停止了?

PG187 https://docs.amd.com/r/en-US/pg187-ultrascale-sem 关于IP各个状态的工作情况有详细的描述,当然可以作为判断依据。这里我们讨论几个最简单最常见的判断方法。

01

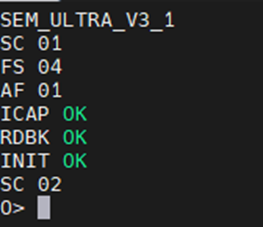

看系统输出的log

IP的行为,从初始化状态开始到各个事件的发生,都会由IP自带的串口输出详细的记录log。比如以下是IP的初始化log:

这个log清楚表明了IP的名称,基本配置信息,进入Initialization阶段做的各项检查,通过后则正确进入了工作状态Observation。检查log是否符合预期,可以得知绝大多数异常情况。

02

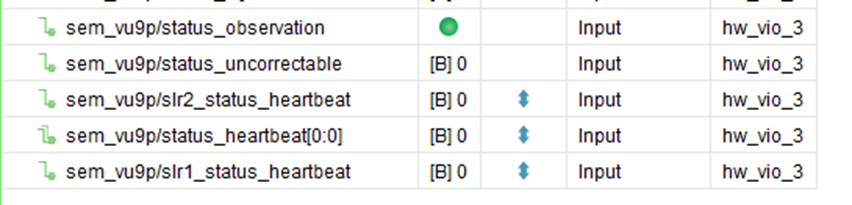

检查IP的心跳

对于UltraScale/+ 系列器件,SEM IP在工作状态Observation时,是不停地有心跳信号status_heartbeat产生的。不同的器件心跳的间隔会有一些差异,但我们建议一旦心跳停止的时间超过1秒钟,可以认为IP已经不再正常工作了。

03

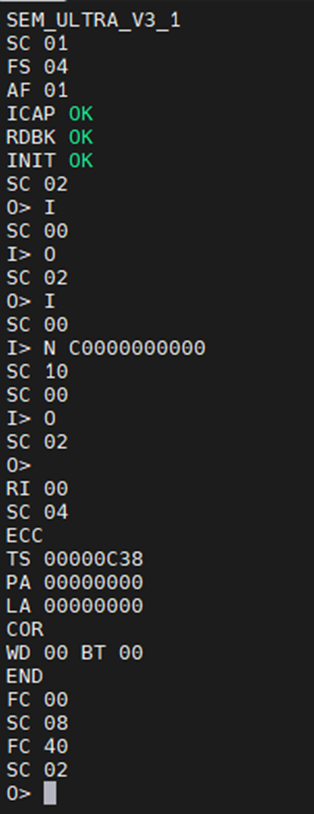

“让IP动一下”

IP的Command Interface和Uart Interface都可以用于向IP发送指令。如果IP能够正常响应我们发出的指令,那么它就是‘健康’的。每个Interface支持的指令都可以用于这个功能,我们挑选最简单直接的测试即可。

比如切换一下IP的状态,让它从Observation进入IDLE状态,再从IDLE返回Observation。

进入IDLE状态后,可以顺便再检测一下IP的插错纠错功能。

IP在回到Observation状态后会纠错并且报告。

如果这一过程正常,IP基本都没有问题。

有一点要注意,插错时请遵循IP的 “Error Injection Guidance” 去选择插错的地址(Appx. F: Error Injection Guidance, PG187)。因为有些bit位置是被屏蔽掉的,插入这类位置,IP回到Observation状态并没有纠错动作,也不会报告信息。经常也有客户据此反馈IP无法正常工作,这是个误解。一般来说,只要IP能响应你的某一个bit位置的插错动作,IP就是没有问题的。当然可以插错的位置比不可插的位置要多得多。

04

没有log怎么办?

请参阅之前写的《如何利用FIFO+ILA/VIO抓取SEM IP的串口log》一文。

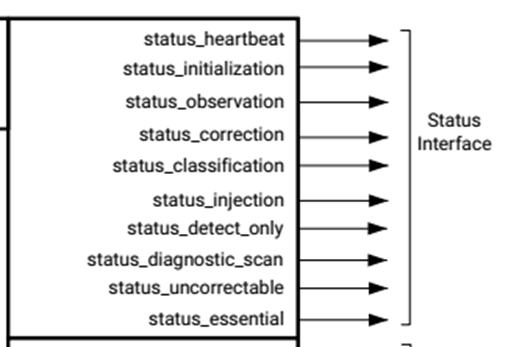

另外也可以通过status_xxx几个端口组合来简单判定一下。

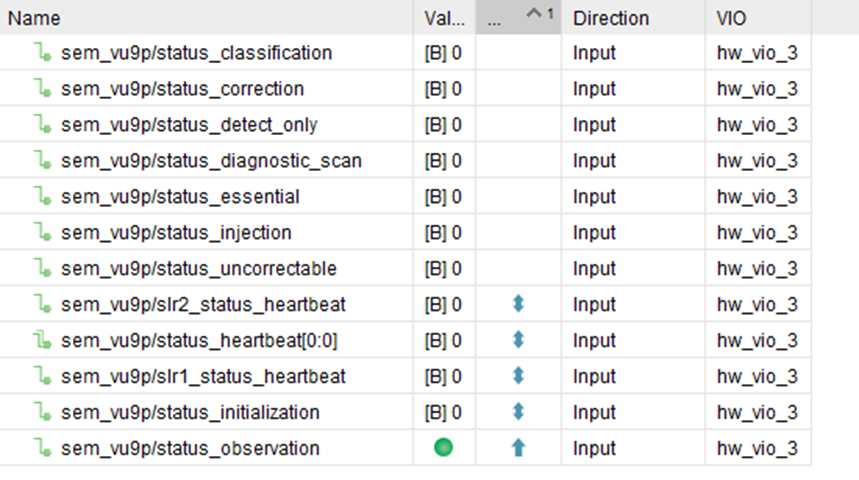

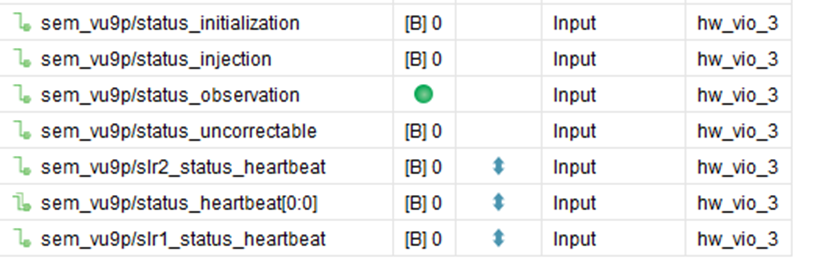

IP初始化时,status_initialization端口输出高电平,其他都是低电平。(这个过程比较短暂,下面截图显示Initialization有过高,正在进入Observation状态)。

开始工作之后则是status_observation为高,其他都为低。正常工作的Observation状态,status_heartbeat一直是跳动的状态。

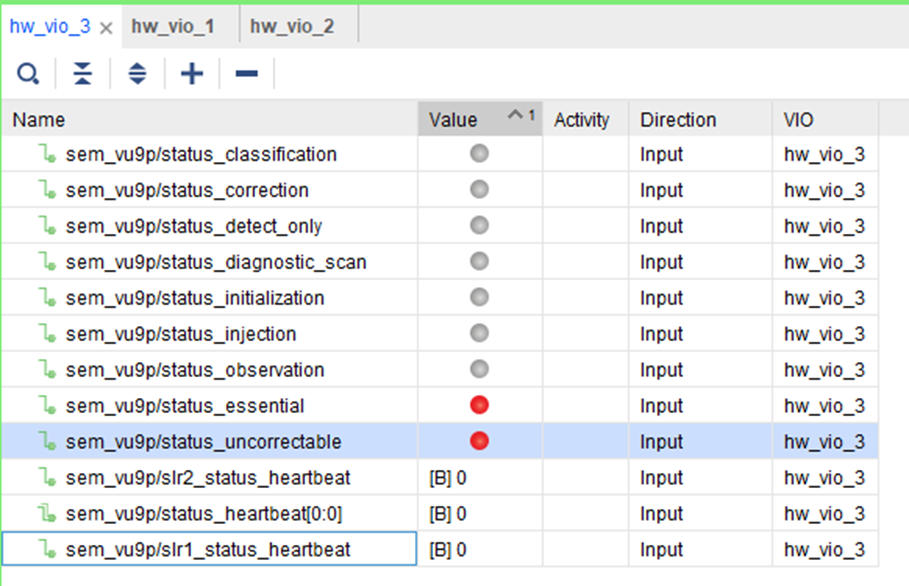

如果IP遇到不可纠错误,通过log上报后会进入IDLE状态,此时status_initialization,status_observation, status_correction,status_correction, status_classification, status_heartbeat等端口全部为0. Status_uncorrectable和status_essential会置1.

如果IP自己遭到了SEU事件攻击,或者噪声的干扰而异常,则log上报错误后会进入HLT状态,此时上述这些端口全部置为高电平。当然,有时IP还来不及上报就失效了,此时status_heartbeat信号一定没有了。通过心跳信号的消失就可以辅助判断异常已经产生。

以上为几个简单直接的判定方法。更详细的IP行为及其解析,请参考PG187:https://docs.amd.com/r/en-US/pg187-ultrascale-sem

(全文完)

声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

812

812

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?