Preface

This note only introduce the essential concepts about Static Timing Analysis, which not contains:

- Async, i.e. remove, recover

- Timing conceptions, i.e. false path, multi cycle path etc.

- Advance timing domain knowledge

- POCV, MCMM etc.

什么是 STA

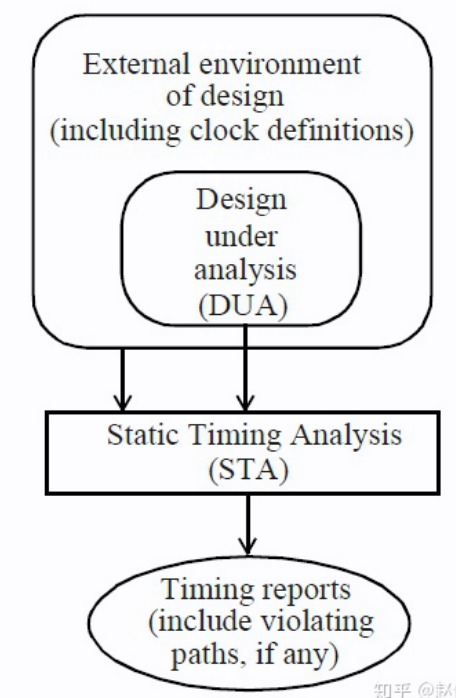

由于时钟频率越快,芯片中的逻辑单元在单位时间内能够完成的操作就越多,所以频率与芯片性能成正相关。而芯片设计需要在 PPA 之间 tradeoff,那么如何才能知道一枚芯片正常工作的频率极限到底是多少呢?这就引入了 STA 静态时序分析的概念。

STA 用于验证设计是否能够安全运行在给定的时钟频率下且没有时序违例。STA存在以下特点:

- Pros

- 无需输入激励仿真

- 完备的时序检查

- Cons

- 无法处理异步时序

STA 应用场景

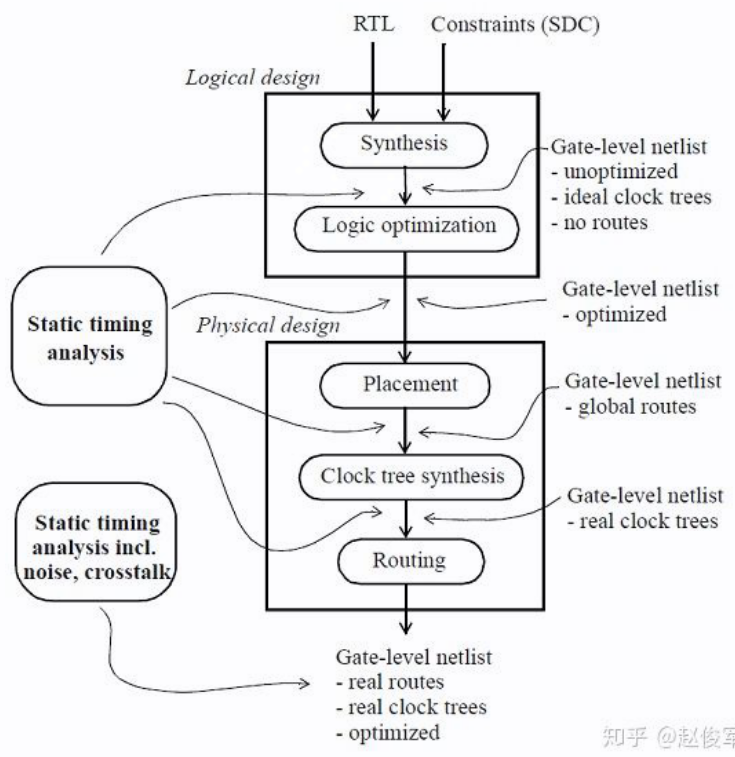

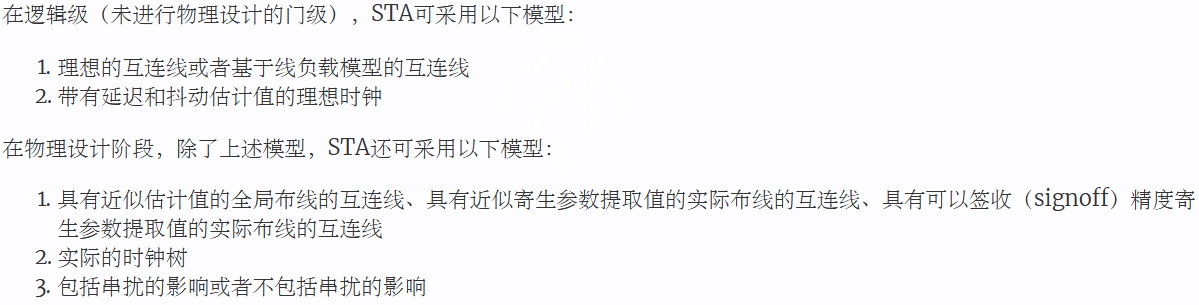

STA 可以应用于 PD 多个阶段,并且分别具有不同特点,如:

- synthesis: 在逻辑设计阶段,由于没有与布局有关的物理信息,因此可以假设互连线是理想状态的,此阶段会更关注查看导致最差路径的逻辑。在这个阶段使用的另一种技术是采用线负载模型(wireload model)来估算互连线的长度, 线负载模型会基于逻辑单元的扇出提供一个估计的RC值。

- Pre-CTS: 在物理设计的一开始,时钟树被认为是理想的,即它们具有零延迟。而在 CTS 后,时钟则具有实际的 propagate delay

- Pre-Route: 在实际布线前,STA 用于计算延迟的金属线寄生 RC 为估计值。

Cell

单元可以是标准单元、IO缓冲器或者是如USB内核这样的复杂 IP。除时序信息外,库单元描述中还包含一些其它属性,例如单元面积和功能,这些属性与时序无关,但在RTL综合(synthesis)过程中会用到。

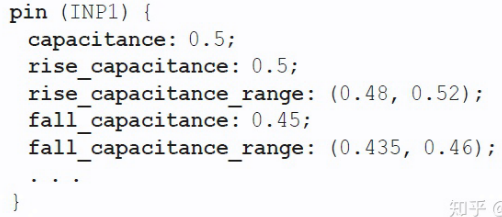

引脚电容

单元的每个输入和输出都可以在引脚(pin)上指定电容。在大多数情况下,仅为单元输入引脚指定电容,而不为输出引脚指定电容,即大多数单元库中的输出引脚电容为0

上面的示例展示了输入INP1引脚电容值的一般规格(specification)。在最基本的格式中,引脚电容被指定为单个值(在上面的示例中为0.5个单位)。电容单位通常为皮法拉(pF),一般在库文件的开头指定。单元描述中还可以为rise_capacitance(0.5个单位)和fall_capacitance(0.45个单位)分别指定值,这些值是指引脚INP1上发生电平上升和下降跳变时的值。也可以将rise_capacitance和fall_capacitance的值指定为范围,并在描述中指定下限值和上限值。

驱动强度

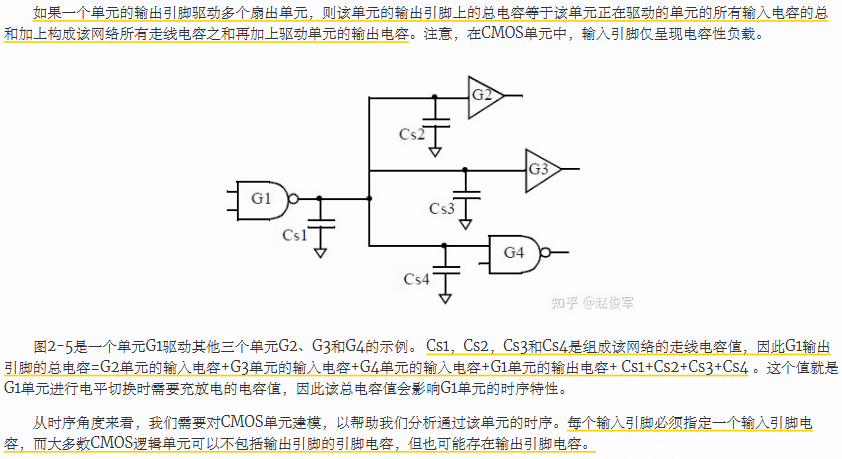

输入引脚电容定义在 liberty 中,而输出引脚电容则由该单元驱动的所有下级单元所决定。当CMOS单元切换电平状态时,切换的速度取决于输出引脚上的电容被充放电的速度。

通常来说,单元驱动强度决定了可以驱动的最大电容负载,最大电容负载又决定了扇出的最大数量,即可以驱动多少个其他单元。较高的输出驱动对应较低的输出上拉/下拉电阻,这使单元可以在输出引脚上对较大的负载进行充电和放电。

- 驱动强度越大则单元面积越大,且

max_cap也越大。 - 驱动强度越大,对应的输出电阻越小,延迟也就越小。

- 如果标准单元库中只有小驱动强度的标准逻辑单元,则对时序有何影响?

- 当整个库只有小驱动单元时,首先想到的是每个单元的驱动能力弱,输出电阻更大。

- 如果一个反相器的驱动强度小,那么它能够驱动的最大负载电容也较小。如果设计中某些节点必须驱动较大的电容,比如长线或高扇出网络,这时候小驱动单元可能无法满足需求,从而导致建立时间或保持时间违规。

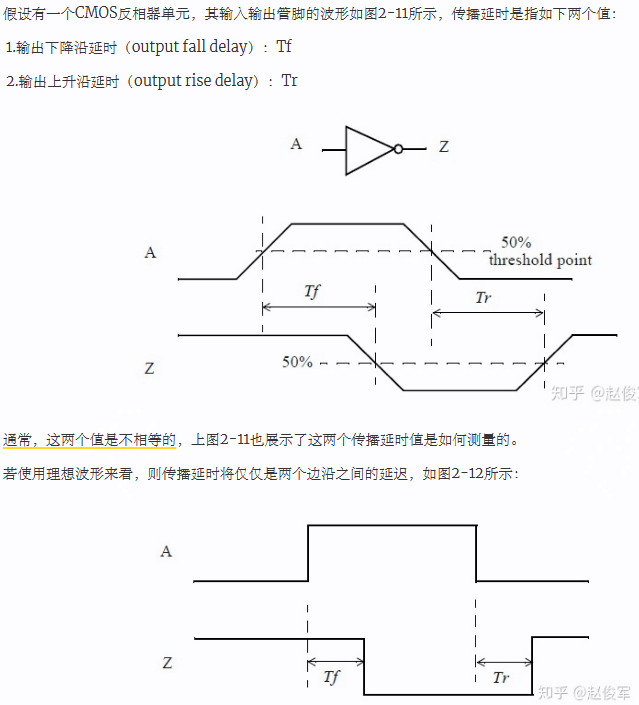

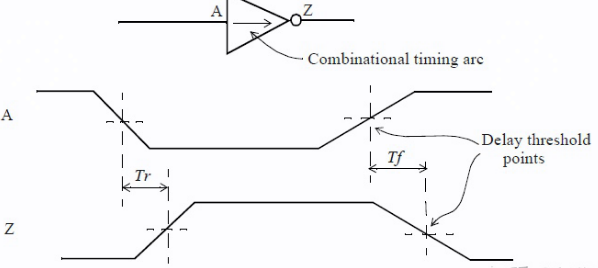

Propagation Delay

单元的传播延时(propagation delay)是由电平切换波形上的某些测量点定义的。这些阈值的单位是Vdd或电源的百分比,对于大多数标准单元库,通常将50%阈值用于计算延时。

这里的传播延时按照输出信号的 rise/fall 分为两种(不相等):

- output rise delay: 从输入信号到达下降沿阈值点开始,到输出信号到达上升沿阈值点结束的这段时间延迟

- output fall delay:与 output rise delay 相反

Slew

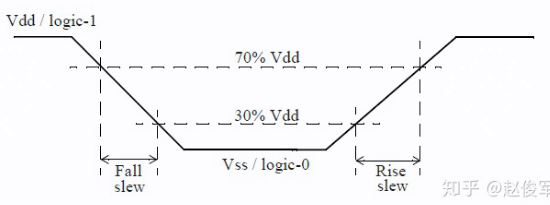

压摆率(slew rate)的定义是电压转换速率。在 STA 中,通常会根据电平转换的快慢来衡量上升波形或下降波形。压摆(slew)通常是根据转换时间(transition time)来定义的,转换时间是指信号在两个特定电平之间转换所需要的时间。请注意,转换时间实际上就是压摆率的倒数,因此转换时间越大,压摆率就越低,反之亦然。

一般使用指定的阈值电压来规定过渡时间计算的起点和终点

Slew rate 和 Slew 非同一件事。Slew 为 transition 而 Slew rate 为其倒数。

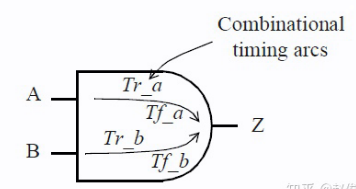

Timing Arc

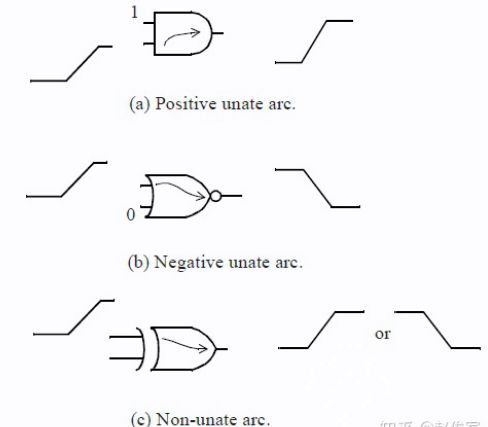

时序弧描述了信号在单元引脚之间传输的延迟以及信号的跳变情况。

- 像与门、或门、与非门、加法器这些组合逻辑单元,每个输入引脚到每个输出引脚都存在一条时序弧

- 而像触发器之类的时序逻辑单元除了有从时钟引脚到输出引脚的时序弧,还有相对于时钟引脚的数据引脚时序约束(timing constraint)

每个时序弧都具有特定的时序敏感(timing sense), 即输出如何针对输入的不同跳变类型而变化。在非单边(non-unate)时序弧中,仅仅从一个输入引脚的跳变方向是无法确定输出引脚电平将如何跳变的,还要取决于其他输入引脚的状态。

Timing Model

逻辑单元的时序模型(timing model)旨在为设计中的各种单元实例(instance)提供准确的时序信息。

- 每个时序弧都有时序模型

- 时序模型由详细电路仿真所得

对于一个 inverter 而言其存在两种延迟:分别为输出上升沿延时 T r T_{r} Tr 和输出下降沿延时 T f T_{f} Tf

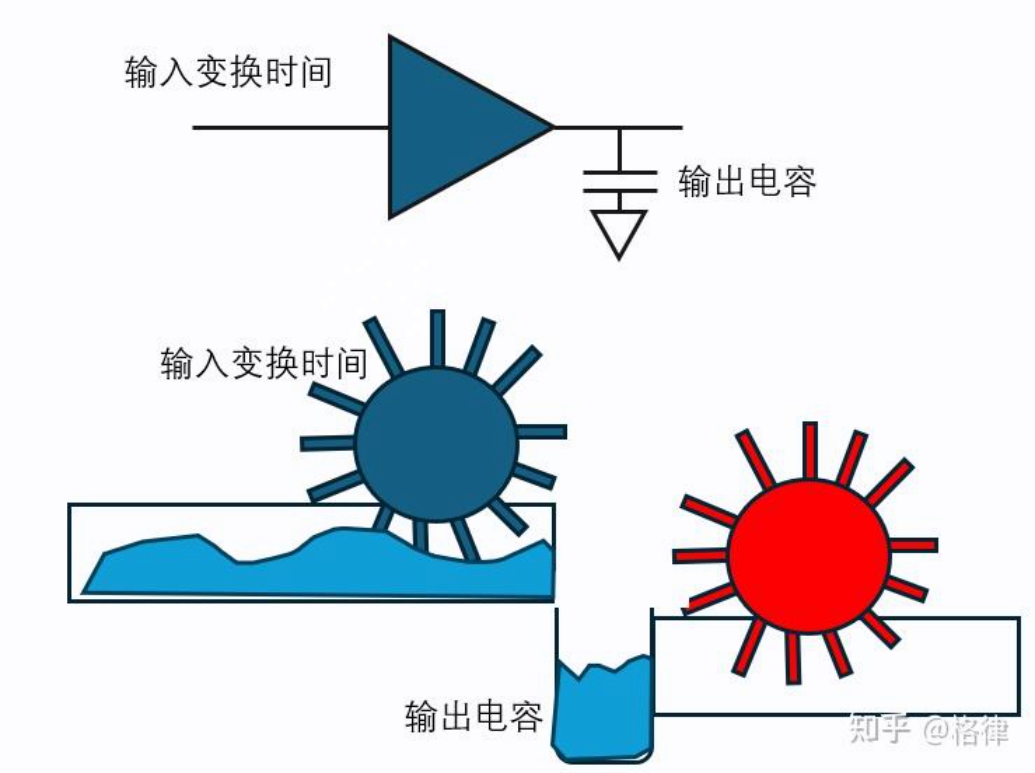

通过 inverter 的 delay and output transition 主要取决于:

- 输出负载,即反相器输出引脚上的电容负载

- 输入信号的过渡(transition)时间

- 晶体管版图设计:可忽略

一个逻辑单元的信号输入,如同在水槽上来了水流,水流首先推动蓝色水车运转(类似于输入变换时间),然后把水池(输出电容)灌满后,才能推动红色水车的运作(下一个逻辑单元)。

延迟值与负载电容有直接关系:负载电容越大,延迟越大。在大多数情况下,延迟也会随着输入信号过渡时间的增加而增加。PS: 非绝对

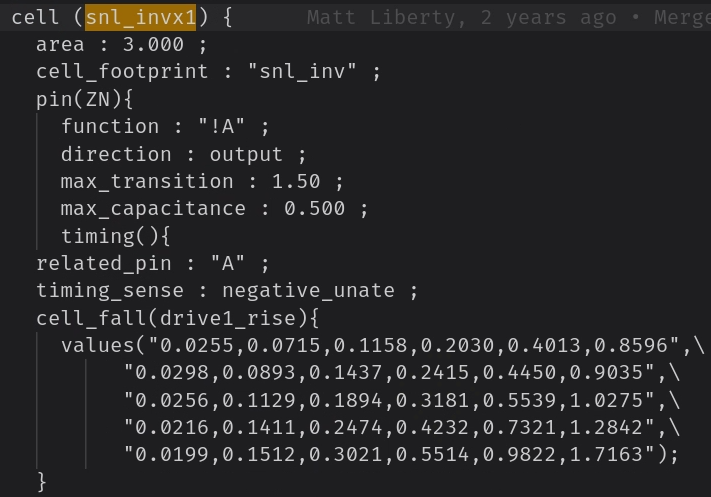

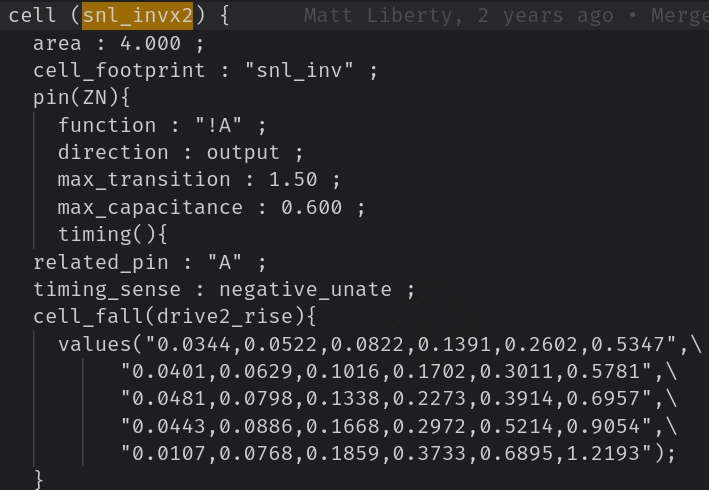

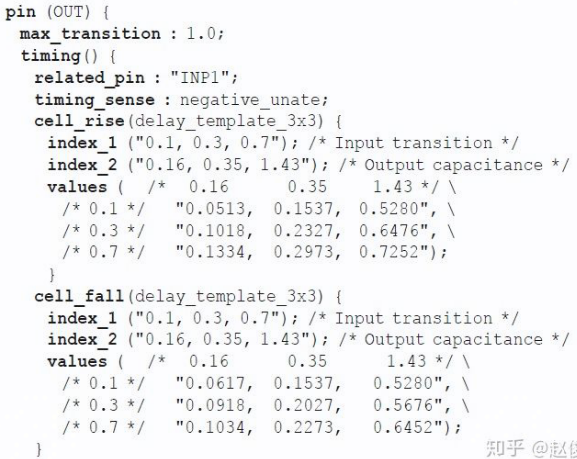

NLDM

逻辑单元的时序模型可以简单理解为以 input slew 和 output load 为参数的函数,但简单的线性时序模型在应用于亚微米技术时并不准确。因此,目前大多数单元库都使用更复杂的非线性延迟模型(non-linear delay model)

大多数单元库都包括表格模型(table model),用于为单元的各种时序弧指定延迟并进行时序检查。这些表格模型被称为 NLDM (Non-Linear Delay Model),可用于延迟、输出压摆计算或其他时序检查。表格模型中提供了:在单元输入引脚处输入过渡时间和输出引脚处输出负载电容的各种组合下通过单元的延迟。

根据延迟表,输入下降过渡时间为0.3ns且输出负载为0.16pf时,反相器的上升延迟为0.1018ns。由于输入的下降沿跳变导致反相器输出的上升沿跳变,因此当输入引脚发生下降沿跳变时,应该去查询cell_rise延迟表。注意,表格模型也可以是3维的,例如一个具有互补输出Q和QN的触发器。

NLDM模型不仅可以用于计算延迟,而且还可用于计算逻辑单元输出引脚的过渡时间,该时间同样由输入过渡时间和输出负载电容来表征。

所以通过 NLDM 模型可计算:

- Rise Delay

- Fall Delay

- Rise Slew

- Fall Slew

另外,如果没有表中对应索引,可通过插值计算结果。

Derate

skip it

压摆值(slew)基于的是在库中指定的测量阈值点,大多数上一代的库(0.25um或更旧的库)都使用10%和90%(对应波形的线性部分)作为压摆 (或称过渡时间)的测量阈值点。

随着技术的发展,实际波形最线性的部分通常在30%至70%之间。因此,大多数新一代时序库都将压摆测量阈值点指定为Vdd的30%和70%。但是,由于之前测得的过渡时间在10%至90%之间,因此在填充库时,通常将测得的30%至70%的过渡时间加倍,这由压摆降额系数(slew derate factor)指定,通常指定为0.5。压摆测量阈值点为30%和70%且压摆降额系数为0.5,等效于测量阈值点为10%和90%。

组合逻辑单元

对于两输入与门:共有四种 delay 以及四种 output transition

- 上升下降 * 两个输入引脚 = 4

- 而在 FPGA 中,每个逻辑单元的所有延时信息基本是固定的,所以每一种逻辑单元都分别拟合一个固定的延迟(例如LUT是0.1ns,DSP是1.3ns等)

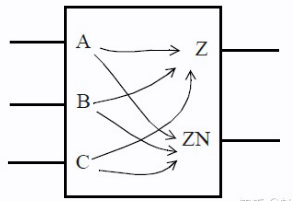

通用组合逻辑块

考虑以下这个具有三输入和两输出的通用组合逻辑块(General Combinational Block):

像这样的组合逻辑块可以具有多个时序弧。通常,从块的每个输入到每个输出都有一条时序弧。

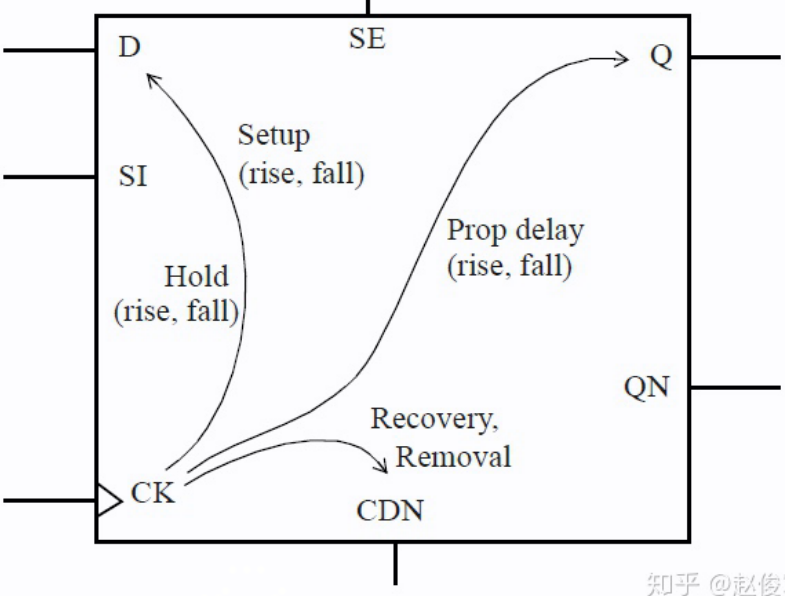

时序逻辑单元

时序逻辑单元的时序弧如下:

对于引脚 D, SI 和 SE 的同步输入信号,存在以下时序弧(both rise and fall):

- 建立时间检查时序弧

- 保持时间检查时序弧

对于引脚 Q 的同步输出信号,存在以下时序弧:

- CK to Q or QN Propagation delay arc

对于引脚 CDN 的异步输入信号,存在以下时序弧:

- 移除时间检查时序弧

- 恢复时间检查时序弧

此外,对于时钟引脚和异步引脚还存在

- 脉冲宽度时序检查

Setup and Hold

建立时间和保持时间的同步时序检查用于确保数据能够正确通过时序单元传播。这些时序检查可验证输入的数据在时钟有效沿上是否为确定的逻辑状态,并且在有效沿上将正确的数据锁存下来。

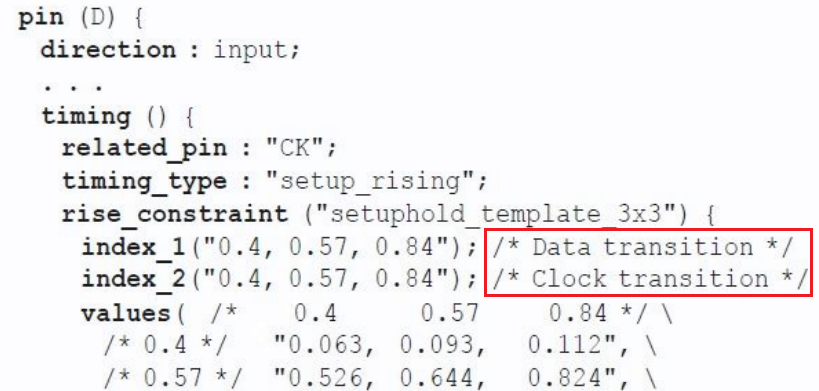

二维表格模型是根据约束引脚constrained_pin(D)和相关引脚related_pin(CK)处的过渡时间确定的。

setup and hold 详细内容在后文介绍。

异步时序检查

SKIP

状态相关的时序模型

SKIP

输入和输出之间的时序弧取决于模块中其他引脚的逻辑状态

黑盒的接口时序模型

SKIP

高级时序模型

SKIP

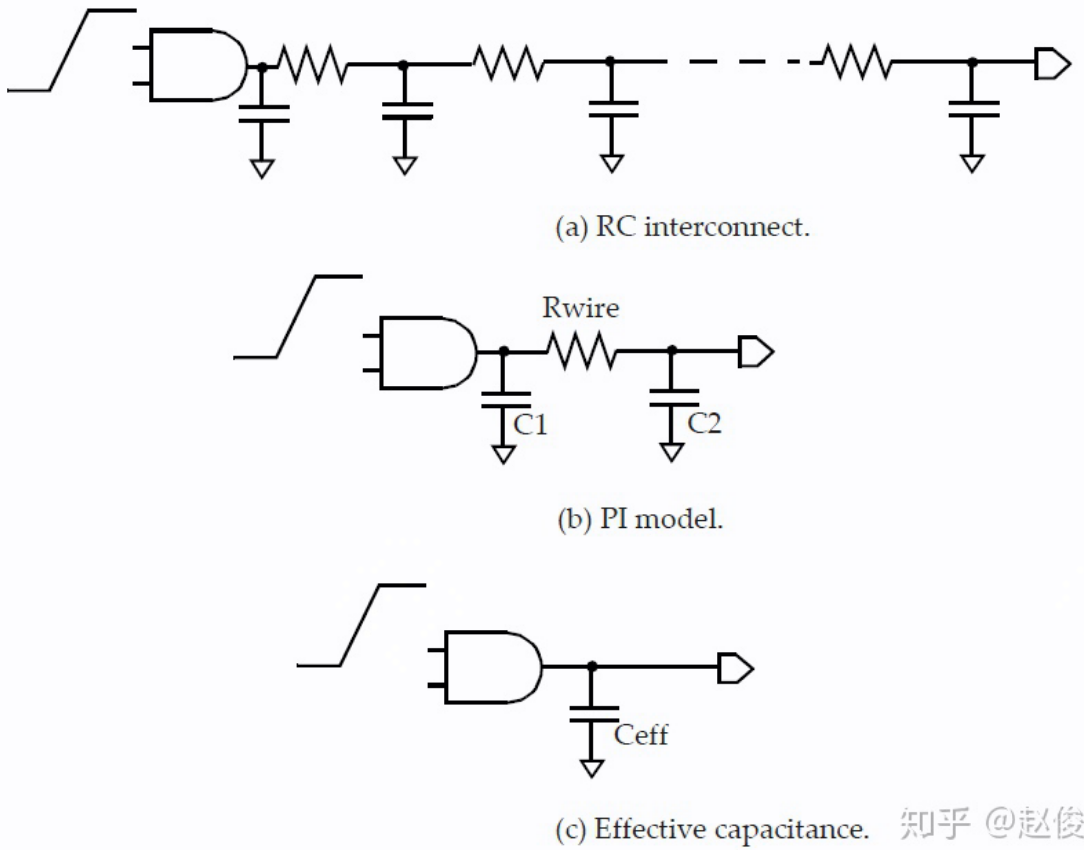

非线性延迟模型(NLDM)这类的时序模型是基于输出负载电容和输入过渡时间来表示通过时序弧的延迟的。实际上,单元输出的负载不仅包括电容还应当包括互连电阻(interconnect resistance)。

由于NLDM方法假设输出负载为纯电容,因此互连电阻成为了一个问题。即使互连电阻不为零,但当互连电阻的影响较小时,仍使用了这些NLDM模型。在互连电阻存在的情况下,延迟的计算方法通过在单元的输出端获得等效的有效电容(effective capacitance)来改进NLDM模型。延迟计算工具中使用的“有效”电容法获得的等效电容可保证单元输出延迟与具有RC互连的单元输出延迟相同。

由于 NLDM 无法很好地处理互连电阻带来的误差,所以提出了如 CCS (Composite Current Source) 等更高级的时序模型。

Clock

Skew

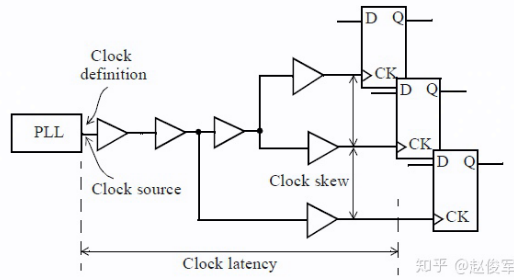

偏斜(skew)是指两个或多个信号(数据或者时钟)之间的时序之差。例如,如果一个时钟树(clock tree)有500个终点, 并且有50ps的偏斜,则意味着最长时钟路径和最短时钟路径之间的延迟差为50ps。

时钟树的起点通常是定义时钟的节点,时钟树的终点通常是同步元件(例如触发器)的时钟引脚。时钟延迟(clock latency: Source + Insertion)是指从时钟源到终点所花费的总时间,时钟偏斜(clock skew)是指到达不同时钟树终点的时间差。

理想时钟树是假定时钟源具有无限驱动力,时钟可以无延迟地驱动无限个终点。另外,假定时钟树中存在的任何逻辑单元都具有零延迟(zero delay)。在逻辑设计的早期阶段,STA通常使用理想的时钟树来执行,因此分析的重点是数据路径 (data path)。通过 set_clock_latency 可显示指定时钟树延迟。

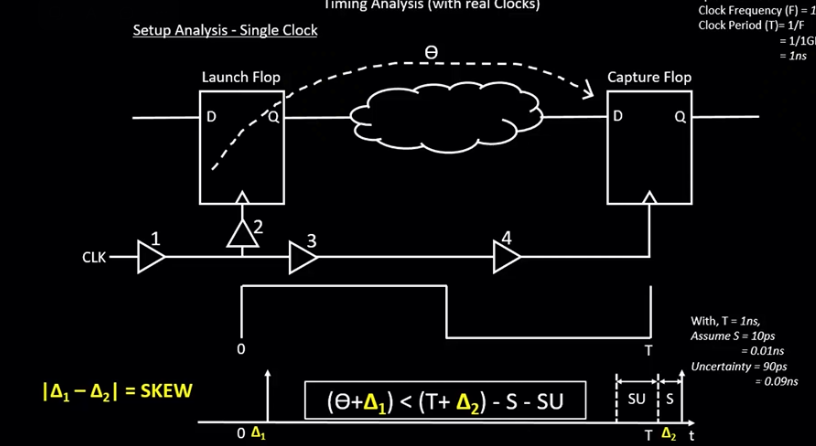

Uncertainty

set_clock_uncertainty 命令为时钟沿的出现指定了一个窗口。时钟边沿时序的不确定性将考虑多个因素,例如时钟周期抖动 (jitter) 和用于时序验证的额外裕量 (slack)。实际上是不存在理想时钟的,所有时钟都具有一定的抖动量,并且在指定时钟不确定度时应包括时钟周期抖动。

在时钟树被实现(implement)之前,时钟不确定度还必须包括预期的时钟偏斜。而保持时间检查不需要将时钟抖动包括在内,因此通常为保持时间检查指定较小的时钟不确定度。

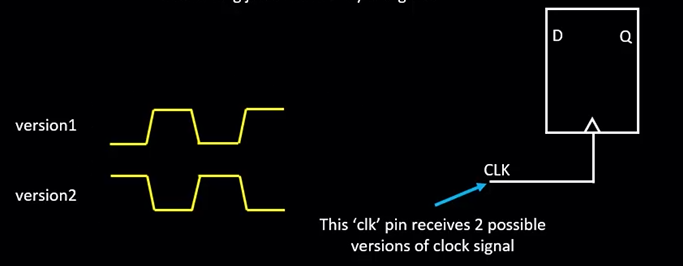

实际中的时钟信号

实际的时钟信号包括上升沿和下降沿:

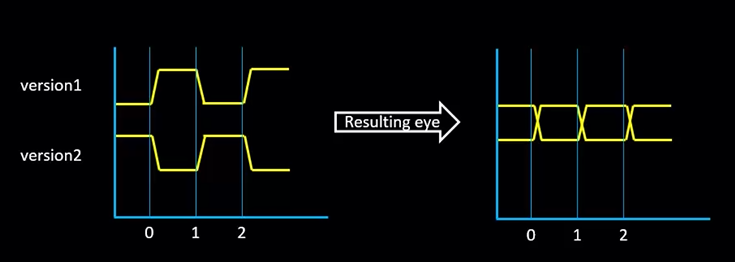

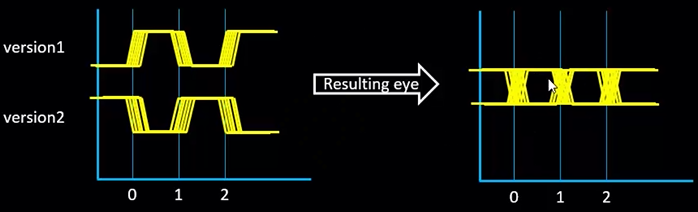

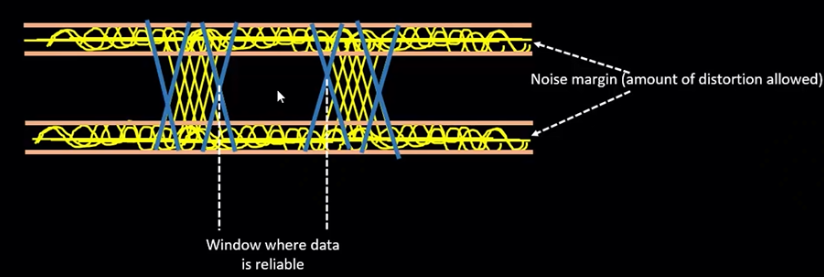

将两种时钟信号结合得到理想情况下的眼图,此时为只有 transition 的理想时钟:

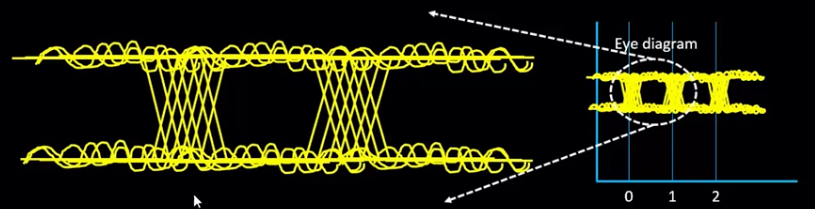

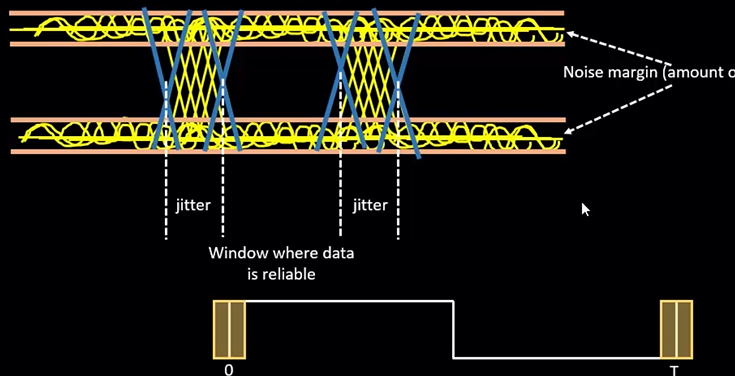

但实际上时钟信号存在不同的到达时间(jitter),此时的眼图为:

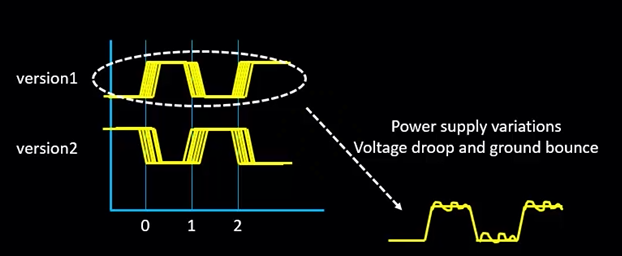

此外,时钟还会因为 Power Supply variations cause voltage drop and ground bounce.

最终得到实际情况下的时钟信号:

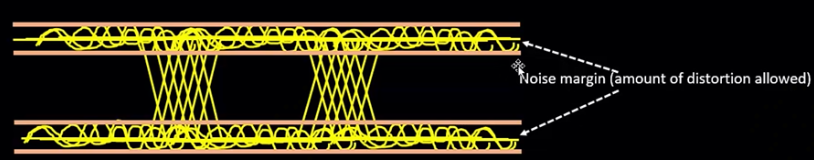

针对电平波动,定义 noise margin, 允许一定失真:

时钟信号无抖动区域称为 window where data is reliable:

而时钟信号存在抖动的区域称为 jitter: Jitter has to be accounted for in the timing reports. We model this using one more parameter called Uncertainty.

Example : Uncertainty = 90ps = 0.09ns

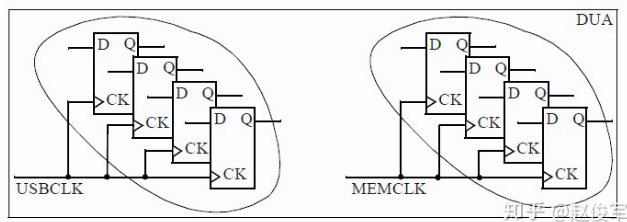

Clock Domain

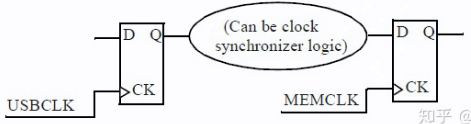

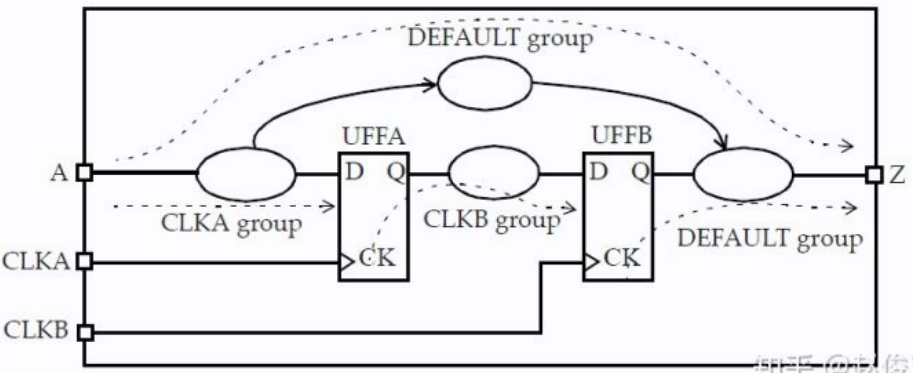

一个时钟通常驱动许多触发器,由同一时钟驱动的一组触发器称为其时钟域(clock domain)。下图即存在两个时钟域:

需要关注一个问题:两个时钟域是相关的还是彼此独立的?答案取决于是否存在一条从一个时钟域开始并在另一时钟域结束的数据路径,如果没有这样的路径,我们可以肯定地说这两个时钟域彼此独立,这意味着没有时序路径从一个时钟域开始而在另一时钟域结束。

若存在跨时钟域的数据路径(如下图所示),则必须确定这些路径是否为真实(real)路径:例如一个两倍频时钟驱动的触发器发起数据,再由一倍频时钟驱动的触发器捕获数据,这条路径就是一条真实路径。

而伪路径(false path)的一个例子是设计人员将时钟同步器(clock synchronizer)逻辑明确放置在两个时钟域之间。在这种情况下,即使好像存在从一个时钟域到下一时钟域的时序路径,但这也不是真实的时序路径,因为数据没有被约束要在一个时钟周期之内通过同步器逻辑传播。这样的路径称为伪路径(不是真实的),因为是由时钟同步器来确保数据正确地从一个时钟域传递到另一个时钟域。

- false path belongs to timing exceptions, so skip it.

- 在设计中,有些路径是不可能存在的,或者不可能发生的,这种路径称为伪路径。伪路径通常发生在异步电路以及跨时钟域;或者电路内部逻辑复杂,推导后发现其实是常量,不会发生变化

实际出现跨时钟域的情况往往是双向的,即从USBCLK时钟域到MEMCLK时钟域,以及从 MEMCLK时钟域到USBCLK时钟域,这两种情况都需要在STA中正确理解和处理。

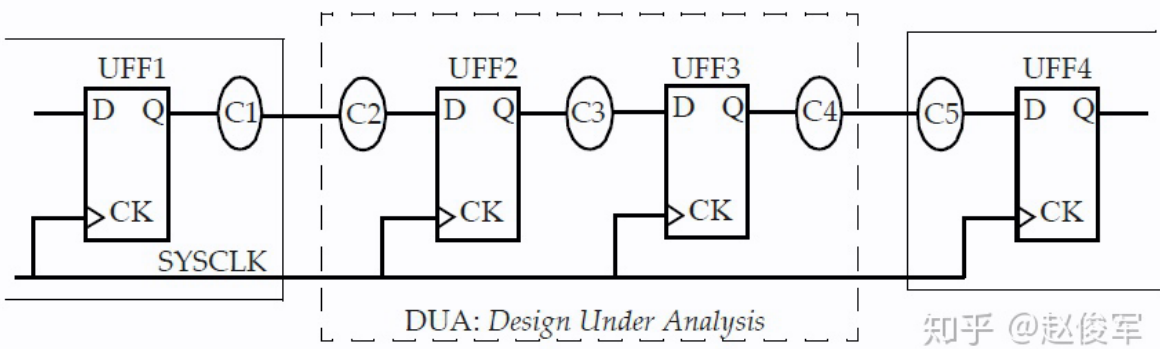

SDC

正确的约束对于分析STA结果很重要,只有准确指定设计环境,STA分析才能够识别出设计中的所有时序问题。STA的准备工作包括设置时钟、指定IO时序特性以及指定伪路径和多周期路径。

为了对这种设计执行STA,需要指定触发器的时钟、以及进入设计和退出设计的所有路径的时序约束。

指定时钟

要定义时钟,我们需要提供以下信息:

- 时钟源(Clock source):它可以是设计的端口,也可以是设计内部单元的引脚(通常是时钟生成逻辑的一部分)。

- 周期(Period):时钟的周期。

- 占空比(Duty cycle):高电平持续时间(正相位)和低电平持续时间(负相位)。

- 边沿时间(Edge times):上升沿和下降沿的时刻。

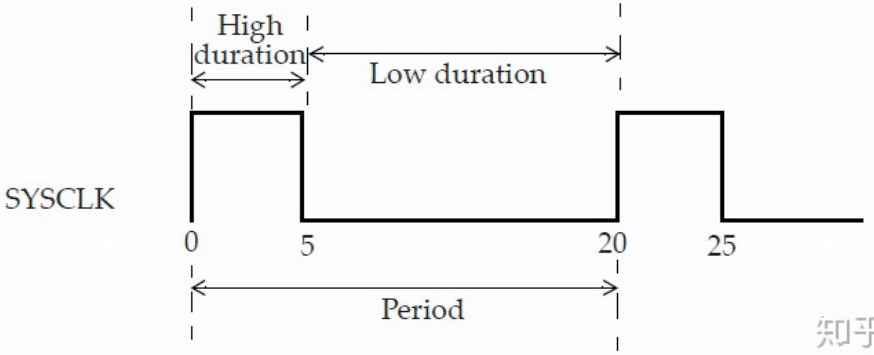

创建时钟的例子:create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK];该时钟名为SYSCLK,并在端口SCLK上定义。SYSCLK的周期指定为20个单位,如果未指定,默认时间单位为纳秒(通常,时间单位会在技术库中进行指定)。waveform中的第一个自变量指定出现上升沿的时刻,第二个自变量指定出现下降沿的时刻。

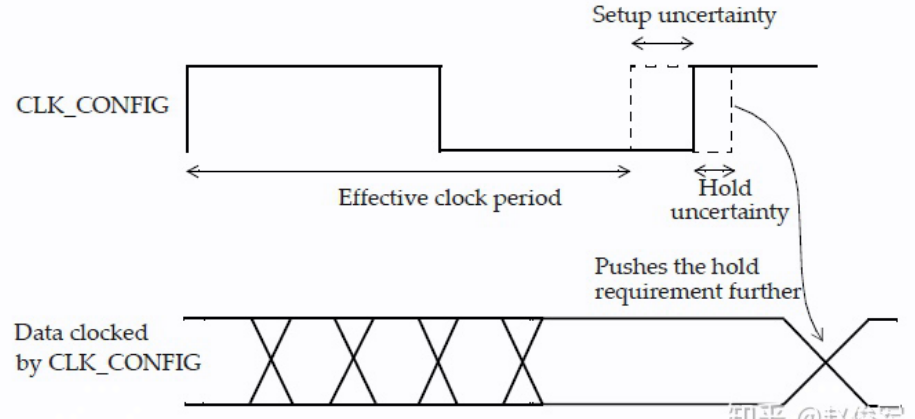

时钟不确定度

可以使用 set_clock_uncertainty 约束来指定时钟周期的时序不确定度(uncertainty),该不确定度可用于对可能会减少有效时钟周期的各种因素进行建模。这些因素可能是jitter以及可能需要在时序分析中考虑的任何其它悲观度。

set_clock_uncertainty -setup 0.2 [get_clocks CLK_CONFIG];注意,建立时间检查的时钟不确定度将减少可用的有效时钟周期。对于保持时间检查,时钟不确定度将用作需要满足的额外时序裕量。

时钟延迟

可用以下命令设置时钟延迟,如 set_clock_latency 1.8 -rise [get_clocks MAIN_CLK]

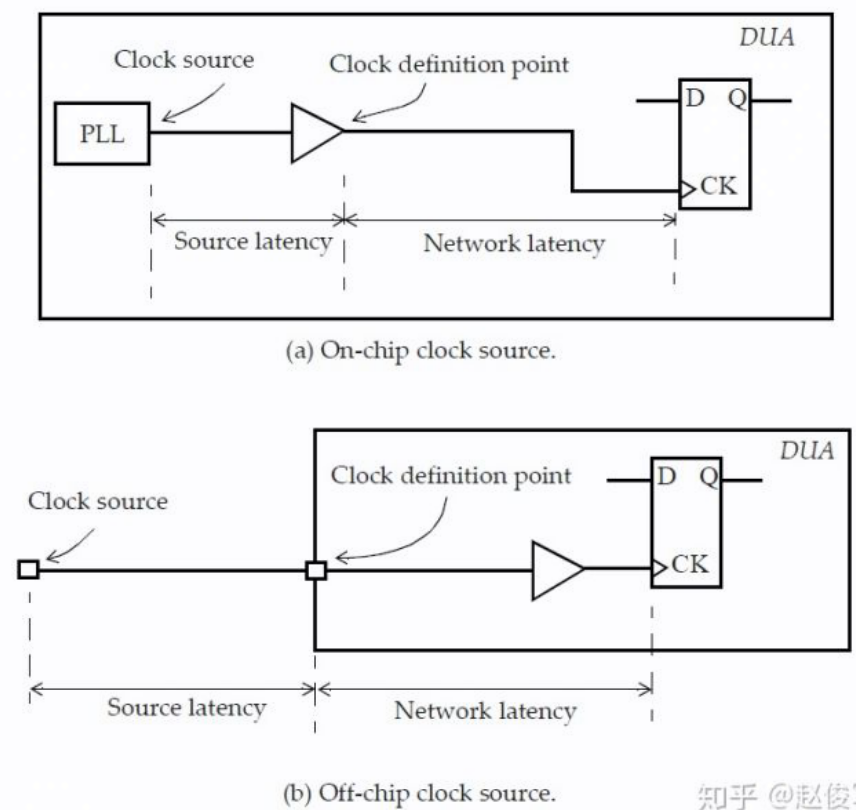

时钟延迟有两种类型:网络延迟(network latency)和源延迟(source latency):触发器时钟引脚上的总时钟延迟是源延迟和网络延迟之和。在时钟树综合完成后,从时钟源到触发器时钟引脚的总时钟延迟是源延迟加上时钟树从时钟定义点到触发器的实际延迟。

- 网络延迟是指从时钟定义点 (create_clock) 到触发器时钟引脚的延迟。

- CTS 后忽略

- 源延迟也称为插入延迟(insertion delay):是指从时钟源到时钟定义点的延迟, 源延迟可能代表片上或片外延迟

- CTS 后保留

源延迟和网络延迟之间的一个重要区别是:一旦为设计建立了时钟树,就可以忽略网络延迟 (假设指定了 set_propagated_clock 命令)。

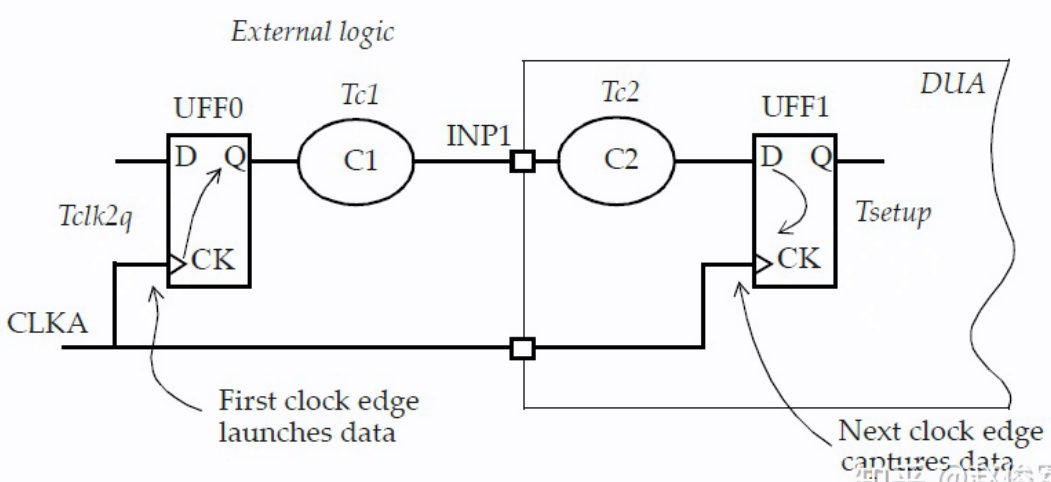

约束输入路径

触发器UFF0在设计的外部,并向设计内部的触发器UFF1提供数据。数据通过输入端口INP1连接两个触发器。

CLKA的时钟定义指定了时钟周期,这是两个触发器UFF0和UFF1之间可用的总时间。外部逻辑所需的时间为Tclk2q(数据发起触发器UFF0的CK至Q延迟)加上Tc1(通过外部组合逻辑的延迟) ,因此输入引脚INP1上的延迟定义指定了Tclk2q加上Tc1的外部延迟。

以下是输入延迟的约束 (可分别定义 minmax):

set Tclk2q 0.9set Tc1 0.6set_input_delay -clock CLKA -max [ expr Tclk2q + Tc1] [ get_ports INP1]

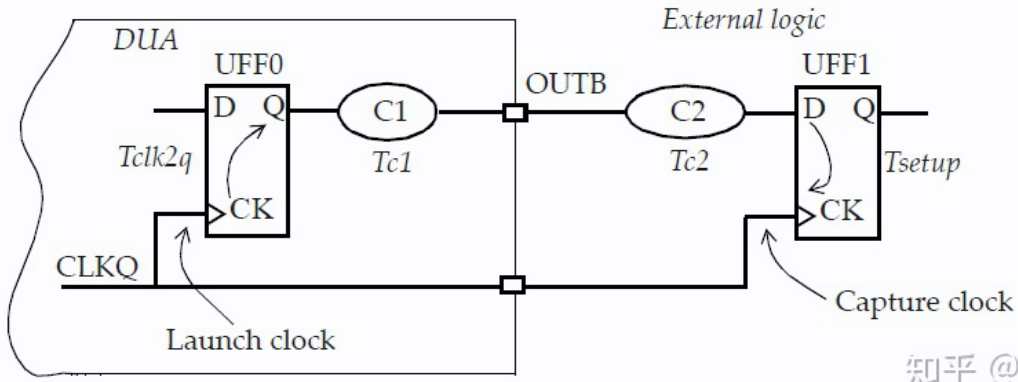

约束输出路径

约束输出路径与约束输入路径类似,可通过命令 set_output_delay 来指定外部延迟:

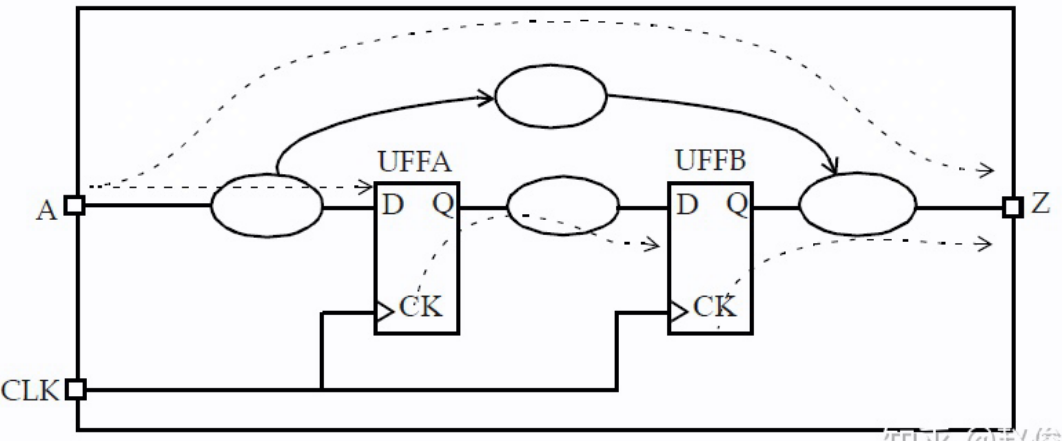

时序路径组

设计中的时序路径可以视为路径的集合,每个路径都有一个起点和一个终点。

时序路径可以根据与路径终点相关的时钟分类为不同时序路径组(path groups)。因此,每个时钟都有一组与之相关的时序路径。还有一个默认时序路径组,其中包括了所有非时钟(异步)路径。

外部属性建模

尽管 create_clock 、set_input_delay 和 set_output_delay 足以约束设计中用于执行时序分析的所有路径,但这些并不足以获取该模块IO引脚上的准确时序。

对于输入,需要在输入端口处指定压摆:

set_driveset_driving_cellset_input_transition

对于输出,需要指定输出引脚的负载电容:

set_load

驱动强度建模

总之,设计人员需要指定输入端的压摆值来确定输入路径中第一个单元的延迟。在没有该约束的情况下,将假设为理想过渡值 0,这显然是不现实的。

set_drive 和 set_driving_cell 约束用于对驱动模块输入端口的外部单元的驱动强度进行建模。在没有这些约束的默认情况下,假定所有输入都具有无限的驱动强度,即输入引脚的过渡时间为0

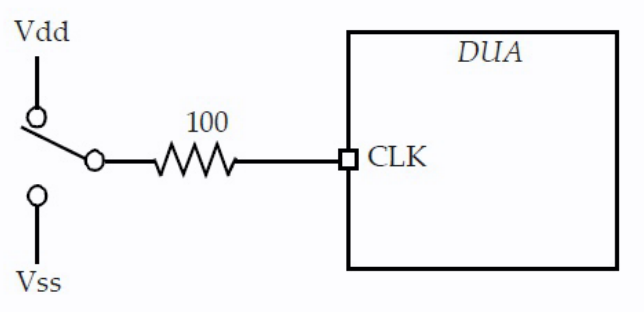

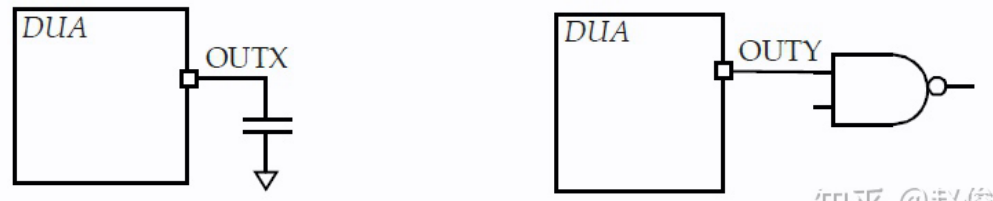

set_drive 明确指定了DUA输入引脚上的驱动电阻值,该电阻值越小,驱动强度越高,电阻值为0表示无限的驱动强度。输入端口的驱动强度用于计算第一个单元的过渡时间。指定的驱动强度还可用于计算在任何RC互连情况下从输入端口到第一个单元的延迟值

- 延迟值 = (驱动强度 * 网络负载) + 互连线延迟

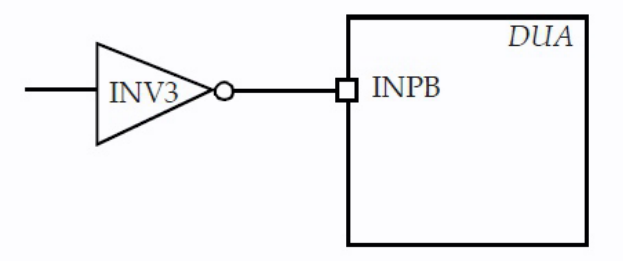

set_driving_cell 约束提供了一种更方便,更准确的方法来描述端口的驱动能力。 set_driving_cell 可用于指定驱动输入端口的单元类型。但由于输入端口上的电容性负载而导致驱动单元的增量延迟被视作为输入上的附加延迟被包括在内

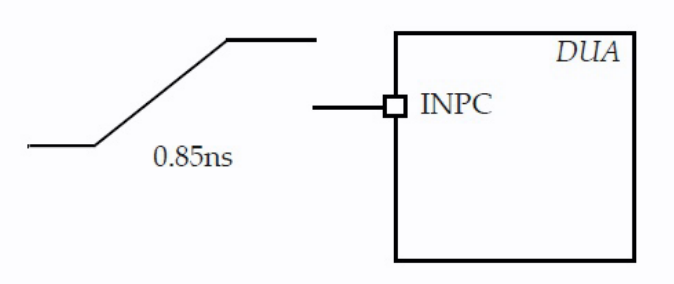

作为上述方法的替代方法, set_input_transition 约束提供了一种在输入端口表示过渡时间的便捷方法,并且可以指定参考时钟

负载电容建模

指定输出上的负载很重要,因为该值会影响驱动输出的单元的延迟。在没有该约束的情况下,将假定负载为0,这显然是不现实的。

set_load 约束在输出端口上设置了电容性负载,以模拟由输出端口驱动的外部负载。默认情况下,端口上的电容性负载为0。可以将负载显式地指定为电容值或某个单元的输入引脚电容。

DRV

STA中两个常用的设计规则是最大过渡时间-max_transition和最大电容-max_capacitance。这些规则将会检查设计中的所有端口和引脚是否满足过渡时间和电容的规定约束。

此外,还可以为设计指定其他设计规则检查,比如: set_max_fanout (指定设计中所有引脚的扇出约束) 以及 set_max_area (用于设计)。但是,这些检查适用于综合(synthesis)而非STA。

Delay Calculation

延迟计算基本概念

由上文可知,每个单元的输入引脚都存在引脚电容,所以每条 net 都将具有容性负载,其值为所有 fanout 的引脚负载电容及互连线的寄生电容之和。

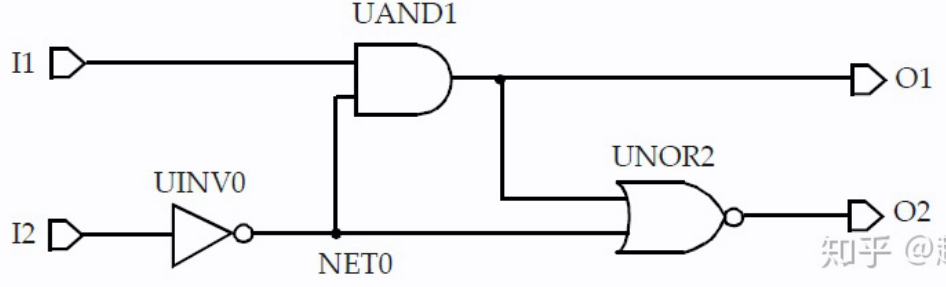

考虑如下设计:

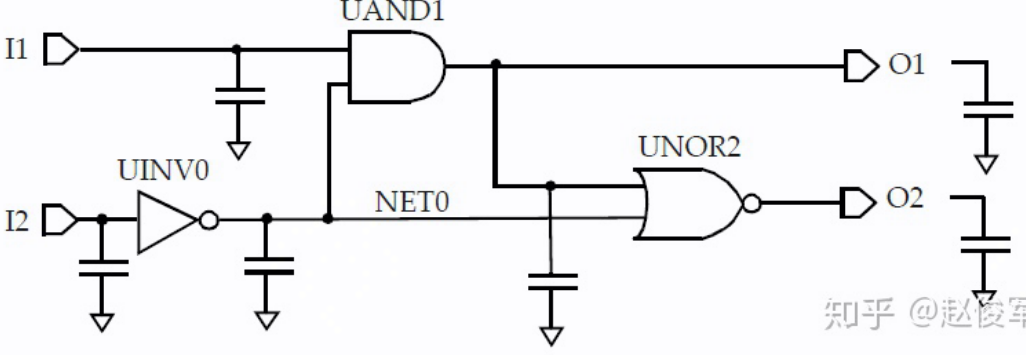

对于 NET0, 在不考虑互联寄生的情况下,其电容等于 UAND1 和 UNOR2 的输入引脚电容之和。由此,可将上图等价为:

输出 O1 的负载电容等价于输出端口负载(未指定,可通过 set_load 指定)加上 UNOR2 输入引脚负载电容(已在库中指定),所以此时只要为输入 I1 指定压摆(或 set_drive),即可获得单元 UAND1 相对于该 input transition 的 propagation delay and output transition(知道了上一级的 output transition, 则又可以得到下一级单元的 input transition).

由于多输入单元存在不同输入到输出的多条 timing arc, 所以 output transition 的值由 slew merge 结果来决定。

有效电容计算单元延迟

当单元输出端的负载包含互连电阻时,NLDM模型不可直接使用。因此,采用“有效”电容法来处理电阻的影响。

有效电容法试图找到一个可以用作等效负载的电容,以使原始设计与具有等效电容负载的设计在单元输出的时序方面表现一致。这个等效电容被称为有效电容(effective capacitance)

即在实际情况下,互连寄生不能忽略电阻的影响,此时可将 RC 互连建模为更精简的 PI model。由于 NLDM 只接受电容,所以将 RC 计算为一个等效的 C e f f C_{eff} Ceff ,进而可以继续使用 NLDM 查表得到单元延迟。那如何计算得到这个 C e f f C_{eff} C

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

421

421

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?