Verilog 代码设计完成后,还需要进行重要的步骤,即逻辑功能仿真。仿真激励文件称之为 testbench,放在各设计模块的顶层,以便对模块进行系统性的例化调用进行仿真。

毫不夸张的说,对于稍微复杂的 Verilog 设计,如果不进行仿真,即便是经验丰富的老手,99.9999% 以上的设计都不会正常的工作。不能说仿真比设计更加的重要,但是一般来说,仿真花费的时间会比设计花费的时间要多。有时候,考虑到各种应用场景,testbench 的编写也会比 Verilog 设计更加的复杂。所以,数字电路行业会具体划分设计工程师和验证工程师。

下面,对 testbench 做一个简单的学习。

testbench 结构划分

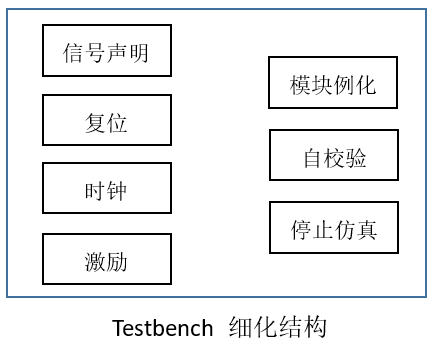

testbench 一般结构如下:

其实 testbench 最基本的结构包括信号声明、激励和模块例化。

根据设计的复杂度,需要引入时钟和复位部分。当然更为复杂的设计,激励部分也会更加复杂。根据自己的验证需求,选择是否需要自校验和停止仿真部分。

当然,复位和时钟产生部分,也可以看做激励,所以它们都可以在一个语句块中实现。也可以拿自校验的结果,作为结束仿真的条件。

实际仿真时,可以根据自己的个人习惯来编写 testbench,这里只是做一份个人的总结。

testbench 仿真举例

前面的章节中,已经写过很多的 testbench。其实它们的结构也都大致相同。

下面,我们举一个数据拼接的简单例子,对 testbench 再做一个具体的分析。

一个 2bit 数据拼接成 8bit 数据的功能模块描述如下:

实例

module data_consolidation

(

input clk ,

input rstn ,

input [1:0] din , //data in

input din_en ,

output [7:0] dout ,

output dout_en //data out

);

// data shift and counter

reg [7:0] data_r ;

reg [1:0] state_cnt ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

state_cnt <= 'b0 ;

data_r <= 'b0 ;

end

else if (din_en) begin

state_cnt <= state_cnt + 1'b1 ; //数据计数

data_r <= {data_r[5:0], din} ; //数据拼接

end

else begin

state_cnt <= 'b0 ;

end

end

assign dout = data_r ;

// data output en

reg dout_en_r ;

always @(posedge clk or negedge rstn) begin

if (!rstn) begin

dout_en_r <= 'b0 ;

end

本文详细介绍了Verilog代码设计后的逻辑功能仿真过程,强调了testbench的重要性,包括其基本结构、时钟复位处理、激励部分编写以及一个数据拼接模块的testbench实例分析。

本文详细介绍了Verilog代码设计后的逻辑功能仿真过程,强调了testbench的重要性,包括其基本结构、时钟复位处理、激励部分编写以及一个数据拼接模块的testbench实例分析。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

514

514

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?