SDRAM(Synchronous Dynamic Random Access Memery)同步动态随机存储器

同步:Sdram的工作时钟与FPGA的时钟频率一致,SDRAM均以此时钟作为基准,同步接口;

动态:电容(存储电荷,但电容会放电,需要不断刷新);

随机:给一个地址,找到存储单元进行读写;

特点:存储空间大,功耗低;发展到五代产品SDRAM、DDR SDRAM、DDR2、DDR3、DDR4

**第一代是单端时钟信号,且数据只在上升沿采样;后面几代均为差分时钟抗干扰,双沿采样;**控制逻辑比较复杂;

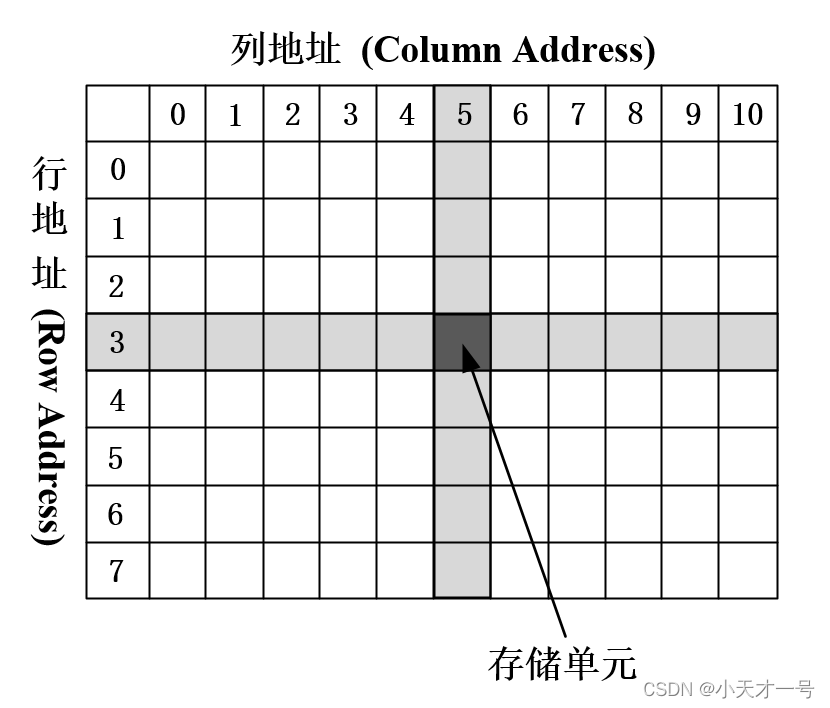

SDRAM数据存取原理:**内部存储阵列

N个存储单元构成一个存储阵列,N=行地址列地址=一个逻辑Bank;SDRAM中会有好几个Bank;

在对SDRAM进行数据存取时,先确定L-Bank地址,定位到指定逻辑Bank,再依次确定行地址和列地址,选中存储单元,进行操作,一次只能对一个Bank中的一个存储单元进行操作。

SDRAM存储容量计算:

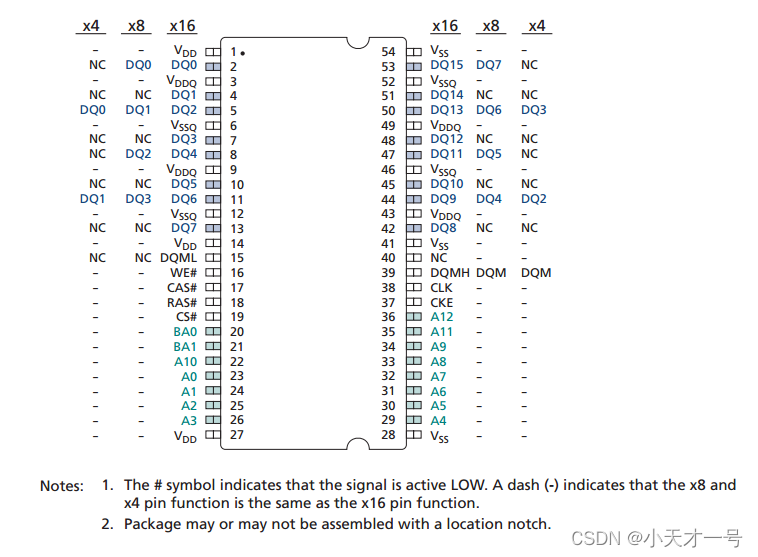

例如镁光的:4Meg164Banks

4Meg:(单个L-BANK包含的存储单元个数)(行地址[12:0]列地址[8:0])

16:(位宽16bit)

4Banks:(4个Bank)

即:**4M16*4=256Mbits**

芯片引脚

CLK 系统时钟: SDRAM 由系统时钟驱动,所有 SDRAM 输入信号都在时钟上升沿采样,同时 CLK 还递增内部突发计

数器并控制输出寄存器。

CKE 时钟使能:屏蔽系统时钟,冻结当前操作,高电平有效,信号有效时,所有信号才能被正确送入 SDRAM。

CS#片选信号:屏蔽和使能所有输入输出端口, CLK、CKE、 DQM 除外, 低电平有效。为高电平时,屏蔽所有命令,但已经突发的读/写操作不受影响。

CAS# 列选通信号:低电平有效,为低电平时, A[8:0]输入的为列地址

RAS# 行选通信号:低电平有效,为低电平时, A[12:0]输入的行地址

WE#写使能信号,低电平有效,为低电平时,使能写操作和预充电。

DQM[1:0] 数据掩码: DQML(H),低(高)字节掩码,若信号为高电平,在下一个时钟周期的时钟上升沿,数据总线的低(高)

字节为高阻态。

BA[1:0] L-Bank 地址:选择不同的逻辑 Bank 进行相关数据操作。

DQ[15:0] 16Bit Inout 数据总线:数据输入/输出复用引脚:

8601

8601

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?