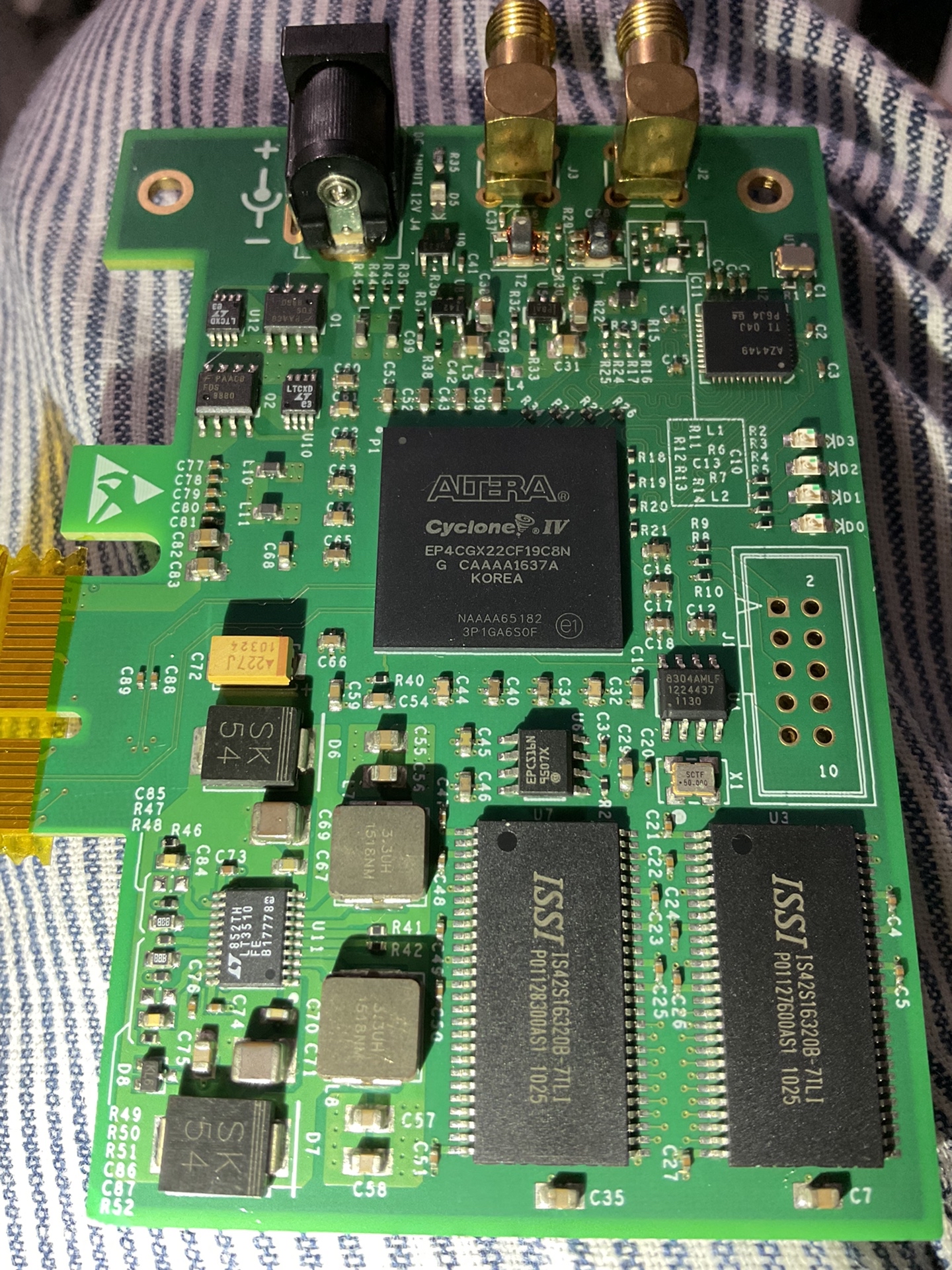

altera fpga ep4cgx22cf19c8,有原理图,PCB图纸,源代码,PCIe二次开发驱动和代码等。

ID:313000681436451614

小明子555

altera fpga ep4cgx22cf19c8,作为一款高性能的可编程逻辑器件,具备丰富的功能和广泛的应用领域。在本文中,我们将重点介绍该型号的特点以及相关的原理图、PCB图纸、源代码、PCIe二次开发驱动和代码等内容。

首先,让我们来了解altera fpga ep4cgx22cf19c8的主要特点。该款FPGA芯片具备较大的逻辑容量和高性能,能够实现复杂的硬件逻辑设计。它采用了先进的40纳米工艺技术,具备低功耗和高速度的特点。同时,它支持多种接口标准,如PCIe、DDR3、USB等,为设计者提供了丰富的扩展和应用方式。

对于硬件设计师来说,原理图和PCB图纸是不可或缺的工具。altera fpga ep4cgx22cf19c8附带了详细的原理图和PCB图纸,方便设计师进行电路连接和布局设计。原理图是硬件设计的基础,在电路实现的过程中起到了关键作用。PCB图纸则是将原理图转化为实际可制造的PCB板的设计文件,通过布局和布线的设计,实现电路的可靠性和稳定性。

此外,源代码是进行FPGA开发的重要组成部分。altera fpga ep4cgx22cf19c8提供了丰富的源代码,包括Verilog和VHDL等硬件描述语言。这些源代码可以用于实现各种逻辑功能,如数据处理、通信接口、算法实现等。通过编写源代码,设计者可以根据具体需求进行定制化的设计和开发。

PCIe二次开发驱动和代码是针对altera fpga ep4cgx22cf19c8与其他设备进行通信的重要内容。PCIe(Peripheral Component Interconnect Express)是一种高速串行接口标准,广泛用于计算机之间的数据传输。通过二次开发驱动和代码,设计者可以实现与其他设备之间的高速数据传输和通信控制。这为系统集成和扩展提供了便利,并且保证了系统的稳定性和可靠性。

综上所述,altera fpga ep4cgx22cf19c8作为一款高性能的可编程逻辑器件,具备强大的功能和广泛的应用领域。通过原理图、PCB图纸、源代码以及PCIe二次开发驱动和代码等工具,设计者可以灵活地进行硬件设计和开发。它的应用范围涵盖了多个领域,如通信、嵌入式系统、图像处理等。未来,随着技术的不断进步,altera fpga ep4cgx22cf19c8将会继续发挥重要作用,为各行各业的创新和发展提供支持。

注:本文所述为作者个人观点,不代表任何厂商或组织的观点。

相关的代码,程序地址如下:http://fansik.cn/681436451614.html

209

209

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?