更新说明:2025/10/13

Altium Designer 报错集

Warnings:Zero hole size multi-layer pad(s) detected

解决Zero hole size multi-layer pad(s) detected 报警错误

检测到的报警错零孔径多层垫,也就是所谓焊盘无孔。

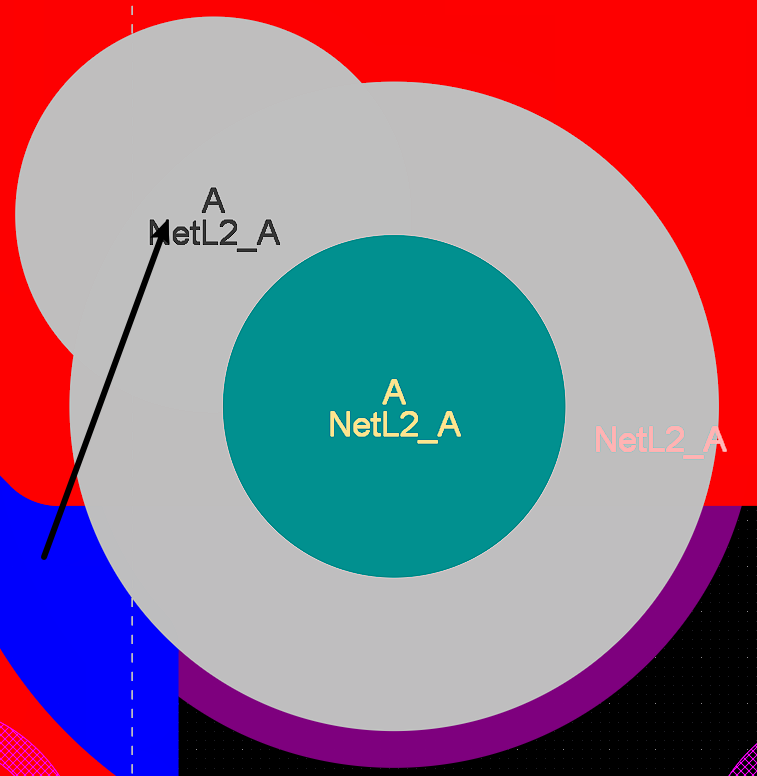

文字描述多少有些抽象,下图提供一张大图高清方便理解

严谨一点并不是靠肉眼确认即可,因为时间久了下次再打开设计文档你还是要再检查确认一次。

既然如此那就解决这个发现问题的人就可以了。

能把这篇内容看到这里,说明你和我一样在认真探索这个领域。

如果这些干货对你有实际帮助,希望你能点赞让更多人看到,收藏下来当作自己的知识库。

解决方法如下:

在 Altium Designer 中出现 "Extra Pin U1-3 in Normal of part U1" 警告,

原理图元器件 U1 中存在多余的引脚(Pin),而该引脚在对应的封装(Footprint)中没有匹配的焊盘(Pad),导致原理图与封装信息不一致。

1. 定位多余引脚的位置

- 双击警告信息中的 "U1-3",软件会自动定位到原理图中 U1 的第 3 号引脚

- 确认该引脚是否为设计所需:

- 若为误添加的引脚(如绘制元器件时多放的引脚),直接删除即可

- 若为实际需要的引脚,但封装中缺少对应焊盘,则需要修改封装

2. 删除多余的无效引脚

- 在原理图中选中 U1,右键选择 "Edit Pins" 进入引脚编辑界面

- 在引脚列表中找到编号为 "3" 的引脚,选中后点击 "Remove" 删除

- 保存修改,重新编译项目(Project → Compile PCB Project),警告通常会消失

3. 若引脚为必要引脚,需补充封装焊盘

如果该引脚是元器件实际需要的(如芯片 datasheet 中明确存在第 3 号引脚),但封装中缺少对应焊盘,则需要修改封装:

- 打开该元器件对应的封装库(.PcbLib)

- 找到 U1 使用的封装,在封装中添加一个编号为 "3" 的焊盘(Pad),确保焊盘编号与原理图引脚编号完全一致

- 保存封装库后,回到原理图,执行 "Update PCB Document" 将修改同步到 PCB

- 重新编译项目,确认警告消除

4. 检查元器件库的完整性

- 若该元器件是从库中调用的标准件,可能是库文件本身存在错误

- 建议重新从官方库或可靠来源调用元器件,或直接重新绘制原理图元器件(确保引脚数量、编号与 datasheet 一致)

- 重新关联正确的封装后,执行编译和更新操作

图文并茂实操解决问题如下:

1. 回到 PCB 文件,点击右下角【Panels】,之后在弹出的菜单中勾选【PCB】。

2.在【PCB】面板中,选择【Nets】勾选警告中的网络,如:【GPIO04】,可以看到警告中的详细信息。

3.尝试修改【Template】

4.此时可以看到出现警告 Pad。

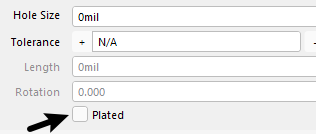

5.进行修改调整。取消下图黑色箭头处即可。

今天的内容到这里就结束啦~如果这篇文章帮你解决了某个小疑问,或者让你有了新启发,别忘了点赞 + 收藏,方便之后反复查看。

也特别期待在评论区看到你的想法 —— 你对这个话题还有哪些补充?或者下一期想看什么内容?想听听你的实践经验,比如你是怎么应用这个方法的?

咱们评论区见!评论区分享你的故事,一起进步~

————————————————

版权声明:本文为优快云博主「硬件王哪跑」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

8145

8145

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?