FPGA的NIOS-II开发入门

本次实验,我将学习 Quartus-II 、Platform Designer、Nios-II SBT 的基本操作;初步了解 SOPC 的开发流程,基本掌握 Nios-II 软核的定制方法;掌握 Nios-II 软件的开发流程,软件的基本调试方法。

并完成以下实验:

- 流水灯显示;

- 串口循环输出“Hello Nios-II"

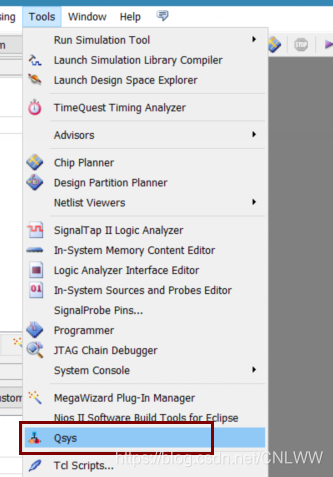

首先,点开Tools,打开Qsys (Platform Designer)

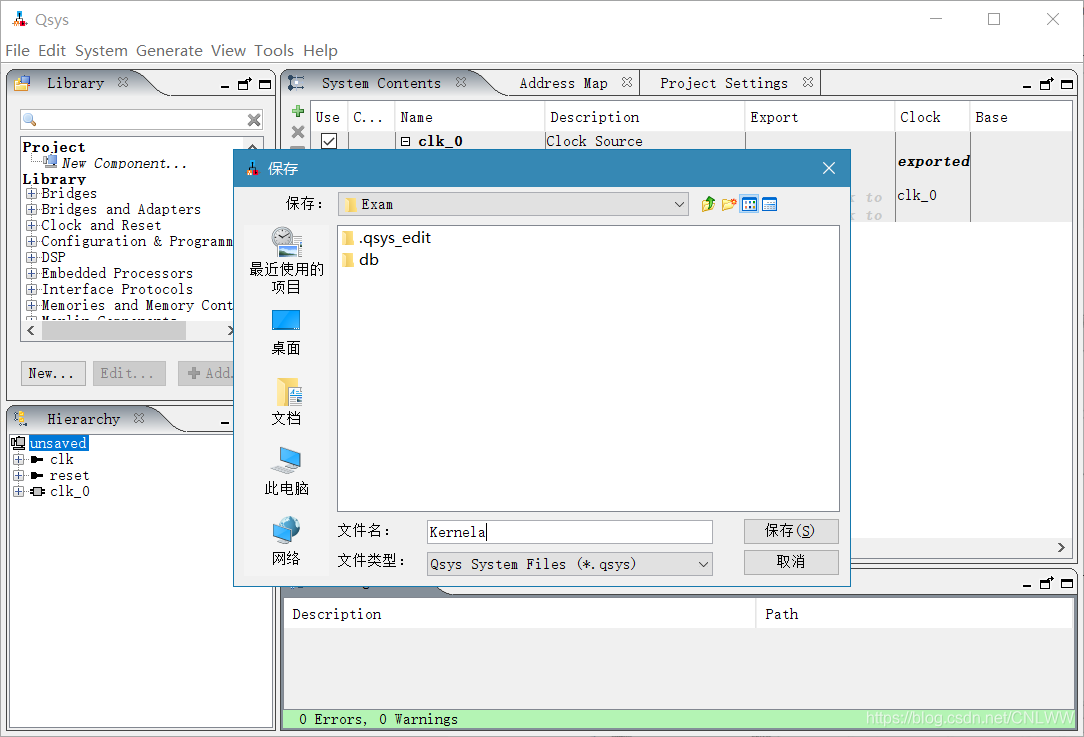

点击File->save,保存名为"Kernel"的文件

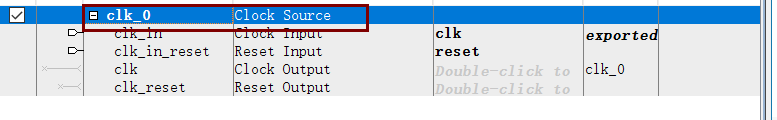

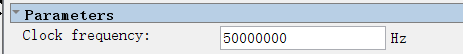

退出,双击clk_0,将时钟设置为50M(50000000)

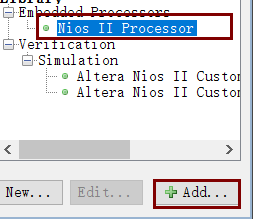

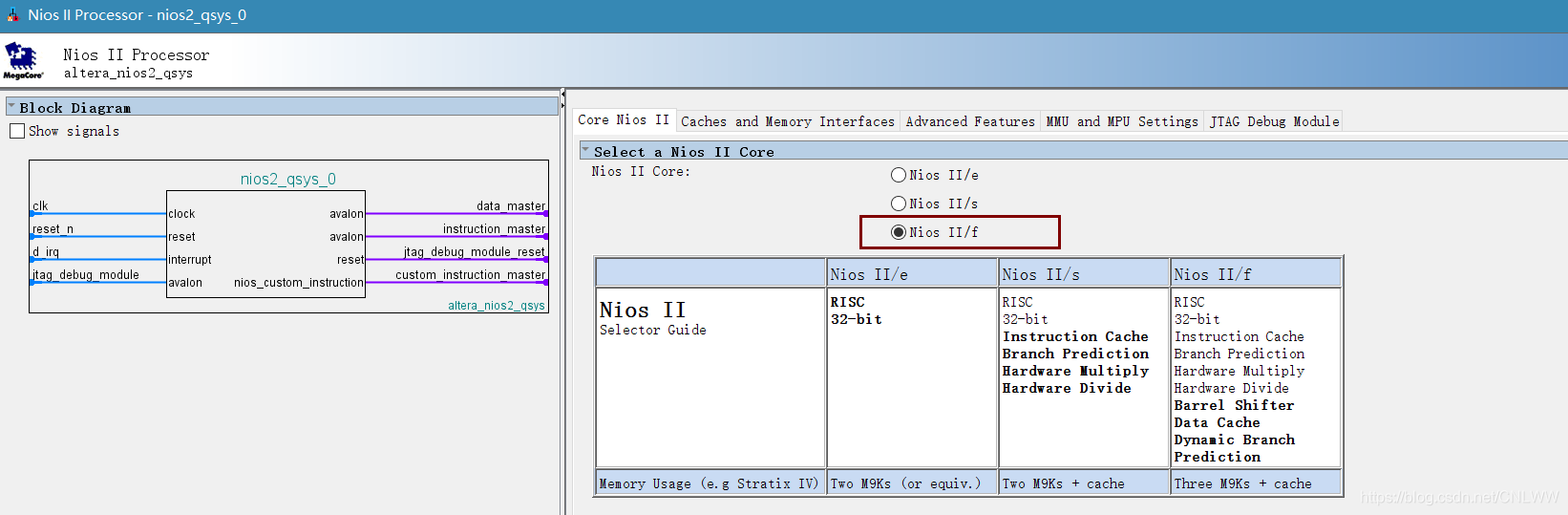

在左侧工具栏输入Nios,找到 Processor,点击add

Nios Core 选择f,点击其他属性,均为默认设置,点击Finish.

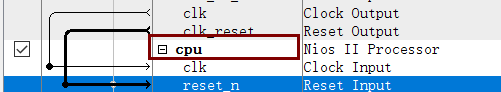

然后将添加进的nios2改名为cpu,再将其clk和reset_n与时钟的clk和reset相连接

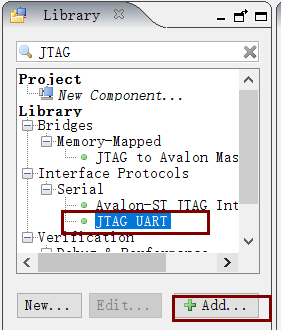

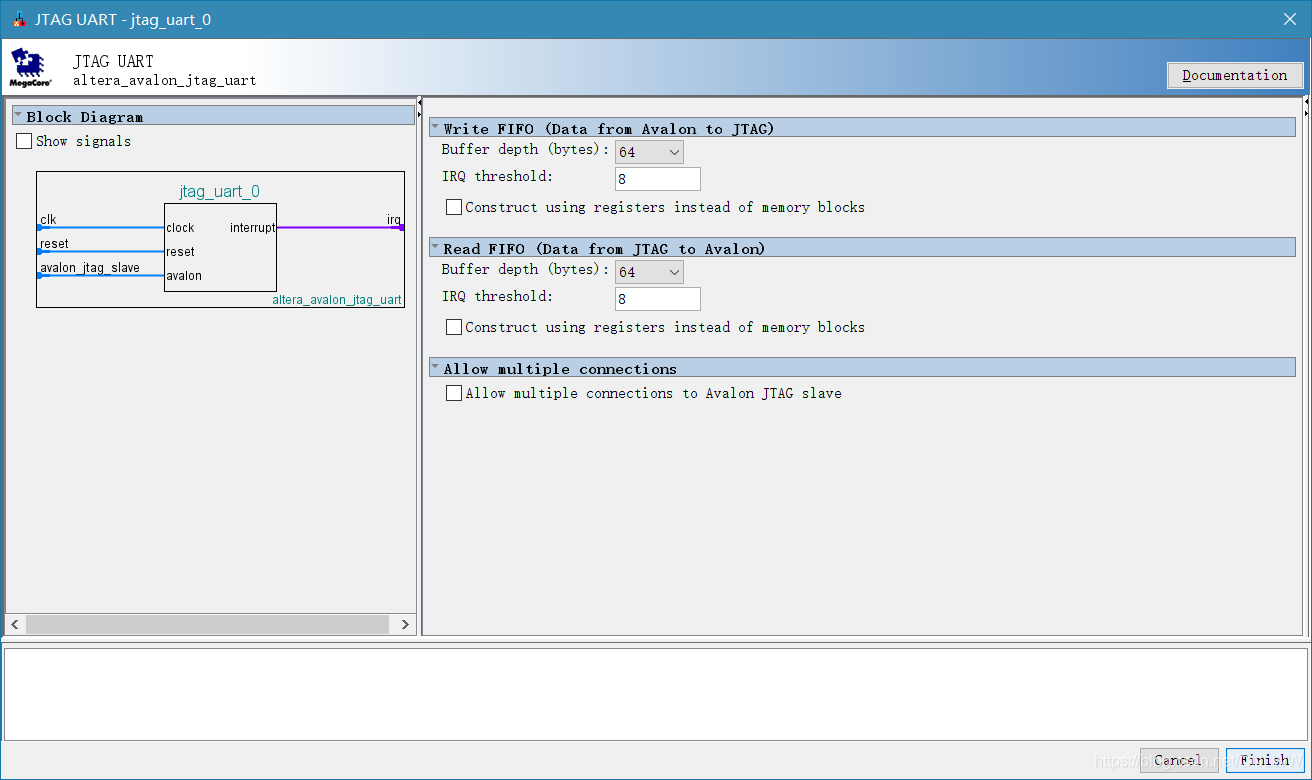

添加一个JTAG UART接口,通过工具栏直接搜索可以找到

保持默认选项,点击完成

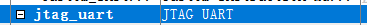

顺便重命名一下,将末尾的“_0”去掉

clk

本文档介绍了使用Quartus-II、Platform Designer和Nios-II Software Build Tools (SBT)进行FPGA开发的入门过程。通过实践,学习了SOPC的开发流程,定制Nios-II软核,以及软件开发和调试方法。实验内容包括实现流水灯显示和串口输出‘Hello Nios-II’。详细步骤涉及Nios软核配置、JTAG UART接口、On-Chip Memory、PIO设置等,最终完成硬件设计并成功编译。

本文档介绍了使用Quartus-II、Platform Designer和Nios-II Software Build Tools (SBT)进行FPGA开发的入门过程。通过实践,学习了SOPC的开发流程,定制Nios-II软核,以及软件开发和调试方法。实验内容包括实现流水灯显示和串口输出‘Hello Nios-II’。详细步骤涉及Nios软核配置、JTAG UART接口、On-Chip Memory、PIO设置等,最终完成硬件设计并成功编译。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

245

245

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?