https://mpbeta.youkuaiyun.com/mp_blog/creation/editor/148794551

**摘要 **

> 本文系统阐述了差分放大电路的核心工作原理与应用价值。从基本电路拓扑结构入手,详细推导差模增益、共模增益及关键性能指标共模抑制比(CMRR)的计算公式。深入剖析了理想差分放大电路特性与现实电路中的误差来源(如元件失配、温度漂移)。结合 Multisim/PSpice 电路仿真验证理论分析,探讨了实际设计中电阻匹配、电流源改进等性能优化策略。论文最后分析了差分电路在现代模拟集成电路、传感器信号调理及高速通信系统中的典型应用场景,指出其作为“抑制共模噪声基石”的不可替代作用。仿真结果与理论分析高度吻合,对工程设计具有重要参考价值。

**1. 引言**

* **1.1 研究背景与意义 **

* 真实世界中信号的困扰:无处不在的共模噪声(电源噪声、地线干扰、环境电磁干扰)。

* 解决核心痛点:差分放大电路的核心价值——抑制共模噪声,放大微弱差模信号。

* 广泛应用场景:生物电信号采集(ECG、EEG)、精密传感器(应变片、电桥)、高速通信接收端、运算放大器输入级等。

* 本文研究目的:从基础到深入,透彻理解原理,掌握设计优化方法。

* **1.2 差分放大电路概述与发展 (约200字)**

* 定义:同时放大两输入信号电压差值(差模信号),抑制两输入信号电压平均值(共模信号)的电路。

* 基本结构:对称性(晶体管/BJT/JFET/MOSFET对或精密匹配电阻)。

* 简要发展:从分立元件到现代IC(如运放)输入级的核心地位。

* **1.3 论文主要内容框架 (约100字)**

* 清晰列出后续章节安排。

**2. 差分放大电路基本结构与工作原理 **

* **2.1 经典双端输入-双端输出结构图解**

* 使用匹配晶体管对 (BJT/MOSFET) + 发射极/源极恒流源 + 集电极/漏极负载电阻的标准电路图。

* 清晰标注输入信号 (`V_in1`, `V_in2`), 输出信号 (`V_out1`, `V_out2`), 参考地 (`GND`)。

* **2.2 关键信号分解与定义**

* 差模输入信号 (`V_id`): `V_id = V_in1 - V_in2`

* 共模输入信号 (`V_ic`): `V_ic = (V_in1 + V_in2) / 2`

* 双端输出差分信号 (`V_od`): `V_od = V_out1 - V_out2`

* 单端输出电压 (`V_o1`, `V_o2`).

* **2.3 差模增益 (`A_d`) 的深入推导与物理意义**

* **小信号模型分析:** 构建半边电路等效模型(差模等效电路)。

* **公式推导:** 详细推导 `A_d = V_od / V_id = ? ` (对于BJT常见:`A_d ≈ - (β * R_c) / (2 * (r_π + (β+1)*R_e))` 或简化 `≈ - g_m * R_c`, 取决于电路细节)。 强调公式中各参数物理意义 (跨导`g_m`, 集电极电阻 `R_c`)。

* **物理意义:** `A_d` 反映了电路放大**有用**信号的能力。

* **2.4 共模增益 (`A_c`) 的深入推导与物理意义**

* **小信号模型分析:** 构建共模等效电路(注意电流源理想特性)。

* **公式推导:** 详细推导理想恒流源下 `A_c ≈ 0`。 推导更实际的有限输出阻抗 `r_o` 下 `A_c = V_oc / V_ic ≈ - R_c / (2 * r_o)`。 强调公式中各参数物理意义。

* **物理意义:** `A_c` 反映了电路抑制**无用/干扰**信号的能力。理想情况下为0。

* **2.5 核心性能指标:共模抑制比 (`CMRR`)**

* **定义:** `CMRR = |A_d| / |A_c|` (无量纲) 或 `CMRR(dB) = 20 * log10(|A_d / A_c|)`。

* **推导与解读:** 用前述 `A_d` 和 `A_c` 表达式代入推导 CMRR表达式。强调 `CMRR` **定量表征了抑制共模干扰的能力**,越大越好。

* **物理意义:** CMRR 100dB 意味着共模干扰被抑制了 100dB,差模信号放大了 `A_d`倍。

**3. 理想特性与现实非理想因素分析 **

* **3.1 理想差分放大电路特性总结**

* 极高的差模增益 (`A_d`)。

* 接近无穷大的输入阻抗。

* 接近零的输出阻抗(对后续电路友好)。

* 理论上为零的共模增益 (`A_c = 0`),即无穷大的 `CMRR`。

* 良好的线性度和对称性。

* **3.2 现实电路中的非理想因素与误差来源 (重点详述)**

* **3.2.1 元件失配 (致命影响CMRR)**

* 晶体管参数失配(`β/V_be` (BJT), `V_th/K'` (MOS)等)。

* **电阻失配:** 负载电阻 `R_c1` ≠ `R_c2`,发射极/源极电阻失配(若有)。定量分析失配度 ΔR/R 对 CMRR 的劣化程度(公式推导或引用)。

* **影响:** `A_c` 显著增大,`CMRR` 大幅度下降,导致输出含有共模干扰成分。

* **3.2.2 电流源非理想性**

* 有限输出阻抗 (`r_o`):这是实际 CMRR 受限的最主要原因之一。定性定量分析:`r_o` 越小,`A_c` 越大,`CMRR` 越小。

* 电流源本身随温度/电压的漂移:影响工作点稳定性和共模抑制能力。

* **3.2.3 温度漂移 (温漂)**

* BJT的`V_be`、`β`随温度变化。

* MOS管的`V_th`、`μ_n`等参数随温度变化。

* 电阻阻值温漂。

* **影响:** 导致静态工作点漂移、增益漂移,特别地是引入**输入失调电压(`V_os`)** 及其温漂 (`dV_os/dT`)。解释 `V_os` 的定义(使输出归零所需的差分输入补偿电压),强调它对直流精度的影响。

* **3.2.4 频率响应限制**

* 晶体管结电容、寄生电容。

* **影响:** `A_d`, `A_c` (尤其 `A_c`) 在高频时衰减速率不同,导致**CMRR随频率升高而急剧下降**。需关注**CMRR带宽**。提供典型曲线说明。

**4. 差分放大电路性能优化设计策略 **

* **4.1 提升 CMRR 的核心技术**

* **精密电阻匹配技术:** 选用高精度低TCR电阻、使用集成电阻阵列(如IC中的匹配对)、激光修调技术。强调匹配的相对重要性(ΔR/R)。

* **改进型恒流源设计:**

* 基础镜像电流源(BJT/MOS)。

* 威尔逊电流源(显著提高输出阻抗`r_o`)。

* 改进型威尔逊电流源、级联(Cascode)电流源(进一步显著提升`r_o`,有效改善CMRR)。

* 比较不同电流源的输出阻抗和温漂特性,分析其对CMRR的提升效果。**公式佐证 `A_c ∝ 1/(2*r_o)`**。

* **4.2 抑制温漂与失调**

* **输入级器件匹配设计:** IC工艺中精细匹配。

* **采用差分对主动负载技术 (如BJT的达林顿或MOS的电流镜有源负载):** 提高增益同时优化性能。

* **外部调零电路:** 简单分立电路可加入失调调零电位器(说明原理与应用限制)。

* **4.3 共模反馈与平衡技术 (概念性介绍)**

* 在某些高精度IC中使用的技术,用于进一步稳定共模工作点。

* **4.4 电路布局与布线考量**

* 对称性布局原则。

* 接地策略(“纯净”地线)。

* 电源退耦电容的重要性。抑制电磁耦合。

差分放大电路的基本结构

差分放大电路通常采用对称结构,由两个匹配的晶体管(BJT或MOSFET)构成。电路包含双端输入和双端输出,发射极或源极连接恒流源,集电极或漏极连接负载电阻。输入信号通过V_in1和V_in2接入,输出信号从V_out1和V_out2获取,参考地为GND。

信号分解与定义

| 差模输入信号V_id定义为两输入信号的差值: | [ V_{id} = V_{in1} - V_{in2} ] |

| 共模输入信号V_ic定义为两输入信号的平均值: | [ V_{ic} = \frac{V_{in1} + V_{in2}}{2} ] |

| 双端输出差分信号V_od为两输出信号的差值 | [ V_{od} = V_{out1} - V_{out2} ] |

| 单端输出电压为V_o1或V_o2 |

差模增益A_d的推导

通过小信号模型分析,构建差模等效电路。对于BJT差分对,差模增益A_d的表达式为: [ A_d = \frac{V_{od}}{V_{id}} \approx -\frac{\beta R_c}{2(r_\pi + (\beta + 1)R_e)} ] 或简化为: [ A_d \approx -g_m R_c ] 其中,g_m为跨导,R_c为集电极电阻。

共模增益A_c的推导

在理想恒流源情况下,共模增益A_c趋近于零。实际电路中,考虑电流源输出阻抗r_o,共模增益为: [ A_c = \frac{V_{oc}}{V_{ic}} \approx -\frac{R_c}{2 r_o} ]

共模抑制比CMRR

CMRR定义为差模增益与共模增益的比值: [ CMRR = \frac{|A_d|}{|A_c|} ] 或以分贝表示: [ CMRR(dB) = 20 \log_{10}\left(\frac{|A_d|}{|A_c|}\right) ]

理想特性与实际误差

理想差分放大电路具有高差模增益、零共模增益和无穷大CMRR。实际电路中,非理想因素包括元件失配、电流源非理想性、温度漂移和频率响应限制。这些因素会导致CMRR下降,共模干扰未被完全抑制。

性能优化策略

提升CMRR的关键技术包括精密电阻匹配和改进型恒流源设计。威尔逊电流源和级联电流源能显著提高输出阻抗r_o,从而减小A_c。抑制温漂的方法包括输入级器件匹配和采用差分对主动负载技术。电路布局需注重对称性和接地策略。

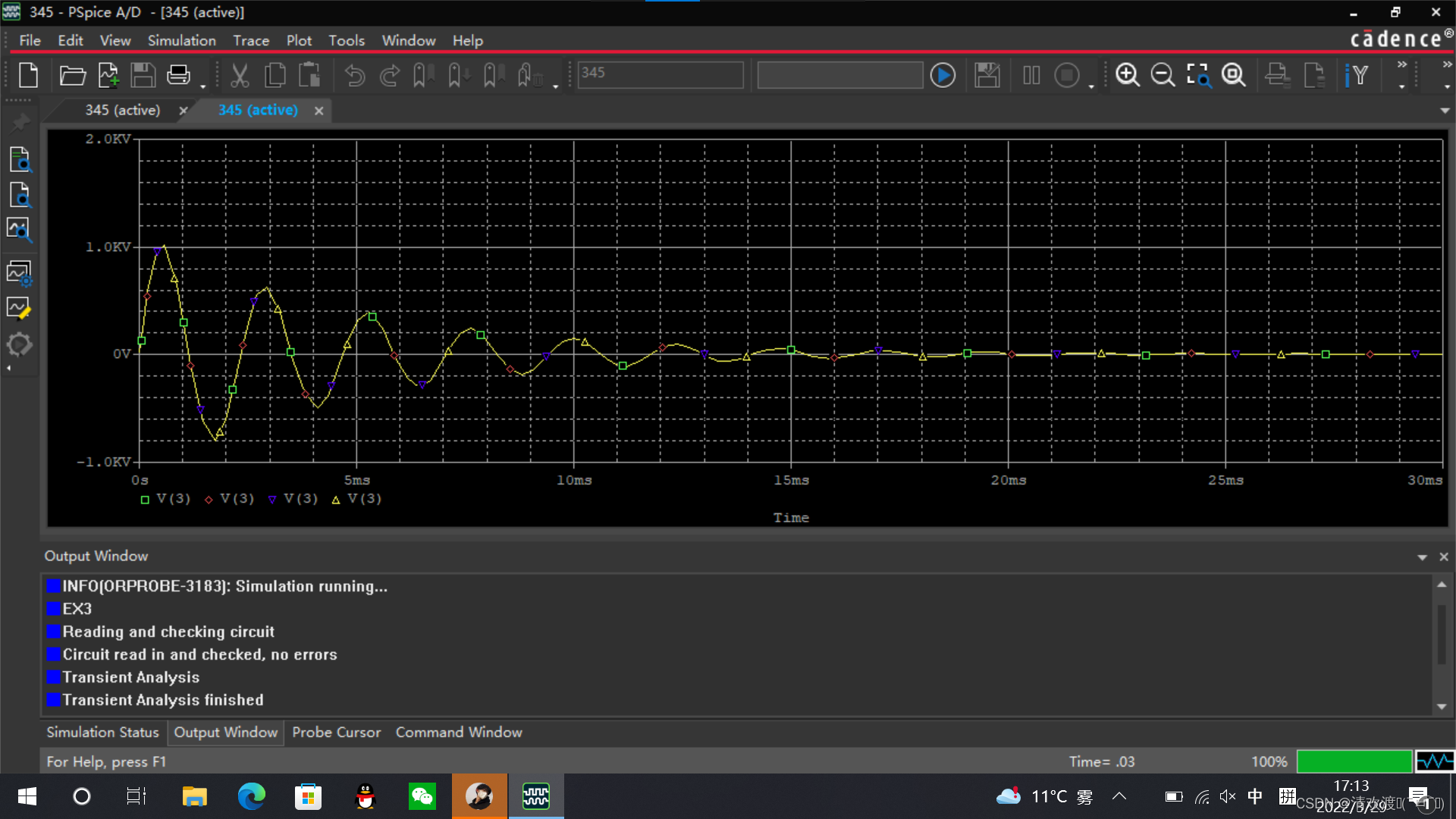

仿真验证

通过Multisim或PSpice搭建仿真电路,测量静态工作点、差模增益和共模增益的频率响应。故意设置元件失配,观察CMRR的变化。更换电流源类型,验证其对CMRR的改善效果。仿真结果与理论分析一致,验证了设计的有效性。

应用场景

差分放大电路在生物电信号采集、精密传感器、高速通信和运算放大器输入级中具有广泛应用。其抑制共模噪声的能力使其成为模拟电路设计的核心组件。