目录

1. T0~T1 120us 能再減少嗎? 最小時間能設置到多少?

4. 如何再GPIO上輸出TX和RX開始執行的瞬間,或者是PA打開和LNA打開這個瞬間狀態通過GPIO輸出

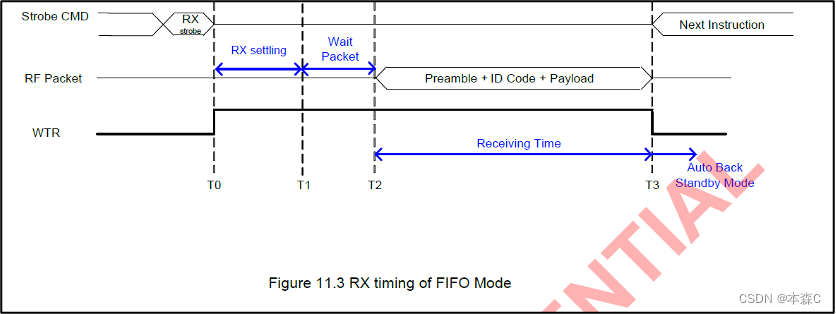

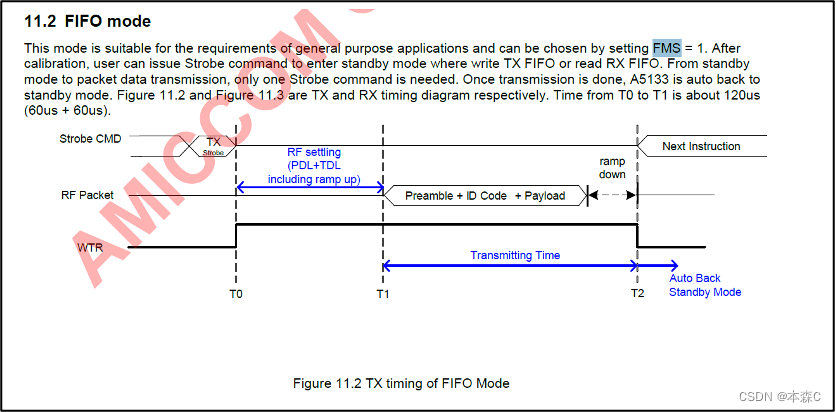

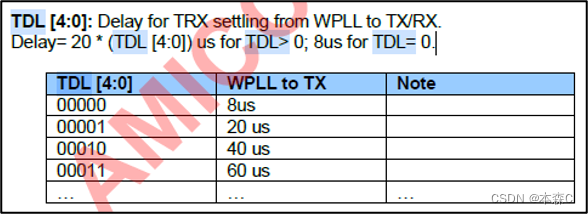

1. T0~T1 120us 能再減少嗎? 最小時間能設置到多少?

可由Delay Register(17h)來設置相應的穩定時間TDL & PDL,如下圖

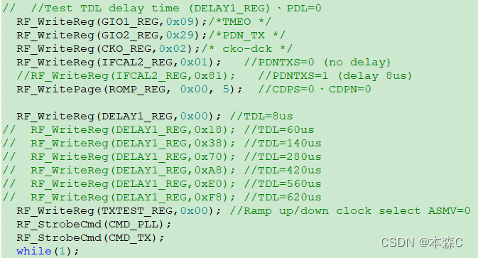

EX: (Sample Code Setting),可參考如下Register配置

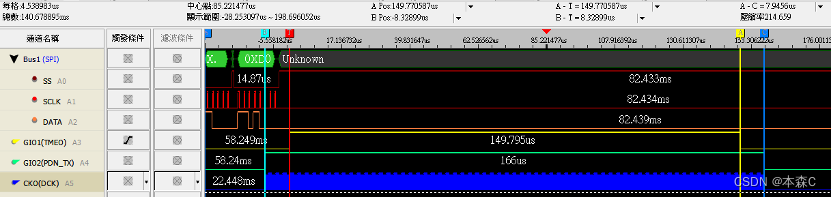

實際LA量測Delay time,得知TDL(ramp up)≒8us、ramp down≒8us

2. PDL 設置成0us, TDL設置成8us, 那上面的PDL+TDL=8us, 就縮短了時間,那ramp up時間是多少?ramp down的時間是多少? PLL是鎖相迴路模式 WPLL是甚麼模式?

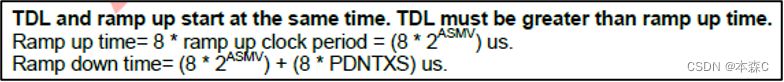

2.1 Ramp up/down 為電壓穩定到發送信號的時間長度設置

由TX Test Register(2Dh)(ASMV)及IF Calibration Register(24h)(PDNTXS)這兩個寄存器來控制delay time

由上述公式即可計算出當前的ramp up/down time,需要注意的是TDL的時間必須比ramp up time的時間長,也就是如果TDL=8us,ramp up time=32us則Total delay為32us,因為兩者是同時開始delay的。(可參考上圖的LA時序圖)

2.2 WPLL則是等待PLL穩定以及準備好進入TX/RX Mode的一個狀態。主要是等待硬體內部自動偵測本地端頻率是否改變。

流程如下:

PLL Mode--->WPLL--->TX/RX Mode

3. 頻率切換或者說跳頻時信道切換時間就是30us?

![]()

是的,Standby Mode到PLL Mode穩定時的時間此部分為硬體設計的固定值

4. 如何再GPIO上輸出TX和RX開始執行的瞬間,或者是PA打開和LNA打開這個瞬間狀態通過GPIO輸出

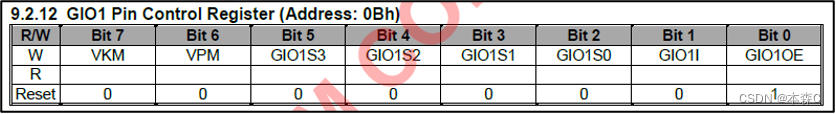

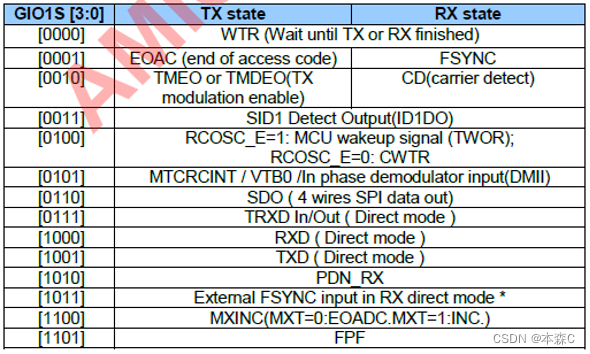

可由GIO1或GIO2 Pin Control Register來設置 WTR 信號。

當下strobe command進入TX/RX時,WTR 信號會輸出高電平,結束傳輸/接收輸出低電平。

本文档详细介绍了射频IC中稳定时间TDL&PDL的设置方法,包括最小时间设置、rampup/rampdown时间计算以及PLL模式介绍。同时,还提供了频率切换时间说明及通过GPIO输出TX/RX状态的方法。

本文档详细介绍了射频IC中稳定时间TDL&PDL的设置方法,包括最小时间设置、rampup/rampdown时间计算以及PLL模式介绍。同时,还提供了频率切换时间说明及通过GPIO输出TX/RX状态的方法。

5047

5047

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?