FPGA:现场可编程逻辑门阵列(Field Programmable Gate Array)

环境:

编译软件:Quartus II 13.1

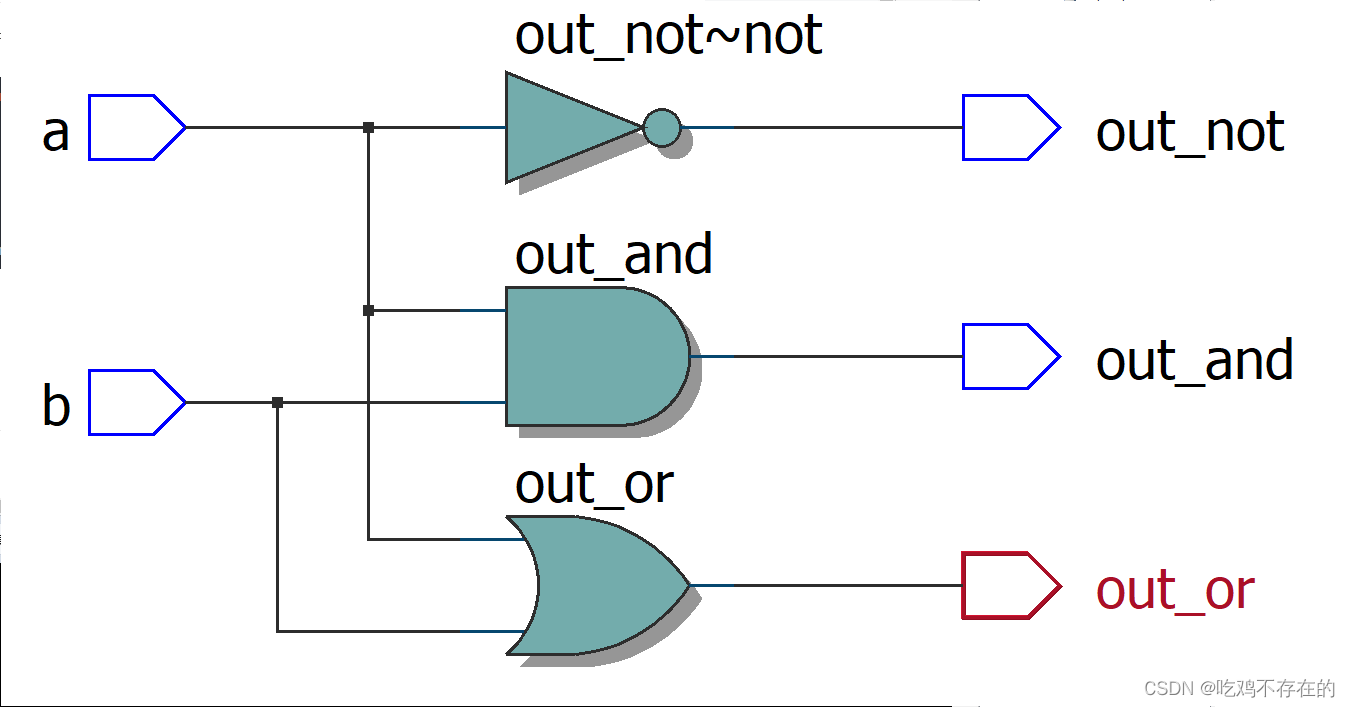

FPGA形成简单的门代码:

module LED ( a,b,out_and,out_or,out_not ); //模块 模块名 (入口参数);

input a,b; //讲输入参数进行定义

output out_and,out_or,out_not;

assign out_not = ~a; //非(not) ~;与(and)&;或(or)|

assign out_and = a&b; //非(not) ~;与(and)&;或(or)|

assign out_or = a|b; //非(not) ~;与(and)&;或(or)|

endmodule //结束这个模块

RTL:

数值判断:

module LED ( equal,a,b );

output equal; //声明输出信号equal

input [1:0] a,b; //声明输入信号a,b

assign equal =(a==b)?1:0 ; //三目运算

//如果a、b 两个输入信号相等,输出为1。否则为0*/

endmodule

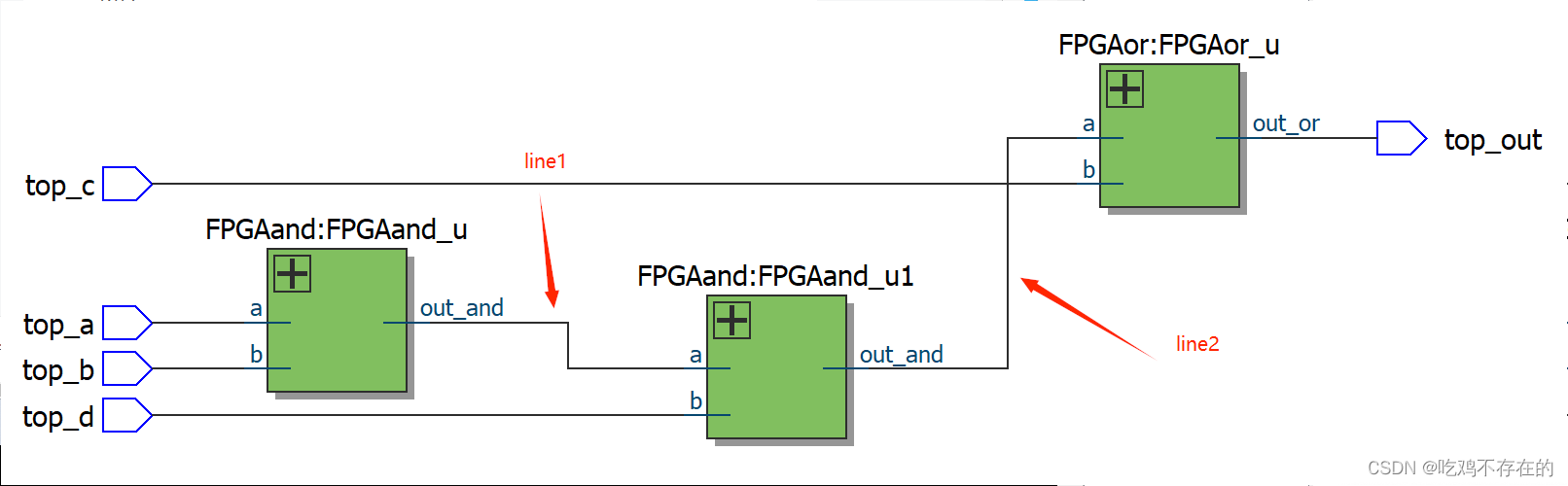

调用多模块

module FPGA_TOP ( top_out,top_a,top_b ,top_c,top_d );

output top_out; //声明输出信号equal

input top_a,top_b,top_c,top_d; //声明输入信号a,b

wire line_1; //创建两个连接线,分别接入第一个模块与第二个模块之间,

wire line_2; //与第二个模块到第三个模块之间。

FPGAand FPGAand_u( //实例化与门

.a(top_a), //与门的入口参数

.b(top_b),

.out_and(line_1) //与门的输出参数

);

FPGAand FPGAand_u1( //实例化第二个与门

.a(line_1), //与门的入口参数

.b(top_d),

.out_and(line_2) //与门的输出参数

);

FPGAor FPGAor_u( //实例化或门

.a(line_2), //或门的入口参数

.b(top_c),

.out_or(top_out) //或门的输出参数

);

endmodule

module FPGAor ( a,b,out_or ); //创建或门模块

input a,b;

output out_or;

assign out_or =a|b;

endmodule

module FPGAand ( a,b,out_and );//创建与门模块

input a,b;

output out_and;

assign out_and =a&b;

endmodule

其RTL:

2952

2952

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?