基于Verlog的IIC协议2-IIC时序和控制器件写入

基于Verlog的IIC协议2-IIC时序和控制器件写入

笔者学到IIC控制eeprom中,发现iic完成一次读必须写一次,根据提供eeprom的iic读写图判断需要满足特定的格式。

举eeprom的格式:

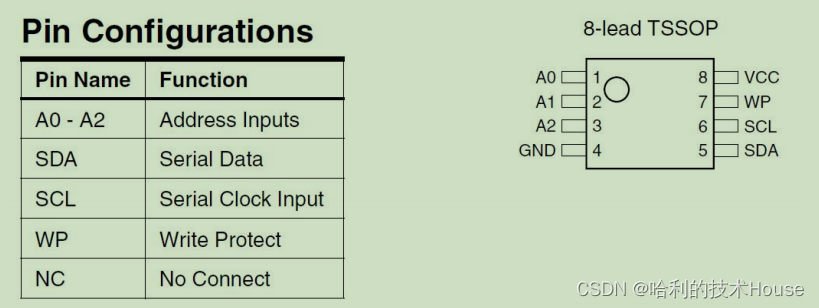

eeprom的器件引脚:

A0-A2:eeprom器件号地址

SDA:输入sda 串行数据(内存地址通过SDA传入,数据通过SDA传入)

SCL:时钟

WP:写保护

NC:不连接

eeprom的写时序

支持单个字节的写,以及多个字节的写

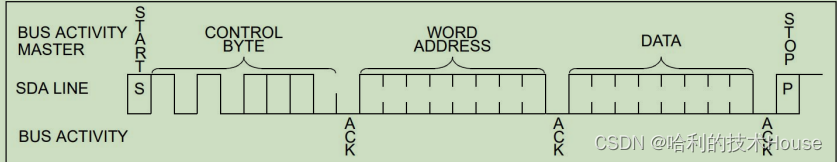

写字节操作 BYTE WRITE

在起始位产生后,先写器件地址,再写芯片内存地址,再写入数据,最后产生停止位,每写一个字节都要产生 ACK 位。

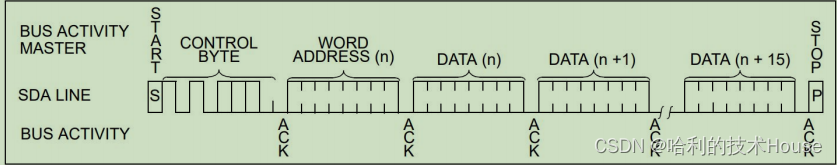

页写 PAGE WRITE

页写和字节写差不多,在字节写的基础上,连续写入数据,最后产生停止位。

eeprom的读时序

支持单个字节的读,以及多个字节的读,三种方式。

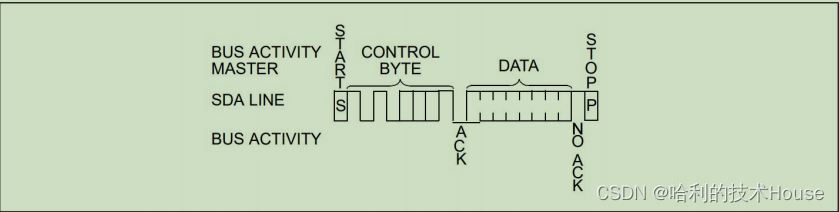

读当前地址 CURRENT ADDRESS READ

只要发送器件地址就能读当前内存地址所指向的地址空间数据,最后的读数据可以不需要发送 ACK,读就需要写一次控制字。(读操作必须要写入控制字)

(内存地址应该是上一次控制传输入的内存地址,如果连续读写进行地址增减)

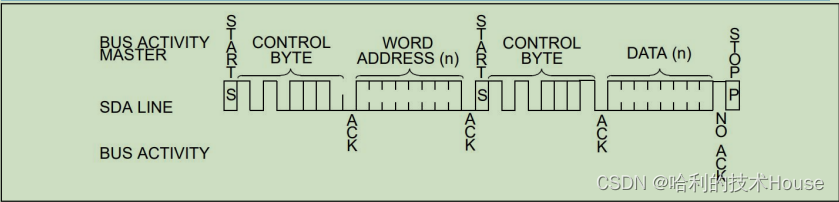

随机读 RANDOM READ

要发送器件地址,然后发送内存地址,之后再发送器件地址并且读取到数据,最后的读数据可以不需要发送 ACK。(读数据必须要写入控制字、内存地址)

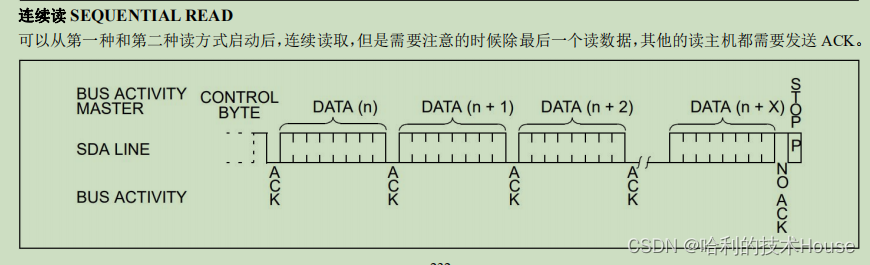

连续读 SEQUENTIAL READ

可以从第一种和第二种读方式启动后,连续读取,但是需要注意的时候除最后一个读数据,其他的读主机都需要发送 ACK。

5431

5431

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?